Full-Custom Ics Standard-Cell-Based

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Section 3. ASIC Industry Trends

3 ASIC INDUSTRY TRENDS ASSPs AND ASICs The term ASIC (Application Specific IC) has been a misnomer from the very beginning. ASICs, as now known in the IC industry, are really customer specific ICs. In other words, the gate array or standard cell device is specifically made for one customer. ASIC, if taken literally, would mean the device was created for one particular type of system (e.g., a disk-drive), even if this device is sold to numerous customers and/or is put in the IC manufacturer’s catalog. Currently, a device type that is sold to more than one user, even if it is produced using ASIC tech- nology, is considered a standard IC or ASSP (Application Specific Standard Product). Thus, we are left with the following nomenclature guidelines (Figure 3-1). ASIC: A device produced for only one customer. PLDs are included as ASICs because the customer “programs” that device for its needs only. CSIC: What ASICs should have been called from the beginning. Some companies differentiate an ASIC from a CSIC by who completes or is responsible for the majority of the IC design effort. If it is the IC producer, the part is labeled a CSIC, if it is the end-user, the device is called an ASIC. This term is not currently used very often in the IC industry. ASSP: A relatively new term for ICs targeting specific types of systems. In many cases the IC will be manufactured using ASIC technology (e.g., gate or linear array or standard cell techniques) but will ultimately be sold as a standard device type to numerous users (i.e., put into a product catolog). -

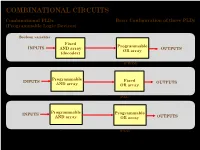

COMBINATIONAL CIRCUITS Combinational Plds Basic Configuration of Three Plds (Programmable Logic Devices)

COMBINATIONAL CIRCUITS Combinational PLDs Basic Configuration of three PLDs (Programmable Logic Devices) Boolean variables Fixed Programmable INPUTS AND array OUTPUTS OR array (decoder) Programmable Read-Only Memory (PROM) Programmable INPUTS Fixed OUTPUTS AND array OR array Programmable Array Logic (PAL) Programmable INPUTS Programmable AND array OR array OUTPUTS (Field) Programmable Logic Array (PLA) 1 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Two-level AND-OR Arrays (Programmable Logic Devices) F (C,B, A) = CBA + CB A A AND B + V B C A C B F C F AND F + V 1 B OR C Multiple functions Simplified equivalent circuit for two-level AND-OR array 2 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) Field-programmable logic elements are devices that contain uncommitted AND/OR arrays that are (programmed) configured by the designer. + V + V A A F (C,B, A) F (C,B, A) = CBA B B C C Unprogrammed AND array Fuse can be "blown" by passing a high current through it. 3 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) F (P1 ,P2 ,P3 ) = P1 + P3 P1 P1 P2 P2 P3 P3 F F (P1 ,P2 ,P3 ) Unprogrammed OR array Programmed OR array P1 P2 P3 P1 + P3 4 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Output Polarity Options (Programmable Logic Devices) I1 Ik Active high Active low Complementary outputs Programmable polarity P P 1 m + V 5 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Bidirectional Pins and Feed back Lines (Programmable Logic Devices) I1 Ik Feedback IOm Three-state driver 6 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs PLA (Programmable Logic Array) (Programmable Logic Devices) If we use ROM to implement the Boolean function we will waste the silicon area. -

GS40 0.11-Μm CMOS Standard Cell/Gate Array

GS40 0.11-µm CMOS Standard Cell/Gate Array Version 1.0 January 29, 2001 Copyright Texas Instruments Incorporated, 2001 The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments. IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this war- ranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WAR- RANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. -

VLSI Design: a New Approach

International Journal of Information Theory Volume 1, Issue 1, 2011, pp-01-04 Available online at: http://www.bioinfo.in/contents.php?id=103 VLSI Design: A New Approach M.B. Swami and V.P. Pawar Department of Physics/Electronics/Computer Science, Maharashtra Udyagiri Mahavidyalaya, Udgir, India e-mail: [email protected] Abstract—This paper presents the different • Cores such as PCI are available and able to Programmable Logic Array is an important building circuit integrate with relative ease Getting started in of VLSI chips and some of the FPGA architectures have FPGA design is easy. evolved from the basic Programmable Logic Array The tools are cheap (and sometimes free) for low- architectures. In this paper the new concepts of Verilog Hardware Description language is included in VLSI Design. end devices and affordable for the high end. Modern Keywords: Programmable Logic Array, FPGA, Verilog. HDL (hardware design language) environments are very powerful for creating and verifying a design. There I. INTRODUCTION is plenty of documentation available for using different vendor’s FPGA design tools and exploiting features of Very-large-scale integration (VLSI) is the process of different FPGAs. creating integrated circuits by combining thousands of Even with modern tools, the fundamentals of transistor-based circuits into a single chip. digital design still remain intact and must be Implementation is based on FPGA design flow with understood. If the fundamentals are ignored, there is a Xilinx tools which will help you to design complex good chance that your design will not work consistently digital systems using HDL and also to get experience of and will probably exhibit intermittent modes of processor and controller implementations on FPGAs. -

Introduction to ASIC Design

’14EC770 : ASIC DESIGN’ An Introduction Application - Specific Integrated Circuit Dr.K.Kalyani AP, ECE, TCE. 1 VLSI COMPANIES IN INDIA • Motorola India – IC design center • Texas Instruments – IC design center in Bangalore • VLSI India – ASIC design and FPGA services • VLSI Software – Design of electronic design automation tools • Microchip Technology – Offers VLSI CMOS semiconductor components for embedded systems • Delsoft – Electronic design automation, digital video technology and VLSI design services • Horizon Semiconductors – ASIC, VLSI and IC design training • Bit Mapper – Design, development & training • Calorex Institute of Technology – Courses in VLSI chip design, DSP and Verilog HDL • ControlNet India – VLSI design, network monitoring products and services • E Infochips – ASIC chip design, embedded systems and software development • EDAIndia – Resource on VLSI design centres and tutorials • Cypress Semiconductor – US semiconductor major Cypress has set up a VLSI development center in Bangalore • VDAT 2000 – Info on VLSI design and test workshops 2 VLSI COMPANIES IN INDIA • Sandeepani – VLSI design training courses • Sanyo LSI Technology – Semiconductor design centre of Sanyo Electronics • Semiconductor Complex – Manufacturer of microelectronics equipment like VLSIs & VLSI based systems & sub systems • Sequence Design – Provider of electronic design automation tools • Trident Techlabs – Power systems analysis software and electrical machine design services • VEDA IIT – Offers courses & training in VLSI design & development • Zensonet Technologies – VLSI IC design firm eg3.com – Useful links for the design engineer • Analog Devices India Product Development Center – Designs DSPs in Bangalore • CG-CoreEl Programmable Solutions – Design services in telecommunications, networking and DSP 3 Physical Design, CAD Tools. • SiCore Systems Pvt. Ltd. 161, Greams Road, ... • Silicon Automation Systems (India) Pvt. Ltd. ( SASI) ... • Tata Elxsi Ltd. -

ECE 274 - Digital Logic Lecture 22 Full-Custom Integrated Circuit

ECE 274 - Digital Logic Lecture 22 Full-Custom Integrated Circuit Full-Custom Integrated Circuit Chip created specifically to implement the transistors of the desired chip Lecture 22 – Implementation Layout – detailed description how each transistor and wires should be Manufactured IC Technologies layed on a chips surface Typically use CAD tools to convert our circuit design to a custom layout Fabricating an IC is often referred to a silicon spin 1 2 Semicustom (Application Specific) Integrated Full-Custom Integrated Circuit Circuits - ASICs Full-Custom Integrated Circuit Gate Arrays Pros Utilize a chip whose transistors are pre-designed to forms rows (arrays) of logic gates on the chip Maximum performance Sometimes referred to as sea-of-gates Cons Pros High NRE (Non-Recurring Engineering) cost Much cheaper than full-custom IC Cost of setting of the fabrication of an IC Fabrications time is typically several weeks Often exceeds $1 million Cons May take months before first IC is available Less optimized compared to full-custom IC - Slower performance, bigger size, and more power consumption 3 4 Semicustom (Application Specific) Integrated Semicustom (Application Specific) Integrated Circuits - ASICs Circuits - ASICs Standard Cells Cell Array Utilize library of pre-layed-out gates and smaller pieces of logic (cells) Standard cells are replaced on the IC with only the wiring left to be that a designer must instantiate and connect with wires completed Pros Sometimes referred to as sea of cells Can be better optimized -

ICS904/EN2 : Design of Digital Integrated Circuits

ICS904/EN2 : Design of Digital Integrated Circuits L5 : Design automation : The "liberty" file format Yves MATHIEU [email protected] Standard Cell characterization "Liberty" files Give all necessary informations to the synthesis and P&R tools A de-facto standard : "Liberty" files from "Synopsys" company. For each cell : • Logic behavior • Area • Power Consumption • Timing But also, for a whole library : • Characterization conditions (Process, Supply Voltage , Temperature) • Characterization conditions (Max rising time, Max capacitances,...) • Statistical capacitance model for wiring... 3/35 ICS904-EN2-L5 Yves MATHIEU An example library Nangate 45nm Open Cell Library Nangate is company creating characterization tools for standard cell libraries. Library distributed by Si2 (Silicon Integration Initiative) an association of electronic design automation companies. No way to process any true circuit, but usable for research and teaching purposes. Based on the NCSU (North Carolina State University) FreePDK45 process kit. FreePDK45 : An open source fictitious, non manufacturable process. 4/35 ICS904-EN2-L5 Yves MATHIEU Nangate 45nm Open Cell Library Units for measurements /* Units Attributes */ voltage_unit : "1V"; current_unit : "1mA"; pulling_resistance_unit : "1kohm"; capacitive_load_unit (1,ff); All measurements use defined units. 6/35 ICS904-EN2-L5 Yves MATHIEU Nangate 45nm Open Cell Library Characterization conditions /* Operation Conditions */ nom_process : 1.00; nom_temperature : 25.00; nom_voltage : 1.10; voltage_map (VDD,1.10); -

The Basics of Logic Design

C APPENDIX The Basics of Logic Design C.1 Introduction C-3 I always loved that C.2 Gates, Truth Tables, and Logic word, Boolean. Equations C-4 C.3 Combinational Logic C-9 Claude Shannon C.4 Using a Hardware Description IEEE Spectrum, April 1992 Language (Shannon’s master’s thesis showed that C-20 the algebra invented by George Boole in C.5 Constructing a Basic Arithmetic Logic the 1800s could represent the workings of Unit C-26 electrical switches.) C.6 Faster Addition: Carry Lookahead C-38 C.7 Clocks C-48 AAppendixC-9780123747501.inddppendixC-9780123747501.indd 2 226/07/116/07/11 66:28:28 PPMM C.8 Memory Elements: Flip-Flops, Latches, and Registers C-50 C.9 Memory Elements: SRAMs and DRAMs C-58 C.10 Finite-State Machines C-67 C.11 Timing Methodologies C-72 C.12 Field Programmable Devices C-78 C.13 Concluding Remarks C-79 C.14 Exercises C-80 C.1 Introduction This appendix provides a brief discussion of the basics of logic design. It does not replace a course in logic design, nor will it enable you to design signifi cant working logic systems. If you have little or no exposure to logic design, however, this appendix will provide suffi cient background to understand all the material in this book. In addition, if you are looking to understand some of the motivation behind how computers are implemented, this material will serve as a useful intro- duction. If your curiosity is aroused but not sated by this appendix, the references at the end provide several additional sources of information. -

RESEARCH INSIGHTS – Hardware Design: FPGA Security Risks

RESEARCH INSIGHTS Hardware Design: FPGA Security Risks www.nccgroup.trust CONTENTS Author 3 Introduction 4 FPGA History 6 FPGA Development 10 FPGA Security Assessment 12 Conclusion 17 Glossary 18 References & Further Reading 19 NCC Group Research Insights 2 All Rights Reserved. © NCC Group 2015 AUTHOR DUNCAN HURWOOD Duncan is a senior consultant at NCC Group, specialising in telecom, embedded systems and application review. He has over 18 years’ experience within the telecom and security industry performing almost every role within the software development cycle from design and development to integration and product release testing. A dedicated security assessor since 2010, his consultancy experience includes multiple technologies, languages and platforms from web and mobile applications, to consumer devices and high-end telecom hardware. NCC Group Research Insights 3 All Rights Reserved. © NCC Group 2015 GLOSSARY AES Advanced encryption standard, a cryptography OTP One time programmable, allowing write once cipher only ASIC Application-specific integrated circuit, non- PCB Printed circuit board programmable hardware logic chip PLA Programmable logic array, forerunner of FPGA Bitfile Binary instruction file used to program FPGAs technology CLB Configurable logic block, an internal part of an PUF Physically unclonable function FPGA POWF Physical one-way function CPLD Complex programmable logic device PSoC Programmable system on chip, an FPGA and EEPROM Electronically erasable programmable read- other hardware on a single chip only memory -

Standard Cell Library Design and Optimization with CDM for Deeply Scaled Finfet Devices

Standard Cell Library Design and Optimization with CDM for Deeply Scaled FinFET Devices. by Ashish Joshi, B.E A Thesis In Electrical Engineering Submitted to the Graduate Faculty of Texas Tech University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCES IN ELECTRICAL ENGINEERING Approved Dr. Tooraj Nikoubin Chair of Committee Dr. Brian Nutter Dr. Stephen Bayne Mark Sheridan Dean of the Graduate School May, 2016 © Ashish Joshi, 2016 Texas Tech University, Ashish Joshi, May 2016 ACKNOWLEDGEMENTS I would like to sincerely thank my supervisor Dr. Nikoubin for providing me the opportunity to pursue my thesis under his guidance. He has been a commendable support and guidance throughout the journey and his thoughtful ideas for problems faced really been the tremendous help. His immense knowledge in VLSI designs constitute the rich source that I have been sampling since the beginning of my research. I am especially indebted to my thesis committee members Dr. Bayne and Dr. Nutter. They have been very gracious and generous with their time, ideas and support. I appreciate Dr. Nutter’s insights in discussing my ideas and depth to which he forces me to think. I would like to thank Texas Instruments and my colleagues Mayank Garg, Jun, Alex, Amber, William, Wenxiao, Shyam, Toshio, Suchi at Texas Instruments for providing me the opportunity to do summer internship with them. I continue to be inspired by their hard work and innovative thinking. I learnt a lot during that tenure and it helped me identifying my field of interest. Internship not only helped me with the technical aspects but also build the confidence to accept the challenges and come up with the innovative solutions. -

Development and Verification of a Small CMOS Digital Standard Cell Library Based on SMIC 130Nm Process

4th International Conference on Mechatronics, Materials, Chemistry and Computer Engineering (ICMMCCE 2015) Development and Verification of A Small CMOS Digital Standard Cell Library Based on SMIC 130nm Process Yiwen Wang1,a,*, Hang Su1,a, Mingjiang Wang1,a, Jipan Huang2,b, Hao Chen2,b 1School of Electronic and Information Engineering, Harbin Institute of Technology Shenzhen Graduate School, Shenzhen, China 2School of Electronic and Computer Engineering, Peking University Shenzhen Graduate School, Shenzhen, China [email protected], [email protected] Keywords: Standard cell library; Full adder; Optimization; Verification; P&R Abstract. Nowadays, Semi-custom design based on the standard cells is the mainstream design method for digital IC chip. In this thesis, the standard cell library is built and verified based on the SMIC 130nm technology, especially the optimization of a 1-bit full adder cell, during which the structure and layout of the full adder in the SMIC library is analyzed. As a result, the structure and size of the adder cell are improved better, which is simulated by H-spice. The comparison shows that the optimized adder is not only smaller in area, with width decreased by 0.82μm, but also have advantages in power consumption and timing, with energy delay product reduced by 7.7% .In the end, the s298 circuit in ISCAS Benchmark89 is used as the benchmark to complete the verification method of the standard cell library. Introduction Standard cell library is the basis of gate-level module based circuit design, and it has a direct impact on the performance[1,2], power consumption, size and yield of the final flowing out circuits. -

Application-Specific Integrated Circuits”, Addison- Wesley, ISBN 0-201-50022-1, 1997

Introduction to Digital Integrated Circuit Design Konstantinos Masselos Department of Electrical & Electronic Engineering Imperial College London URL: http://cas.ee.ic.ac.uk/~kostas E-mail: [email protected] Introduction & Trends Introduction to Digital Integrated Circuit Design Lecture 1 - 1 Aims and Objectives The aim of this course is to introduce the basics of digital integrated circuits design. After following this course you will be able to: • Comprehend the different issues related to the development of digital integrated circuits including fabrication, circuit design, implementation methodologies, testing, design methodologies and tools and future trends. • Use tools covering the back-end design stages of digital integrated circuits. Introduction & Trends Introduction to Digital Integrated Circuit Design Lecture 1 - 2 Course Outline Week Lectures Laboratory/Project 1 Introduction and Trends 2 Basic MOS Theory, SPICE Simulation, CMOS Fabrication Learning Electric & SPICE simulation 3 Inverters and Combinational Logic Learning Layout with Electric 4 Sequential Circuits Switch-level simulation with IRSIM 5 Timing and Interconnect Issues Finishing the previous labs 6 Data Path Circuits Design Project 7 Memory and Array Circuits Design Project 8 Low Power Design Design Project Package, Power and I/O 9 Design for Test Design Project 10 Design Methodologies and Tools Design Project Introduction & Trends Introduction to Digital Integrated Circuit Design Lecture 1 - 3 Recommended Books N. H. E. Weste and D. Harris, “CMOS VLSI Design: A Circuits and Systems Perspective”, 3rd Edition, Addison-Wesley, ISBN 0-321- 14901-7, May 2004. J. Rabaey, A. Chandrakasan, B. Nikolic, “Digital Integrated Circuits: A Design Perspective” 2nd Edition, Prentice Hall, ISBN 0131207644, January 2003.