Introduction to ASIC Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Section 3. ASIC Industry Trends

3 ASIC INDUSTRY TRENDS ASSPs AND ASICs The term ASIC (Application Specific IC) has been a misnomer from the very beginning. ASICs, as now known in the IC industry, are really customer specific ICs. In other words, the gate array or standard cell device is specifically made for one customer. ASIC, if taken literally, would mean the device was created for one particular type of system (e.g., a disk-drive), even if this device is sold to numerous customers and/or is put in the IC manufacturer’s catalog. Currently, a device type that is sold to more than one user, even if it is produced using ASIC tech- nology, is considered a standard IC or ASSP (Application Specific Standard Product). Thus, we are left with the following nomenclature guidelines (Figure 3-1). ASIC: A device produced for only one customer. PLDs are included as ASICs because the customer “programs” that device for its needs only. CSIC: What ASICs should have been called from the beginning. Some companies differentiate an ASIC from a CSIC by who completes or is responsible for the majority of the IC design effort. If it is the IC producer, the part is labeled a CSIC, if it is the end-user, the device is called an ASIC. This term is not currently used very often in the IC industry. ASSP: A relatively new term for ICs targeting specific types of systems. In many cases the IC will be manufactured using ASIC technology (e.g., gate or linear array or standard cell techniques) but will ultimately be sold as a standard device type to numerous users (i.e., put into a product catolog). -

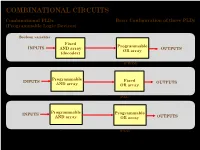

COMBINATIONAL CIRCUITS Combinational Plds Basic Configuration of Three Plds (Programmable Logic Devices)

COMBINATIONAL CIRCUITS Combinational PLDs Basic Configuration of three PLDs (Programmable Logic Devices) Boolean variables Fixed Programmable INPUTS AND array OUTPUTS OR array (decoder) Programmable Read-Only Memory (PROM) Programmable INPUTS Fixed OUTPUTS AND array OR array Programmable Array Logic (PAL) Programmable INPUTS Programmable AND array OR array OUTPUTS (Field) Programmable Logic Array (PLA) 1 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Two-level AND-OR Arrays (Programmable Logic Devices) F (C,B, A) = CBA + CB A A AND B + V B C A C B F C F AND F + V 1 B OR C Multiple functions Simplified equivalent circuit for two-level AND-OR array 2 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) Field-programmable logic elements are devices that contain uncommitted AND/OR arrays that are (programmed) configured by the designer. + V + V A A F (C,B, A) F (C,B, A) = CBA B B C C Unprogrammed AND array Fuse can be "blown" by passing a high current through it. 3 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) F (P1 ,P2 ,P3 ) = P1 + P3 P1 P1 P2 P2 P3 P3 F F (P1 ,P2 ,P3 ) Unprogrammed OR array Programmed OR array P1 P2 P3 P1 + P3 4 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Output Polarity Options (Programmable Logic Devices) I1 Ik Active high Active low Complementary outputs Programmable polarity P P 1 m + V 5 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Bidirectional Pins and Feed back Lines (Programmable Logic Devices) I1 Ik Feedback IOm Three-state driver 6 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs PLA (Programmable Logic Array) (Programmable Logic Devices) If we use ROM to implement the Boolean function we will waste the silicon area. -

GS40 0.11-Μm CMOS Standard Cell/Gate Array

GS40 0.11-µm CMOS Standard Cell/Gate Array Version 1.0 January 29, 2001 Copyright Texas Instruments Incorporated, 2001 The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments. IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this war- ranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WAR- RANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. -

System Design for a Computational-RAM Logic-In-Memory Parailel-Processing Machine

System Design for a Computational-RAM Logic-In-Memory ParaIlel-Processing Machine Peter M. Nyasulu, B .Sc., M.Eng. A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy Ottaw a-Carleton Ins titute for Eleceical and Computer Engineering, Department of Electronics, Faculty of Engineering, Carleton University, Ottawa, Ontario, Canada May, 1999 O Peter M. Nyasulu, 1999 National Library Biôiiothkque nationale du Canada Acquisitions and Acquisitions et Bibliographie Services services bibliographiques 39S Weiiington Street 395. nie WeUingtm OnawaON KlAW Ottawa ON K1A ON4 Canada Canada The author has granted a non- L'auteur a accordé une licence non exclusive licence allowing the exclusive permettant à la National Library of Canada to Bibliothèque nationale du Canada de reproduce, ban, distribute or seU reproduire, prêter, distribuer ou copies of this thesis in microform, vendre des copies de cette thèse sous paper or electronic formats. la forme de microficbe/nlm, de reproduction sur papier ou sur format électronique. The author retains ownership of the L'auteur conserve la propriété du copyright in this thesis. Neither the droit d'auteur qui protège cette thèse. thesis nor substantial extracts fkom it Ni la thèse ni des extraits substantiels may be printed or otherwise de celle-ci ne doivent être imprimés reproduced without the author's ou autrement reproduits sans son permission. autorisation. Abstract Integrating several 1-bit processing elements at the sense amplifiers of a standard RAM improves the performance of massively-paralle1 applications because of the inherent parallelism and high data bandwidth inside the memory chip. -

VLSI Design: a New Approach

International Journal of Information Theory Volume 1, Issue 1, 2011, pp-01-04 Available online at: http://www.bioinfo.in/contents.php?id=103 VLSI Design: A New Approach M.B. Swami and V.P. Pawar Department of Physics/Electronics/Computer Science, Maharashtra Udyagiri Mahavidyalaya, Udgir, India e-mail: [email protected] Abstract—This paper presents the different • Cores such as PCI are available and able to Programmable Logic Array is an important building circuit integrate with relative ease Getting started in of VLSI chips and some of the FPGA architectures have FPGA design is easy. evolved from the basic Programmable Logic Array The tools are cheap (and sometimes free) for low- architectures. In this paper the new concepts of Verilog Hardware Description language is included in VLSI Design. end devices and affordable for the high end. Modern Keywords: Programmable Logic Array, FPGA, Verilog. HDL (hardware design language) environments are very powerful for creating and verifying a design. There I. INTRODUCTION is plenty of documentation available for using different vendor’s FPGA design tools and exploiting features of Very-large-scale integration (VLSI) is the process of different FPGAs. creating integrated circuits by combining thousands of Even with modern tools, the fundamentals of transistor-based circuits into a single chip. digital design still remain intact and must be Implementation is based on FPGA design flow with understood. If the fundamentals are ignored, there is a Xilinx tools which will help you to design complex good chance that your design will not work consistently digital systems using HDL and also to get experience of and will probably exhibit intermittent modes of processor and controller implementations on FPGAs. -

ECE 546 Lecture -20 Power Distribution Networks

ECE 546 Lecture ‐20 Power Distribution Networks Spring 2020 Jose E. Schutt-Aine Electrical & Computer Engineering University of Illinois [email protected] ECE 546 – Jose Schutt‐Aine 1 IC on Package ECE 546 – Jose Schutt‐Aine 2 IC on Package ECE 546 – Jose Schutt‐Aine 3 Power-Supply Noise - Power-supply-level fluctuations - Delta-I noise - Simultaneous switching noise (SSN) - Ground bounce VOH Ideal Actual VOL Vout Vout Time 4 ECE 546 – Jose Schutt‐Aine 4 Voltage Fluctuations • Voltage fluctuations can cause the following Reduction in voltage across power supply terminals. May prevent devices from switching Increase in voltage across power supply terminalsreliability problems Leakage of the voltage fluctuation into transistors Timing errors, power supply noise, delta‐I noise, simultaneous switching noise (SSN) ECE 546 – Jose Schutt‐Aine 5 Power-Supply-Level Fluctuations • Total capacitive load associated with an IC increases as minimum feature size shrinks • Average current needed to charge capacitance increases • Rate of change of current (dI/dt) also increases • Total chip current may change by large amounts within short periods of time • Fluctuation at the power supply level due to self inductance in distribution lines ECE 546 – Jose Schutt‐Aine 6 Reducing Power-Supply-Level Fluctuations Minimize dI/dt noise • Decoupling capacitors • Multiple power & ground pins • Taylored driver turn-on characteristics Decoupling capacitors • Large capacitor charges up during steady state • Assumes role of power supply during current switching • Leads -

Digital Design Flow Techniques and Circuit Design for Thin-Film Transistors

Printed by Tryckeriet i E-huset, Lund 2020 Printed by Tryckeriet SUMAN BALAJI Digital Design Flow Techniques and Circuit Design for Thin-Film Transistors SUMAN BALAJI MASTER´S THESIS Digital Design Flow Techniques and Circuit Design for Thin-Film Transistors for Thin-Film Design and Circuit Flow Design Techniques Digital DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY Series of Master’s theses Department of Electrical and Information Technology LUND 2020 LU/LTH-EIT 2020-770 http://www.eit.lth.se Digital Design Flow Techniques and Circuit Design for Thin-Film Transistors Suman Balaji [email protected] Department of Electrical and Information Technology Lund University Academic Supervisor: Joachim Rodrigues Supervisor: Hikmet Celiker Examiner: Pietro Andreani June 18, 2020 © 2020 Printed in Sweden Tryckeriet i E-huset, Lund Abstract Thin-Film Transistor (TFT) technology refers to process and manufacture tran- sistors, circuits, Integrated circuits (ICs) using thin-film organic or metal-oxide semiconductors on different substrates, such as flexible plastic foils and rigid glass substrates. TFT technology is attractive and used for applications requiring flexible, ultra- thin ICs to enable seamless integration into devices. TFT technology shows great potential to be an enabling technology for Internet of Things (IoT) applications. TFT is currently used and a dominant technology for switching circuits in flat- panel displays and are the main candidates for IoT applications in the near future because of its flexible structure, low cost. It is possible to design different kinds of Application-specific integrated circuits (ASIC) with flexible TFTs. Logic gates are considered as the basic building blocks of a digital circuit. -

The Effects of Globalization on the Fashion Industry– Maísa Benatti

ACKNOLEDGMENTS Thank you my dear parents for raising me in a way that I could travel the world and have experienced different cultures. My main motivation for this dissertation was my curiosity to understand personal and professional connections throughout the world and this curiosity was awakened because of your emotional and financial incentives on letting me live away from home since I was very young. Mae and Ingo, thank you for not measuring efforts for having me in Portugal. I know how hard it was but you´d never said no to anything I needed here. Having you both in my life makes everything so much easier. I love you more than I can ever explain. Pai, your time here in Portugal with me was very important for this masters, thank you so much for showing me that life is not a bed of roses and that I must put a lot of effort on the things to make them happen. I could sew my last collection because of you, your patience and your words saying “if it was easy, it wouldn´t be worth it”. Thank you to my family here in Portugal, Dona Teresinha, Sr. Eurico, Erica, Willian, Felipe, Daniel, Zuleica, Emanuel, Vitória and Artur, for understanding my absences in family gatherings because of the thesis and for always giving me support on anything I need. Dona Teresinha and Sr. Eurico, thank you a million times for helping me so much during this (not easy) year of my life. Thank you for receiving me at your house as if I were your child. -

An Automated Flow for Integrating Hardware IP Into the Automotive Systems Engineering Process

An Automated Flow for Integrating Hardware IP into the Automotive Systems Engineering Process Jan-Hendrik Oetjens Ralph Görgen Joachim Gerlach Wolfgang Nebel Robert Bosch GmbH OFFIS Institute Robert Bosch GmbH Carl v. Ossietzky University AE/EIM3 R&D Division Transportation AE/EIM3 Embedded Hardware-/ Postfach 1342 Escherweg 2 Postfach 1342 Software-Systems 72703 Reutlingen 26121 Oldenburg 72703 Reutlingen 26111 Oldenburg Jan-Hendrik.Oetjens Ralph.Goergen Joachim.Gerlach nebel@informatik. @de.bosch.com @offis.de @de.bosch.com uni-oldenburg.de Abstract during system integration is possible in an earlier stage of the systems engineering process. This contribution shows and discusses the require- Most of the companies’ system development processes ments and constraints that an industrial engineering follow – at least, in their basic principals – the well- process defines for the integration of hardware IP into known V model [1]. In our specific case, there is running the system development flow. It describes the developed an additional boundary through that V model. It partitions strategy for automating the step of making hardware de- the process steps into tasks to be done within our semi- scriptions available in a MATLAB/Simulink based system conductor division and tasks to be done within the corre- modeling and validation environment. It also explains the sponding system divisions (see Figure 1). The prior men- transformation technique on which that strategy is based. tioned acts as a supplier of the hardware parts of the over- An application of the strategy is shown in terms of an all system for the latter. Such boundaries also exist in industrial automotive electronic hardware IP block. -

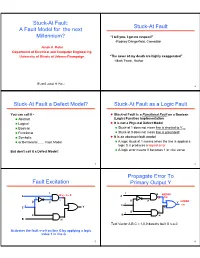

Stuck-At Fault As a Logic Fault

Stuck-At Fault: Stuck-At Fault A Fault Model for the next Millennium? “I tell you, I get no respect!” -Rodney Dangerfield, Comedian Janak H. Patel Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign “The news of my death are highly exaggerated” -Mark Twain, Author © 2005 Janak H. Patel 2 Stuck-At Fault a Defect Model? Stuck-At Fault as a Logic Fault You can call it - z Stuck-at Fault is a Functional Fault on a Boolean Abstract (Logic) Function Implementation Logical z It is not a Physical Defect Model Boolean Stuck-at 1 does not mean line is shorted to VDD Functional Stuck-at 0 does not mean line is grounded! Symbolic z It is an abstract fault model or Behavioral …... Fault Model A logic stuck-at 1 means when the line is applied a logic 0, it produces a logical error But don’t call it a Defect Model! A logic error means 0 becomes 1 or vice versa 3 4 Propagate Error To Fault Excitation Primary Output Y 1 1 G ERROR A G s - a - 0 A 0 1 x X 1/0 D 1 D F ERROR F 0 Y 0 C 1/0 C Y 0 0 0 E E B H B H Test Vector A,B,C = 1,0,0 detects fault G s-a-0 Activates the fault s-a-0 on line G by applying a logic value 1 in line G 5 6 Unmodeled Defect Detection Defect Sites z Internal to a Logic Gate or Cell Other Logic Transistor Defects – Stuck-On, Stuck-Open, Leakage, Shorts between treminals ERROR Defect G ERROR z External to a Gate or Cell Interconnect Defects – Shorts and Opens D 1 F 0 Y ERROR C 0 0 0 E B H G I 7 8 Defects in Physical Cells Fault Modeling z Physical z Electrical Physical Cells such as NAND, NOR, XNOR, AOI, OAI, MUX2, etc. -

ECE 274 - Digital Logic Lecture 22 Full-Custom Integrated Circuit

ECE 274 - Digital Logic Lecture 22 Full-Custom Integrated Circuit Full-Custom Integrated Circuit Chip created specifically to implement the transistors of the desired chip Lecture 22 – Implementation Layout – detailed description how each transistor and wires should be Manufactured IC Technologies layed on a chips surface Typically use CAD tools to convert our circuit design to a custom layout Fabricating an IC is often referred to a silicon spin 1 2 Semicustom (Application Specific) Integrated Full-Custom Integrated Circuit Circuits - ASICs Full-Custom Integrated Circuit Gate Arrays Pros Utilize a chip whose transistors are pre-designed to forms rows (arrays) of logic gates on the chip Maximum performance Sometimes referred to as sea-of-gates Cons Pros High NRE (Non-Recurring Engineering) cost Much cheaper than full-custom IC Cost of setting of the fabrication of an IC Fabrications time is typically several weeks Often exceeds $1 million Cons May take months before first IC is available Less optimized compared to full-custom IC - Slower performance, bigger size, and more power consumption 3 4 Semicustom (Application Specific) Integrated Semicustom (Application Specific) Integrated Circuits - ASICs Circuits - ASICs Standard Cells Cell Array Utilize library of pre-layed-out gates and smaller pieces of logic (cells) Standard cells are replaced on the IC with only the wiring left to be that a designer must instantiate and connect with wires completed Pros Sometimes referred to as sea of cells Can be better optimized -

ICS904/EN2 : Design of Digital Integrated Circuits

ICS904/EN2 : Design of Digital Integrated Circuits L5 : Design automation : The "liberty" file format Yves MATHIEU [email protected] Standard Cell characterization "Liberty" files Give all necessary informations to the synthesis and P&R tools A de-facto standard : "Liberty" files from "Synopsys" company. For each cell : • Logic behavior • Area • Power Consumption • Timing But also, for a whole library : • Characterization conditions (Process, Supply Voltage , Temperature) • Characterization conditions (Max rising time, Max capacitances,...) • Statistical capacitance model for wiring... 3/35 ICS904-EN2-L5 Yves MATHIEU An example library Nangate 45nm Open Cell Library Nangate is company creating characterization tools for standard cell libraries. Library distributed by Si2 (Silicon Integration Initiative) an association of electronic design automation companies. No way to process any true circuit, but usable for research and teaching purposes. Based on the NCSU (North Carolina State University) FreePDK45 process kit. FreePDK45 : An open source fictitious, non manufacturable process. 4/35 ICS904-EN2-L5 Yves MATHIEU Nangate 45nm Open Cell Library Units for measurements /* Units Attributes */ voltage_unit : "1V"; current_unit : "1mA"; pulling_resistance_unit : "1kohm"; capacitive_load_unit (1,ff); All measurements use defined units. 6/35 ICS904-EN2-L5 Yves MATHIEU Nangate 45nm Open Cell Library Characterization conditions /* Operation Conditions */ nom_process : 1.00; nom_temperature : 25.00; nom_voltage : 1.10; voltage_map (VDD,1.10);