The Basics of Logic Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Optimization of Combinational Logic Circuits Based on Compatible Gates

COMPUTER SYSTEMS LABORATORY STANFORD UNIVERSITY STANFORD, CA 94305455 Optimization of Combinational Logic Circuits Based on Compatible Gates Maurizio Damiani Jerry Chih-Yuan Yang Giovanni De Micheli Technical Report: CSL-TR-93-584 September 1993 This research is sponsored by NSF and DEC under a PYI award and by ARPA and NSF under contract MIP 9115432. Optimization of Combinational Logic Circuits Based on Compatible Gates Maurizio Damiani * Jerry Chih- Yuan Yang Giovanni De Micheli Technical Report: CSL-TR-93-584 September, 1993 Computer Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University, Stanford CA 94305-4055 Abstract This paper presents a set of new techniques for the optimization of multiple-level combinational Boolean networks. We describe first a technique based upon the selection of appropriate multiple- output subnetworks (consisting of so-called compatible gates) whose local functions can be op- timized simultaneously. We then generalize the method to larger and more arbitrary subsets of gates. Because simultaneous optimization of local functions can take place, our methods are more powerful and general than Boolean optimization methods using don’t cares , where only single-gate optimization can be performed. In addition, our methods represent a more efficient alternative to optimization procedures based on Boolean relations because the problem can be modeled by a unate covering problem instead of the more difficult binate covering problem. The method is implemented in program ACHILLES and compares favorably to SIS. Key Words and Phrases: Combinational logic synthesis, don’t care methods. *Now with the Dipartimento di Elettronica ed Informatica, UniversitB di Padova, Via Gradenigo 6/A, Padova, Italy. -

Chapter 3: Combinational Logic Design

Chapter 3: Combinational Logic Design 1 Introduction • We have learned all the prerequisite material: – Truth tables and Boolean expressions describe functions – Expressions can be converted into hardware circuits – Boolean algebra and K-maps help simplify expressions and circuits • Now, let us put all of these foundations to good use, to analyze and design some larger circuits 2 Introduction • Logic circuits for digital systems may be – Combinational – Sequential • A combinational circuit consists of logic gates whose outputs at any time are determined by the current input values, i.e., it has no memory elements • A sequential circuit consists of logic gates whose outputs at any time are determined by the current input values as well as the past input values, i.e., it has memory elements 3 Introduction • Each input and output variable is a binary variable • 2^n possible binary input combinations • One possible binary value at the output for each input combination • A truth table or m Boolean functions can be used to specify input-output relation 4 Design Hierarchy • A single very large-scale integrated (VLSI) processos circuit contains several tens of millions of gates! • Imagine interconnecting these gates to form the processor • No complex circuit can be designed simply by interconnecting gates one at a time • Divide and Conquer approach is used to deal with the complexity – Break up the circuit into pieces (blocks) – Define the functions and the interfaces of each block such that the circuit formed by interconnecting the blocks obeys the original circuit specification – If a block is still too large and complex to be designed as a single entity, it can be broken into smaller blocks 5 Divide and Conquer 6 Hierarchical Design due to Divide and Conquer 7 Hierarchical Design • A hierarchy reduce the complexity required to represent the schematic diagram of a circuit • In any hierarchy, the leaves consist of predefined blocks, some of which may be primitives. -

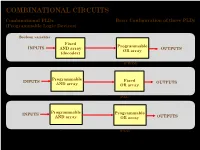

COMBINATIONAL CIRCUITS Combinational Plds Basic Configuration of Three Plds (Programmable Logic Devices)

COMBINATIONAL CIRCUITS Combinational PLDs Basic Configuration of three PLDs (Programmable Logic Devices) Boolean variables Fixed Programmable INPUTS AND array OUTPUTS OR array (decoder) Programmable Read-Only Memory (PROM) Programmable INPUTS Fixed OUTPUTS AND array OR array Programmable Array Logic (PAL) Programmable INPUTS Programmable AND array OR array OUTPUTS (Field) Programmable Logic Array (PLA) 1 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Two-level AND-OR Arrays (Programmable Logic Devices) F (C,B, A) = CBA + CB A A AND B + V B C A C B F C F AND F + V 1 B OR C Multiple functions Simplified equivalent circuit for two-level AND-OR array 2 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) Field-programmable logic elements are devices that contain uncommitted AND/OR arrays that are (programmed) configured by the designer. + V + V A A F (C,B, A) F (C,B, A) = CBA B B C C Unprogrammed AND array Fuse can be "blown" by passing a high current through it. 3 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) F (P1 ,P2 ,P3 ) = P1 + P3 P1 P1 P2 P2 P3 P3 F F (P1 ,P2 ,P3 ) Unprogrammed OR array Programmed OR array P1 P2 P3 P1 + P3 4 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Output Polarity Options (Programmable Logic Devices) I1 Ik Active high Active low Complementary outputs Programmable polarity P P 1 m + V 5 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Bidirectional Pins and Feed back Lines (Programmable Logic Devices) I1 Ik Feedback IOm Three-state driver 6 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs PLA (Programmable Logic Array) (Programmable Logic Devices) If we use ROM to implement the Boolean function we will waste the silicon area. -

Logic Optimization and Synthesis: Trends and Directions in Industry

Logic Optimization and Synthesis: Trends and Directions in Industry Luca Amaru´∗, Patrick Vuillod†, Jiong Luo∗, Janet Olson∗ ∗ Synopsys Inc., Design Group, Sunnyvale, California, USA † Synopsys Inc., Design Group, Grenoble, France Abstract—Logic synthesis is a key design step which optimizes of specific logic styles and cell layouts. Embedding as much abstract circuit representations and links them to technology. technology information as possible early in the logic optimiza- With CMOS technology moving into the deep nanometer regime, tion engine is key to make advantageous logic restructuring logic synthesis needs to be aware of physical informations early in the flow. With the rise of enhanced functionality nanodevices, opportunities carry over at the end of the design flow. research on technology needs the help of logic synthesis to capture In this paper, we examine the synergy between logic synthe- advantageous design opportunities. This paper deals with the syn- sis and technology, from an industrial perspective. We present ergy between logic synthesis and technology, from an industrial technology aware synthesis methods incorporating advanced perspective. First, we present new synthesis techniques which physical information at the core optimization engine. Internal embed detailed physical informations at the core optimization engine. Experiments show improved Quality of Results (QoR) and results evidence faster timing closure and better correlation better correlation between RTL synthesis and physical implemen- between RTL synthesis and physical implementation. We elab- tation. Second, we discuss the application of these new synthesis orate on synthesis aware technology development, where logic techniques in the early assessment of emerging nanodevices with synthesis enables a fair system-level assessment on emerging enhanced functionality. -

Combinational Logic; Hierarchical Design and Analysis

Combinational Logic; Hierarchical Design and Analysis Tom Kelliher, CS 240 Feb. 10, 2012 1 Administrivia Announcements Collect assignment. Assignment Read 3.3. From Last Time IC technology. Outline 1. Combinational logic. 2. Hierarchical design 3. Design analysis. 1 Coming Up Design example. 2 Combinational Logic 1. Definition: Logic circuits in which the output(s) depend solely upon current inputs. 2. No feedback or memory. 3. Sequential circuits: outputs depend upon current inputs and previous inputs. Memory or registers. 4. Example — BCD to 7-segment decoder: S0 D0 S1 D1 BCD - 7 Seg S2 D2 S3 D3 Decoder S4 S5 S6 3 Hierarchical Design 1. Transistor counts: 2 Processor Year Transistor Count TI SN7400 1966 16 Intel 4004 1971 2,300 Intel 8085 1976 6,500 Intel 8088 1979 29,000 Intel 80386 1985 275,000 Intel Pentium 1993 3,100,000 Intel Pentium 4 2000 42,000,000 AMD Athlon 64 2003 105,900,000 Intel Core 2 Duo 2006 291,000,000 Intel Core 2 Quad 2006 582,000,000 NVIDIA G80 2006 681,000,000 Intel Dual Core Itanium 2 2006 1,700,000,000 Intel Atom 2008 42,000,000 Six Core Xeon 7400 2008 1,900,000,000 AMD RV770 2008 956,000,000 NVIDIA GT200 2008 1,400,000,000 Eight Core Xeon Nehalem-EX 2010 2,300,000,000 10 Core Xeon Westmere-EX 2011 2,600,000,000 AMD Cayman 2010 2,640,000,000 NVIDIA GF100 2010 3,000,000,000 Altera Stratix V 2011 3,800,000,000 2. Design and conquer: CPU ⇒ Integer Unit ⇒ Adder ⇒ binary full adder ⇒ NAND gates 3. -

VLSI Design: a New Approach

International Journal of Information Theory Volume 1, Issue 1, 2011, pp-01-04 Available online at: http://www.bioinfo.in/contents.php?id=103 VLSI Design: A New Approach M.B. Swami and V.P. Pawar Department of Physics/Electronics/Computer Science, Maharashtra Udyagiri Mahavidyalaya, Udgir, India e-mail: [email protected] Abstract—This paper presents the different • Cores such as PCI are available and able to Programmable Logic Array is an important building circuit integrate with relative ease Getting started in of VLSI chips and some of the FPGA architectures have FPGA design is easy. evolved from the basic Programmable Logic Array The tools are cheap (and sometimes free) for low- architectures. In this paper the new concepts of Verilog Hardware Description language is included in VLSI Design. end devices and affordable for the high end. Modern Keywords: Programmable Logic Array, FPGA, Verilog. HDL (hardware design language) environments are very powerful for creating and verifying a design. There I. INTRODUCTION is plenty of documentation available for using different vendor’s FPGA design tools and exploiting features of Very-large-scale integration (VLSI) is the process of different FPGAs. creating integrated circuits by combining thousands of Even with modern tools, the fundamentals of transistor-based circuits into a single chip. digital design still remain intact and must be Implementation is based on FPGA design flow with understood. If the fundamentals are ignored, there is a Xilinx tools which will help you to design complex good chance that your design will not work consistently digital systems using HDL and also to get experience of and will probably exhibit intermittent modes of processor and controller implementations on FPGAs. -

Introduction to ASIC Design

’14EC770 : ASIC DESIGN’ An Introduction Application - Specific Integrated Circuit Dr.K.Kalyani AP, ECE, TCE. 1 VLSI COMPANIES IN INDIA • Motorola India – IC design center • Texas Instruments – IC design center in Bangalore • VLSI India – ASIC design and FPGA services • VLSI Software – Design of electronic design automation tools • Microchip Technology – Offers VLSI CMOS semiconductor components for embedded systems • Delsoft – Electronic design automation, digital video technology and VLSI design services • Horizon Semiconductors – ASIC, VLSI and IC design training • Bit Mapper – Design, development & training • Calorex Institute of Technology – Courses in VLSI chip design, DSP and Verilog HDL • ControlNet India – VLSI design, network monitoring products and services • E Infochips – ASIC chip design, embedded systems and software development • EDAIndia – Resource on VLSI design centres and tutorials • Cypress Semiconductor – US semiconductor major Cypress has set up a VLSI development center in Bangalore • VDAT 2000 – Info on VLSI design and test workshops 2 VLSI COMPANIES IN INDIA • Sandeepani – VLSI design training courses • Sanyo LSI Technology – Semiconductor design centre of Sanyo Electronics • Semiconductor Complex – Manufacturer of microelectronics equipment like VLSIs & VLSI based systems & sub systems • Sequence Design – Provider of electronic design automation tools • Trident Techlabs – Power systems analysis software and electrical machine design services • VEDA IIT – Offers courses & training in VLSI design & development • Zensonet Technologies – VLSI IC design firm eg3.com – Useful links for the design engineer • Analog Devices India Product Development Center – Designs DSPs in Bangalore • CG-CoreEl Programmable Solutions – Design services in telecommunications, networking and DSP 3 Physical Design, CAD Tools. • SiCore Systems Pvt. Ltd. 161, Greams Road, ... • Silicon Automation Systems (India) Pvt. Ltd. ( SASI) ... • Tata Elxsi Ltd. -

Basic Boolean Algebra and Logic Optimization

Fundamental Algorithms for System Modeling, Analysis, and Optimization Edward A. Lee, Jaijeet Roychowdhury, Sanjit A. Seshia UC Berkeley EECS 144/244 Fall 2011 Copyright © 2010-11, E. A. Lee, J. Roychowdhury, S. A. Seshia, All rights reserved Lec 3: Boolean Algebra and Logic Optimization - 1 Thanks to S. Devadas, K. Keutzer, S. Malik, R. Rutenbar for several slides RTL Synthesis Flow FSM, HDL Verilog, HDL Simulation/ VHDL Verification RTL Synthesis a 0 d q Boolean circuit/network 1 netlist b Library/ s clk module logic generators optimization a 0 d q Boolean circuit/network netlist b 1 s clk physical design Graph / Rectangles layout K. Keutzer EECS 144/244, UC Berkeley: 2 Reduce Sequential Ckt Optimization to Combinational Optimization B Flip-flops inputs Combinational outputs Logic Optimize the size/delay/etc. of the combinational circuit (viewed as a Boolean network) EECS 144/244, UC Berkeley: 3 Logic Optimization 2-level Logic opt netlist tech multilevel independent Logic opt logic Library optimization tech dependent Generic Library netlist Real Library EECS 144/244, UC Berkeley: 4 Outline of Topics Basics of Boolean algebra Two-level logic optimization Multi-level logic optimization Boolean function representation: BDDs EECS 144/244, UC Berkeley: 5 Definitions – 1: What is a Boolean function? EECS 144/244, UC Berkeley: 6 Definitions – 1: What is a Boolean function? Let B = {0, 1} and Y = {0, 1} Input variables: X1, X2 …Xn Output variables: Y1, Y2 …Ym A logic function ff (or ‘Boolean’ function, switching function) in n inputs and m -

Combinational Logic

MEC520 디지털 공학 Combinational Logic Jee-Hwan Ryu School of Mechanical Engineering Korea University of Technology and Education Combinational circuits Outputs are determined from the present inputs Consist of input/output variables and logic gates Binary signal to registers Binary signal from registers Sequential Circuits Outputs are determined from the present inputs and the state of the storage elements The state of the storage elements is a function of previous inputs Depends on present and past inputs Korea University of Technology and Education Analysis procedure To determine the function from a given circuit diagram Analysis procedure Make sure the circuit is combinational or sequential No Feedback and memory elements Obtain the output Boolean functions or the truth table Korea University of Technology and Education Obtain Procedure-Boolean Function Boolean function from a logic diagram Label all gate outputs with arbitrary symbols Make output functions at each level Substitute final outputs to input variables Korea University of Technology and Education Obtain Procedure-Truth Table Truth table from a logic diagram Put the input variables to binary numbers Determine the output value at each gate Obtain truth table Korea University of Technology and Education Example Korea University of Technology and Education Design Procedure Procedure to design a combinational circuit 1. Determine the required number of input and output from specification 2. Assign a symbol to each input/output 3. Derive the truth table from the -

RESEARCH INSIGHTS – Hardware Design: FPGA Security Risks

RESEARCH INSIGHTS Hardware Design: FPGA Security Risks www.nccgroup.trust CONTENTS Author 3 Introduction 4 FPGA History 6 FPGA Development 10 FPGA Security Assessment 12 Conclusion 17 Glossary 18 References & Further Reading 19 NCC Group Research Insights 2 All Rights Reserved. © NCC Group 2015 AUTHOR DUNCAN HURWOOD Duncan is a senior consultant at NCC Group, specialising in telecom, embedded systems and application review. He has over 18 years’ experience within the telecom and security industry performing almost every role within the software development cycle from design and development to integration and product release testing. A dedicated security assessor since 2010, his consultancy experience includes multiple technologies, languages and platforms from web and mobile applications, to consumer devices and high-end telecom hardware. NCC Group Research Insights 3 All Rights Reserved. © NCC Group 2015 GLOSSARY AES Advanced encryption standard, a cryptography OTP One time programmable, allowing write once cipher only ASIC Application-specific integrated circuit, non- PCB Printed circuit board programmable hardware logic chip PLA Programmable logic array, forerunner of FPGA Bitfile Binary instruction file used to program FPGAs technology CLB Configurable logic block, an internal part of an PUF Physically unclonable function FPGA POWF Physical one-way function CPLD Complex programmable logic device PSoC Programmable system on chip, an FPGA and EEPROM Electronically erasable programmable read- other hardware on a single chip only memory -

Gate Logic Logic Optimization Overview

Lecture 5: Gate Logic Logic Optimization MAH, AEN EE271 Lecture 5 1 Overview Reading McCluskey, Logic Design Principles- or any text in boolean algebra Introduction We could design at the level of irsim - Think about transistors as switches - Build collections of switches that do useful stuff - Don’t much care whether the collection of transistors is a gate, switch logic, or some combination. It is a collection of switches. But this is pretty complicated - Switches are bidirectional, charge-sharing, - Need to worry about series resistance… MAH, AEN EE271 Lecture 5 2 Logic Gates Constrain the problem to simplify it. • Constrain how one can connect transistors - Create a collection of transistors where the Output is always driven by a switch-network to a supply (not an input) And the inputs to this unit only connect the gate of the transistors • Model this collection of transistors by a simpler abstraction Units are unidirectional Function is modelled by boolean operations Capacitance only affects speed and not functionality Delay through network is sum of delays of elements This abstract model is one we have used already. • It is a logic gate MAH, AEN EE271 Lecture 5 3 Logic Gates Come in various forms and sizes In CMOS, all of the primitive gates1 have one inversion from each input to the output. There are many versions of primitive gates. Different libraries have different collections. In general, most libraries have all 3 input gates (NAND, NOR, AOI, and OAI gates) and some 4 input gates. Most libraries are much richer, and have a large number of gates. -

Chapter 6 - Combinational Logic Systems GCSE Electronics – Component 1: Discovering Electronics

Chapter 6 - Combinational logic systems GCSE Electronics – Component 1: Discovering Electronics Combinational logic systems Learners should be able to: (a) recognise 1/0 as two-state logic levels (b) identify and use NOT gates and 2-input AND, OR, NAND and NOR gates, singly and in combination (c) produce a suitable truth table from a given system specification and for a given logic circuit (d) use truth tables to analyse a system of gates (e) use Boolean algebra to represent the output of truth tables or logic gates and use the basic Boolean identities A.B = A+B and A+B = A.B (f) design processing systems consisting of logic gates to solve problems (g) simplify logic circuits using NAND gate redundancy (h) analyse and design systems from a given truth table to solve a given problem (i) use data sheets to select a logic IC for given applications and to identify pin connections (j) design and use switches and pull-up or pull-down resistors to provide correct logic level/edge-triggered signals for logic gates and timing circuits 180 © WJEC 2017 Chapter 6 - Combinational logic systems GCSE Electronics – Component 1: Discovering Electronics Introduction In this chapter we will be concentrating on the basics of digital logic circuits which will then be extended in Component 2. We should start by ensuring that you understand the difference between a digital signal and an analogue signal. An analogue signal Voltage (V) Max This is a signal that can have any value between the zero and maximum of the power supply. Changes between values can occur slowly or rapidly depending on the system involved.