Lecture20-(140624)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

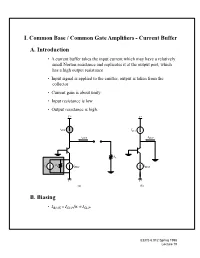

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Lecture 19 Common-Gate Stage

4/7/2008 Lecture 19 OUTLINE • Common‐gate stage • Source follower • Reading: Chap. 7.3‐7.4 EE105 Spring 2008 Lecture 19, Slide 1Prof. Wu, UC Berkeley Common‐Gate Stage AvmD= gR • Common‐gate stage is similar to common‐base stage: a rise in input causes a rise in output. So the gain is positive. EE105 Spring 2008 Lecture 19, Slide 2Prof. Wu, UC Berkeley EE105 Fall 2007 1 4/7/2008 Signal Levels in CG Stage • In order to maintain M1 in saturation, the signal swing at Vout cannot fall below Vb‐VTH EE105 Spring 2008 Lecture 19, Slide 3Prof. Wu, UC Berkeley I/O Impedances of CG Stage 1 R = in λ =0 RRout= D gm • The input and output impedances of CG stage are similar to those of CB stage. EE105 Spring 2008 Lecture 19, Slide 4Prof. Wu, UC Berkeley EE105 Fall 2007 2 4/7/2008 CG Stage with Source Resistance 1 g vv= m Xin1 + RS gm 1 vv g AgR==out x m vmD1 vvxin + RS gm R gR ==D mD 1 1+ gRmS + RS gm • When a source resistance is present, the voltage gain is equal to that of a CS stage with degeneration, only positive. EE105 Spring 2008 Lecture 19, Slide 5Prof. Wu, UC Berkeley Generalized CG Behavior Rgout= (1++g mrR O) S r O • When a gate resistance is present it does not affect the gain and I/O impedances since there is no potential drop across it (at low frequencies). • The output impedance of a CG stage with source resistance is identical to that of CS stage with degeneration. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Tabulation of Published Data on Electron Devices of the U.S.S.R. Through December 1976

NAT'L INST. OF STAND ms & TECH R.I.C. Pubii - cations A111D4 4 Tfi 3 4 4 NBSIR 78-1564 Tabulation of Published Data on Electron Devices of the U.S.S.R. Through December 1976 Charles P. Marsden Electron Devices Division Center for Electronics and Electrical Engineering National Bureau of Standards Washington, DC 20234 December 1978 Final QC— U.S. DEPARTMENT OF COMMERCE 100 NATIONAL BUREAU OF STANDARDS U56 73-1564 Buraev of Standard! NBSIR 78-1564 1 4 ^79 fyr *'• 1 f TABULATION OF PUBLISHED DATA ON ELECTRON DEVICES OF THE U.S.S.R. THROUGH DECEMBER 1976 Charles P. Marsden Electron Devices Division Center for Electronics and Electrical Engineering National Bureau of Standards Washington, DC 20234 December 1978 Final U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary / Dr. Sidney Harman, Under Secretary Jordan J. Baruch, Assistant Secretary for Science and Technology NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Director - 1 TABLE OF CONTENTS Page Preface i v 1. Introduction 2. Description of the Tabulation ^ 1 3. Organization of the Tabulation ’ [[ ] in ’ 4. Terminology Used the Tabulation 3 5. Groups: I. Numerical 7 II. Receiving Tubes 42 III . Power Tubes 49 IV. Rectifier Tubes 53 IV-A. Mechanotrons , Two-Anode Diode 54 V. Voltage Regulator Tubes 55 VI. Current Regulator Tubes 55 VII. Thyratrons 56 VIII. Cathode Ray Tubes 58 VIII-A. Vidicons 61 IX. Microwave Tubes 62 X. Transistors 64 X-A-l . Integrated Circuits 75 X-A-2. Integrated Circuits (Computer) 80 X-A-3. Integrated Circuits (Driver) 39 X-A-4. Integrated Circuits (Linear) 89 X- B. -

Common Gate Amplifier

© 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company COMMON GATE AMPLIFIER • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Common Gate Amplifier A common-gate amplifier is one of three basic single-stage field-effect transistor (FET) amplifier topologies, typically used as a current buffer or voltage amplifier. In the circuit the source terminal of the transistor serves as the input, the drain is the output and the gate is connected to ground, or common, hence its name. The analogous bipolar junction transistor circuit is the common-base amplifier. Input signal is applied to the source, output is taken from the drain. current gain is about unity, input resistance is low, output resistance is high a CG stage is a current buffer. It takes a current at the input that may have a relatively small Norton equivalent resistance and replicates it at the output port, which is a good current source due to the high output resistance. • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Circuit Topology • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Waveforms Input Voltage Output Voltage • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company The common-source and common-drain configurations have extremely high input resistances because the gate is the input terminal. In contrast, the common-gate configuration where the source is the input terminal has a low input resistance. Common gate FET configuration provides a low input impedance while offering a high output impedance. -

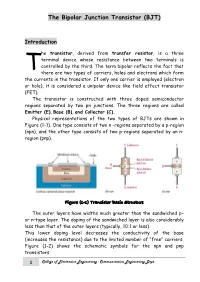

The Bipolar Junction Transistor (BJT)

The Bipolar Junction Transistor (BJT) Introduction he transistor, derived from transfer resistor, is a three terminal device whose resistance between two terminals is controlled by the third. The term bipolar reflects the fact that T there are two types of carriers, holes and electrons which form the currents in the transistor. If only one carrier is employed (electron or hole), it is considered a unipolar device like field effect transistor (FET). The transistor is constructed with three doped semiconductor regions separated by two pn junctions. The three regions are called Emitter (E), Base (B), and Collector (C). Physical representations of the two types of BJTs are shown in Figure (1–1). One type consists of two n -regions separated by a p-region (npn), and the other type consists of two p-regions separated by an n- region (pnp). Figure (1-1) Transistor Basic Structure The outer layers have widths much greater than the sandwiched p– or n–type layer. The doping of the sandwiched layer is also considerably less than that of the outer layers (typically, 10:1 or less). This lower doping level decreases the conductivity of the base (increases the resistance) due to the limited number of “free” carriers. Figure (1-2) shows the schematic symbols for the npn and pnp transistors 1 College of Electronics Engineering - Communication Engineering Dept. Figure (1-2) standard transistor symbol Transistor operation Objective: understanding the basic operation of the transistor and its naming In order for the transistor to operate properly as an amplifier, the two pn junctions must be correctly biased with external voltages. -

Lecture 20 Transistor Amplifiers (II) Other Amplifier Stages

Lecture 20 Transistor Amplifiers (II) Other Amplifier Stages Outline • Common-drain amplifier • Common-gate amplifier Reading Assignment: Howe and Sodini; Chapter 8, Sections 8.7-8.9 6.012 Spring 2007 1 1. Common-drain amplifier VDD signal source RS signal vs + load iSUP RL vOUT VBIAS - VSS • A voltage buffer takes the input voltage which may have a relatively large Thevenin resistance and replicates the voltage at the output port, which has a low output resistance • Input signal is applied to the gate • Output is taken from the source • To first order, voltage gain ≈ 1 • Input resistance is high • Output resistance is low – Effective voltage buffer stage How does it work? •vgate ↑⇒ iD cannot change ⇒ vsource ↑ – Source follower 6.012 Spring 2007 2 Biasing the Common-drain amplifier VDD signal source RS VSS signal + load vs iSUP RL vOUT VBIAS - VSS • Assume device in saturation; neglect RS and RL; neglect CLM (λ = 0) • Obtain desired output bias voltage – Typically set VOUT to”halfway” between VSS and VDD. • Output voltage maximum VDD-VDSsat • Output voltage minimum set by voltage requirement across ISUP. VBIAS = VGS + VOUT I V = V (V ) + SUP GS Tn SB W µ C 2L n ox 6.012 Spring 2007 3 Small-signal Analysis Unloaded small-signal equivalent circuit model: D G + gmvgs ro S vin + roc vout - - + vgs - + + vin gmvgs ro//roc vout - - vin = vgs + vout vout = gmvgs(ro // roc ) Then: g A m 1 vo = 1 ≈ gm + ro // roc 6.012 Spring 2007 4 Input and Output Resistance Input Impedance : Rin = ∞ Output Impedance: i + v - t + gs + RS vin gmvgs ro//roc vt -

Common Gate Amplifier Is Often Used As a Current Buffer I.E

Lecture 20 Transistor Amplifiers (III) Other Amplifier Stages Outline • Common-drain amplifier • Common-gate amplifier Reading Assignment: Howe and Sodini; Chapter 8, Sections 8.7-8.9 6.012 Electronic Devices and Circuits—Fall 2000 Lecture 20 1 Summary of Key Concepts • Common-drain amplifier: good voltage buffer – Voltage gain » 1 – High input resistance – Low output resistance • Common-gate amplifier: good current buffer – Current gain » 1 – Low input resistance – High output resistance 6.012 Electronic Devices and Circuits—Fall 2000 Lecture 20 2 1. Common-drain amplifier • A voltage buffer takes the input voltage which may have a relatively large Thevenin resistance and replicates the voltage at the output port, which has a low output resistance • Input signal is applied to the gate • Output is taken from the source • To first order, voltage gain » 1 – vs » vg. • Input resistance is high • Output resistance is low – Effective voltage buffer stage How does it work? • vG •Þ iD cannot change Þ vS • – Source follower 6.012 Electronic Devices and Circuits—Fall 2000 Lecture 20 3 Biasing the Common-drain amplifier • VGG, ISUP, and W/L selected to bias MOSFET in saturation • Obtain desired output bias voltage – Typically set VOUT to”halfway” between VSS and VDD. • Output voltage maximum VDD-VDSsat • Output voltage minimum set by voltage requirement across ISUP. VBIAS = VGG = VGS + VOUT I = + SUP VGS VTn(VSB) W mnCox 2L 6.012 Electronic Devices and Circuits—Fall 2000 Lecture 20 4 Small-signal Analysis Unloaded small-signal equivalent circuit -

Lecture 17: Common Source/Gate/Drain Amplifiers

EECS 105 Fall 2003, Lecture 17 Lecture 17: Common Source/Gate/Drain Amplifiers Prof. Niknejad Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Lecture Outline MOS Common Source Amp Current Source Active Load Common Gate Amp Common Drain Amp Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Common-Source Amplifier Isolate DC level Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Load-Line Analysis to find Q V −V I = DD out RD RD Q 1 5V slope = I = 10k D 10k 0V I = D 10k Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Small-Signal Analysis =∞ Rin Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Two-Port Parameters: Generic Transconductance Amp Rs + vs Rin Gmvin RL vin Rout − Find Rin, Rout, Gm =∞ Rin = = Gm gm RrRout o|| D Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Two-Port CS Model Reattach source and load one-ports: Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Maximize Gain of CS Amp =− AgRrv mD|| o Increase the gm (more current) Increase RD (free? Don’t need to dissipate extra power) Limit: Must keep the device in saturation =− > VVIRVDS DD D D DS, sat For a fixed current, the load resistor can only be chosen so large To have good swing we’d also like to avoid getting to close to saturation Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. -

EE 203 Lecture 12

EE 330 Lecture 30 Basic amplifier architectures • Common Emitter/Source • Common Collector/Drain • Common Base/Gate Review from Previous Lecture Two-port representation of amplifiers Unilateral amplifiers: y V1 y11 22 V2 y21V1 • Thevenin equivalent output port often more standard • RIN, AV, and ROUT often used to characterize the two-port of amplifiers ROUT AVV1 V1 RIN V2 Unilateral amplifier in terms of “amplifier” parameters 1 y21 1 R A ROUT IN V y y11 y22 22 Review from Previous Lecture Relationship with Dependent Sources ? I1 I2 RIN ROUT AVRV2 V1 AVV1 V2 Two Port (Thevenin) Dependent sources from EE 201 200VB 16IA VIN IA VB Example showing two dependent sources Review from Previous Lecture Relationship with Dependent Sources ? I1 I2 RIN ROUT AVRV2 V1 AVV1 V2 Two Port (Thevenin) Dependent sources from EE 201 Voltage Transconductance Amplifier Vs=µVx Is=αVx Amplifier Voltage Dependent Voltage Dependent Voltage Source Current Source Transresistance Current Amplifier Vs=ρIx Is=βIx Amplifier Current Dependent Current Dependent Voltage Source Current Source Review From Previous Lecture Relationship with Dependent Sources ? I1 I2 RIN ROUT AVRV2 V1 AVV1 V2 Two Port (Thevenin) It follows that AVR=0 RIN= AV=µ ROUT=0 I1 I2 Vs=µVx V1 AVV1 V2 Two Port (Thevenin) V2=AVV1 Voltage dependent voltage source is a unilateral floating two-port voltage amplifier with RIN=∞ and ROUT=0 Review From Previous Lecture Relationship with Dependent Sources ? I1 I2 RIN ROUT AVRV2 V1 AVV1 V2 Two Port (Thevenin) It follows that AVR=0 RIN=0 ρ =RT ROUT=0 I1 I2 Vs=ρIx -

Design of a Magnetically Tunable Low Noise Amplifier in 0.13 Um CMOS Technology Jeremy Brown Iowa State University

Iowa State University Capstones, Theses and Graduate Theses and Dissertations Dissertations 2012 Design of a Magnetically Tunable Low Noise Amplifier in 0.13 um CMOS Technology Jeremy Brown Iowa State University Follow this and additional works at: https://lib.dr.iastate.edu/etd Part of the Electrical and Electronics Commons Recommended Citation Brown, Jeremy, "Design of a Magnetically Tunable Low Noise Amplifier in 0.13 um CMOS Technology" (2012). Graduate Theses and Dissertations. 12672. https://lib.dr.iastate.edu/etd/12672 This Thesis is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact [email protected]. Design of a Magnetically Tunable Low Noise Amplifier in 0.13µm CMOS Technology By Jeremy L. Brown A thesis submitted to the graduate faculty in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE Major: Electrical Engineering Program of Study Committee: Nathan Neihart, Major Professor Degang Chen Mani Mina Iowa State University Ames, Iowa 2012 Copyright © Jeremy L. Brown, 2012. All rights reserved. ii TABLE OF CONTENTS LIST OF FIGURES ................................................................................................................. iv ACKNOWLEDGEMENTS ...................................................................................................