Fundamentals of MOSFET and IGBT Gate Driver Circuits

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Run Capacitor Info-98582

Run Cap Quiz-98582_Layout 1 4/16/15 10:26 AM Page 1 ® Run Capacitor Info WHAT IS A CAPACITOR? Very simply, a capacitor is a device that stores and discharges electrons. While you may hear capacitors referred to by a variety of names (condenser, run, start, oil, etc.) all capacitors are comprised of two or more metallic plates separated by an insulating material called a dielectric. PLATE 1 PLATE 2 A very simple capacitor can be made with two plates separated by a dielectric, in this PLATE 1 PLATE 2 case air, and connected to a source of DC current, a battery. Electrons will flow away from plate 1 and collect on plate 2, leaving it with an abundance of electrons, or a “charge”. Since current from a battery only flows one way, the capacitor plate will stay BATTERY + – charged this way unless something causes current flow. If we were to short across the plates with a screwdriver, the resulting spark would indicate the electrons “jumping” from plate 2 to plate 1 in an attempt to equalize. As soon as the screwdriver is removed, plate 2 will again collect a PLATE 1 PLATE 2 charge. + BATTERY – Now let’s connect our simple capacitor to a source of AC current and in series with the windings of an electric motor. Since AC current alternates, first one PLATE 1 PLATE 2 MOTOR plate, then the other would be charged and discharged in turn. First plate 1 is charged, then as the current reverses, a rush of electrons flow from plate 1 to plate 2 through the motor windings. -

UCC27531 35-V Gate Driver for Sic MOSFET Applications (Rev. A)

(1) Application Report SLUA770A–March 2016–Revised May 2018 UCC27531 35-V Gate Driver for SiC MOSFET Applications Richard Herring........................................................................................... High Power Driver Solutions ABSTRACT SiC MOSFETs are gaining popularity in many high-power applications due to their significant switching performance advantages. SiC MOSFETs are also available with attractive voltage ratings and current capabilities. However, the characteristics of SiC MOSFETs require consideration of the gate-driver circuit to optimize the switching performance of the SiC device. Although SiC MOSFETs are not difficult to drive properly, many typical MOSFET drivers may result in compromised switching speed performance. The UCC27531 gate driver includes features and has operating parameters that allow for driving SiC power MOSFETs within the recommended optimum drive configuration. This application note reviews the characteristics of SiC MOSFETs and how to drive them to achieve the performance improvement that SiC can bring at the system level. The features of UCC27531 to achieve optimal performance of SiC are explained and results from a demonstration circuit are provided. 1 Introduction In the past, the majority of applications such as uninterruptible power supplies (UPS), photovoltaic (PV) inverters, and motor drive have utilized IGBTs for the power devices due to the combination of high- voltage ratings exceeding 1 kV and high current capability. Usable switching frequency of IGBTs has typically been limited to 20–30 kHz, due to the high turnoff losses caused by the long turnoff current tail. Design comparisons have shown that SiC MOSFET designs can operate at considerably higher switching frequency and achieve the same or better efficiency. Although the device cost of the SiC MOSFETs are higher than the equivalent IGBTs, the significant savings in transformer, capacitor, and enclosure size results in a lower system cost. -

Egan® Ics for Low Voltage DC-DC Applications Egan® Ics for Low Voltage DC-DC Applications EFFICIENT POWER CONVERSION

APPLICATION NOTE: AN025 eGaN® ICs for Low Voltage DC-DC Applications eGaN® ICs for Low Voltage DC-DC Applications EFFICIENT POWER CONVERSION Michael de Rooij, Ph.D., Vice President of Applications Engineering , Yuanzhe Zhang, Ph.D., Director of Applications Engineering eGaN® FETs from EPC have repeatedly demonstrated higher performance over Monolithic integration of the gate driver to the MOSFET counterparts in many applications [1]. The lateral structure and material FET offers the lowest possible common source properties of eGaN FETs make it possible to monolithically integrate a number of FETs inductance (CSI) as it is moved to within the as demonstrated by products such as the EPC2107 [2]. The next phase in the eGaN IC structure. Furthermore the gate driver has been optimized for the FET being driven to offer FET and IC evolution includes gate driver integration. Integrating the gate driver with maximum performance under any operating the FET offers a number of additional advantages over discrete gate driver and FET condition. These benefits are on top of the well- solutions such as extremely low common source inductance, matched gate driver established low capacitance and inductance, and to FET, and ease of design. All the traditional eGaN FET benefits such as significantly zero reverse recovery charge (QRR) that enable lower capacitance and inductance with zero reverse recovery charge (QRR) in a smaller efficient operation at high switching frequencies even under hard switching conditions. The key footprint for a given on-resistance (RDS(on)) than comparable MOSFETs are retained. However, the combined effect of the new characteristics and benefits ensures an ever characteristics of the EPC2112 are given in table 1. -

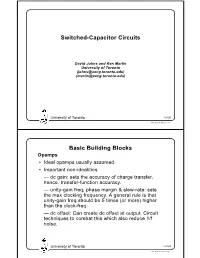

Switched-Capacitor Circuits

Switched-Capacitor Circuits David Johns and Ken Martin University of Toronto ([email protected]) ([email protected]) University of Toronto 1 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Opamps • Ideal opamps usually assumed. • Important non-idealities — dc gain: sets the accuracy of charge transfer, hence, transfer-function accuracy. — unity-gain freq, phase margin & slew-rate: sets the max clocking frequency. A general rule is that unity-gain freq should be 5 times (or more) higher than the clock-freq. — dc offset: Can create dc offset at output. Circuit techniques to combat this which also reduce 1/f noise. University of Toronto 2 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Double-Poly Capacitors metal C1 metal poly1 Cp1 thin oxide bottom plate C1 poly2 Cp2 thick oxide C p1 Cp2 (substrate - ac ground) cross-section view equivalent circuit • Substantial parasitics with large bottom plate capacitance (20 percent of C1) • Also, metal-metal capacitors are used but have even larger parasitic capacitances. University of Toronto 3 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Switches I I Symbol n-channel v1 v2 v1 v2 I transmission I I gate v1 v p-channel v 2 1 v2 I • Mosfet switches are good switches. — off-resistance near G: range — on-resistance in 100: to 5k: range (depends on transistor sizing) • However, have non-linear parasitic capacitances. University of Toronto 4 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Non-Overlapping Clocks I1 T Von I I1 Voff n – 2 n – 1 n n + 1 tTe delay 1 I fs { --- delay V 2 T on I Voff 2 n – 32e n – 12e n + 12e tTe • Non-overlapping clocks — both clocks are never on at same time • Needed to ensure charge is not inadvertently lost. -

Power Electronics

Diodes and Transistors Semiconductors • Semiconductor devices are made of alternating layers of positively doped material (P) and negatively doped material (N). • Diodes are PN or NP, BJTs are PNP or NPN, IGBTs are PNPN. Other devices are more complex Diodes • A diode is a device which allows flow in one direction but not the other. • When conducting, the diodes create a voltage drop, kind of acting like a resistor • There are three main types of power diodes – Power Diode – Fast recovery diode – Schottky Diodes Power Diodes • Max properties: 1500V, 400A, 1kHz • Forward voltage drop of 0.7 V when on Diode circuit voltage measurements: (a) Forward biased. (b) Reverse biased. Fast Recovery Diodes • Max properties: similar to regular power diodes but recover time as low as 50ns • The following is a graph of a diode’s recovery time. trr is shorter for fast recovery diodes Schottky Diodes • Max properties: 400V, 400A • Very fast recovery time • Lower voltage drop when conducting than regular diodes • Ideal for high current low voltage applications Current vs Voltage Characteristics • All diodes have two main weaknesses – Leakage current when the diode is off. This is power loss – Voltage drop when the diode is conducting. This is directly converted to heat, i.e. power loss • Other problems to watch for: – Notice the reverse current in the recovery time graph. This can be limited through certain circuits. Ways Around Maximum Properties • To overcome maximum voltage, we can use the diodes in series. Here is a voltage sharing circuit • To overcome maximum current, we can use the diodes in parallel. -

Kirchhoff's Laws in Dynamic Circuits

Kirchhoff’s Laws in Dynamic Circuits Dynamic circuits are circuits that contain capacitors and inductors. Later we will learn to analyze some dynamic circuits by writing and solving differential equations. In these notes, we consider some simpler examples that can be solved using only Kirchhoff’s laws and the element equations of the capacitor and the inductor. Example 1: Consider this circuit Additionally, we are given the following representations of the voltage source voltage and one of the resistor voltages: ⎧⎧10 V fortt<< 0 2 V for 0 vvs ==⎨⎨and 1 −5t ⎩⎩20 V forte>+ 0 8 4 V fort> 0 We wish to express the capacitor current, i 2 , as a function of time, t. Plan: First, apply Kirchhoff’s voltage law (KVL) to the loop consisting of the source, resistor R1 and the capacitor to determine the capacitor voltage, v 2 , as a function of time, t. Next, use the element equation of the capacitor to determine the capacitor current as a function of time, t. Solution: Apply Kirchhoff’s voltage law (KVL) to the loop consisting of the source, resistor R1 and the capacitor to write ⎧ 8 V fort < 0 vvv12+−=ss0 ⇒ v2 =−= vv 1⎨ −5t ⎩16− 8et V for> 0 Use the element equation of the capacitor to write ⎧ 0 A fort < 0 dv22 dv ⎪ ⎧ 0 A fort < 0 iC2 ==0.025 =⎨⎨d −5t =−5t dt dt ⎪0.025() 16−> 8et for 0 ⎩1et A for> 0 ⎩ dt 1 Example 2: Consider this circuit where the resistor currents are given by ⎧⎧0.8 A fortt<< 0 0 A for 0 ii13==⎨⎨−−22ttand ⎩⎩0.8et−> 0.8 A for 0 −0.8 e A fort> 0 Express the inductor voltage, v 2 , as a function of time, t. -

A High Efficiency 0.13Μm CMOS Full Wave Active Rectifier With

Advances in Science, Technology and Engineering Systems Journal ASTES Journal Vol. 2, No. 3, 1019-1025 (2017) ISSN: 2415-6698 www.astesj.com Special issue on Recent Advances in Engineering Systems A High Efficiency 0.13µm CMOS Full Wave Active Rectifier with Comparators for Implanted Medical Devices Joao˜ Ricardo de Castilho Louzada, Leonardo Breseghello Zoccal, Robson Luiz Moreno, Tales Cleber Pimenta Federal University of Itajuba,´ IEST, Itajuba´ - MG, Brazil ARTICLEINFO ABSTRACT Article history: This paper presents a full wave active rectifier for biomedical implanted Received: 30 April, 2017 devices using a new comparator in order to reduce the rectifier Accepted: 29 June, 2017 transistors reverse current. The rectifier was designed in 0.13µm Online: 11 July, 2017 CMOS process and it can deliver 1.2Vdc for a minimum signal of Keywords: 1.3Vac. It achieves a power conversion e ciency of 92% at the Active Rectifier ffi 13.56MHz Scientific and Medical (ISM) band. CMOS Comparator Medical Devices 1 Introduction but it is unusable for circuits running on power sup- plies of 1V or less. Alternatively to the conventional This paper is an extension of work originally pre- diodes, Schottky diodes can be used, but the manu- sented in The 15th International Symposium on In- facturing process of low forward drop voltage can be tegrated Circuits, Sigapure, 2016 [1]. It presents some more expensive than the traditional processes [4] be- details not described in the original paper. This paper cause they might not be present in some regular pro- also brings new results obtained after a new calibra- cesses and require extra fabrication steps [5]. -

Failure Precursors for Insulated Gate Bipolar Transistors (Igbts) Nishad Patil1, Diganta Das1, Kai Goebel2 and Michael Pecht1

Failure Precursors for Insulated Gate Bipolar Transistors (IGBTs) 1 1 2 1 Nishad Patil , Diganta Das , Kai Goebel and Michael Pecht 1Center for Advanced Life Cycle Engineering (CALCE) University of Maryland College Park, MD 20742, USA 2NASA Ames Research Center Moffett Field, CA 94035, USA Abstract Failure precursors indicate changes in a measured variable that can be associated with impending failure. By identifying precursors to failure and by monitoring them, system failures can be predicted and actions can be taken to mitigate their effects. In this study, three potential failure precursor candidates, threshold voltage, transconductance, and collector-emitter ON voltage, are evaluated for insulated gate bipolar transistors (IGBTs). Based on the failure causes determined by the failure modes, mechanisms and effects analysis (FMMEA), IGBTs are aged using electrical-thermal stresses. The three failure precursor candidates of aged IGBTs are compared with new IGBTs under a temperature range of 25-200oC. The trends in the three electrical parameters with changes in temperature are correlated to device degradation. A methodology is presented for validating these precursors for IGBT prognostics using a hybrid approach. Keywords: Failure precursors, IGBTs, prognostics Failure precursors indicate changes in a measured variable structure of an IGBT is similar to that of a vertical that can be associated with impending failure [1]. A diffusion power MOSFET (VDMOS) [3] except for an systematic method for failure precursor selection is additional p+ layer above the collector as seen in Figure 1. through the use of the failure modes, mechanisms, and The main characteristic of the vertical configuration is that effects analysis (FMMEA) [2]. -

Selecting the Optimal Inductor for Power Converter Applications

Selecting the Optimal Inductor for Power Converter Applications BACKGROUND SDR Series Power Inductors Today’s electronic devices have become increasingly power hungry and are operating at SMD Non-shielded higher switching frequencies, starving for speed and shrinking in size as never before. Inductors are a fundamental element in the voltage regulator topology, and virtually every circuit that regulates power in automobiles, industrial and consumer electronics, SRN Series Power Inductors and DC-DC converters requires an inductor. Conventional inductor technology has SMD Semi-shielded been falling behind in meeting the high performance demand of these advanced electronic devices. As a result, Bourns has developed several inductor models with rated DC current up to 60 A to meet the challenges of the market. SRP Series Power Inductors SMD High Current, Shielded Especially given the myriad of choices for inductors currently available, properly selecting an inductor for a power converter is not always a simple task for designers of next-generation applications. Beginning with the basic physics behind inductor SRR Series Power Inductors operations, a designer must determine the ideal inductor based on radiation, current SMD Shielded rating, core material, core loss, temperature, and saturation current. This white paper will outline these considerations and provide examples that illustrate the role SRU Series Power Inductors each of these factors plays in choosing the best inductor for a circuit. The paper also SMD Shielded will describe the options available for various applications with special emphasis on new cutting edge inductor product trends from Bourns that offer advantages in performance, size, and ease of design modification. -

Capacitors and Inductors

DC Principles Study Unit Capacitors and Inductors By Robert Cecci In this text, you’ll learn about how capacitors and inductors operate in DC circuits. As an industrial electrician or elec- tronics technician, you’ll be likely to encounter capacitors and inductors in your everyday work. Capacitors and induc- tors are used in many types of industrial power supplies, Preview Preview motor drive systems, and on most industrial electronics printed circuit boards. When you complete this study unit, you’ll be able to • Explain how a capacitor holds a charge • Describe common types of capacitors • Identify capacitor ratings • Calculate the total capacitance of a circuit containing capacitors connected in series or in parallel • Calculate the time constant of a resistance-capacitance (RC) circuit • Explain how inductors are constructed and describe their rating system • Describe how an inductor can regulate the flow of cur- rent in a DC circuit • Calculate the total inductance of a circuit containing inductors connected in series or parallel • Calculate the time constant of a resistance-inductance (RL) circuit Electronics Workbench is a registered trademark, property of Interactive Image Technologies Ltd. and used with permission. You’ll see the symbol shown above at several locations throughout this study unit. This symbol is the logo of Electronics Workbench, a computer-simulated electronics laboratory. The appearance of this symbol in the text mar- gin signals that there’s an Electronics Workbench lab experiment associated with that section of the text. If your program includes Elec tronics Workbench as a part of your iii learning experience, you’ll receive an experiment lab book that describes your Electronics Workbench assignments. -

Graphene Field-Effect Transistor Array with Integrated Electrolytic Gates Scaled to 200 Mm

Graphene field-effect transistor array with integrated electrolytic gates scaled to 200 mm N C S Vieira1,3, J Borme1, G Machado Jr.1, F Cerqueira2, P P Freitas1, V Zucolotto3, N M R Peres2 and P Alpuim1,2 1INL - International Iberian Nanotechnology Laboratory, 4715-330, Braga, Portugal. 2CFUM - Center of Physics of the University of Minho, 4710-057, Braga, Portugal. 3IFSC - São Carlos Institute of Physics, University of São Paulo, 13560-970, São Carlos-SP, Brazil E-mail: [email protected] Abstract Ten years have passed since the beginning of graphene research. In this period we have witnessed breakthroughs both in fundamental and applied research. However, the development of graphene devices for mass production has not yet reached the same level of progress. The architecture of graphene field-effect transistors (FET) has not significantly changed, and the integration of devices at the wafer scale has generally not been sought. Currently, whenever an electrolyte-gated FET (EGFET) is used, an external, cumbersome, out-of-plane gate electrode is required. Here, an alternative architecture for graphene EGFET is presented. In this architecture, source, drain, and gate are in the same plane, eliminating the need for an external gate electrode and the use of an additional reservoir to confine the electrolyte inside the transistor active zone. This planar structure with an integrated gate allows for wafer-scale fabrication of high-performance graphene EGFETs, with carrier mobility up to 1800 cm2 V-1 s-1. As a proof-of principle, a chemical sensor was achieved. It is shown that the sensor can discriminate between saline solutions of different concentrations. -

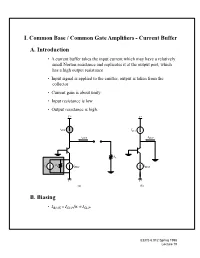

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp.