The Bipolar Junction Transistor (BJT)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Using Rctime to Measure Resistance

Basic Express Application Note Using RCtime to Measure Resistance Introduction One common use for I/O pins is to measure the analog value of a variable resistance. Although a built-in ADC (Analog to Digital Converter) is perhaps the easiest way to do this, it is also possible to use a digital I/O pin. This can be useful in cases where you don't have enough ADC channels, or if a particular processor doesn't have ADC capability. Procedure RCtime BasicX provides a special procedure called RCtime for this purpose. RCtime measures the time it takes for a pin to change state to a defined value. By connecting a fixed capacitor and a variable resistor in an RC circuit, you can use an I/O pin to measure the value of the variable resistor, which might be a device such as a potentiometer or thermistor. There are two common ways to wire an RCtime system. The first is to tie the variable resistor to ground. Figure 1 shows this configuration. The advantage here is less chance of damage from static electricity: Figure 1 Figure 2 The second configuration is shown in Figure 2. Here we use the opposite connection, where the capacitor C is tied to ground and the variable resistor RV is tied to 5 volts: In both circuits resistor R1 is there to protect the BasicX chip's output driver from driving too much current when charging the capacitor. To take a sample, the capacitor is first discharged by taking the pin to the correct state. In the case of Figure 1, the pin needs to be taken high (+5 V) to produce essentially 0 volts across the capacitor, which causes it to discharge. -

Unit-1 Mphycc-7 Ujt

UNIT-1 MPHYCC-7 UJT The Unijunction Transistor or UJT for short, is another solid state three terminal device that can be used in gate pulse, timing circuits and trigger generator applications to switch and control either thyristors and triac’s for AC power control type applications. Like diodes, unijunction transistors are constructed from separate P-type and N-type semiconductor materials forming a single (hence its name Uni-Junction) PN-junction within the main conducting N-type channel of the device. Although the Unijunction Transistor has the name of a transistor, its switching characteristics are very different from those of a conventional bipolar or field effect transistor as it can not be used to amplify a signal but instead is used as a ON-OFF switching transistor. UJT’s have unidirectional conductivity and negative impedance characteristics acting more like a variable voltage divider during breakdown. Like N-channel FET’s, the UJT consists of a single solid piece of N-type semiconductor material forming the main current carrying channel with its two outer connections marked as Base 2 ( B2 ) and Base 1 ( B1 ). The third connection, confusingly marked as the Emitter ( E ) is located along the channel. The emitter terminal is represented by an arrow pointing from the P-type emitter to the N-type base. The Emitter rectifying p-n junction of the unijunction transistor is formed by fusing the P-type material into the N-type silicon channel. However, P-channel UJT’s with an N- type Emitter terminal are also available but these are little used. -

Memristor-The Future of Artificial Intelligence L.Kavinmathi, C.Gayathri, K.Kumutha Priya

International Journal of Scientific & Engineering Research, Volume 5, Issue 4, April-2014 358 ISSN 2229-5518 Memristor-The Future of Artificial Intelligence L.kavinmathi, C.Gayathri, K.Kumutha priya Abstract- Due to increasing demand on miniaturization and low power consumption, Memristor came into existence. Our design exploration is Reconfigurable Threshold Logic Gates based Programmable Analog Circuits using Memristor. Thus a variety of linearly separable and non- linearly separable logic functions such as AND, OR, NAND, NOR, XOR, XNOR have been realized using Threshold logic gate using Memristor. The functionality can be changed between these operations just by varying the resistance of the Memristor. Based on this Reconfigurable TLG, various Programmable Analog circuits can be built using Memristor. As an example of our approach, we have built Programmable analog Gain amplifier demonstrating Memristor-based programming of Threshold, Gain and Frequency. As our idea consisting of Programmable circuit design, in which low voltages are applied to Memristor during their operation as analog circuit element and high voltages are used to program the Memristor’s states. In these circuits the role of memristor is played by Memristor Emulator developed by us using FPGA. Reconfigurable is the option we are providing with the present system, so that the resistance ranges are varied by preprogram too. Index Terms— Memristor, TLG-threshold logic gates, Programmable Analog Circuits, FPGA-field programmable gate array, MTL- memristor threshold logic, CTL-capacitor Threshold logic, LUT- look up table. —————————— ( —————————— 1 INTRODUCTION CCORDING to Chua’s [founder of Memristor] definition, 9444163588. E-mail: [email protected] the internal state of an ideal Memristor depends on the • L.kavinmathi is currently pursuing bachelors degree program in electronics A and communication engineering in tagore engineering college under Anna integral of the voltage or current over time. -

Lab 1: the Bipolar Junction Transistor (BJT): DC Characterization

Lab 1: The Bipolar Junction Transistor (BJT): DC Characterization Electronics II Contents Introduction 2 Day 1: BJT DC Characterization 2 Background . 2 BJT Operation Regions . 2 (i) Saturation Region . 4 (ii) Active Region . 4 (iii) Cutoff Region . 5 Part 1: Diode-Like Behavior of BJT Junctions, and BJT Type 6 Experiment . 6 Creating Your Own File . 6 Report..................................................... 8 Part 2: BJT IC vs. VCE Characteristic Curves - Point by Point Plotting 8 Prelab . 8 Experiment . 8 Creating Your Own File . 8 Parameter Sweep . 9 Report..................................................... 10 Part 3: The Current Mirror 11 Experiment . 12 Simulation . 12 Checkout . 12 Report..................................................... 13 1 ELEC 3509 Electronics II Lab 1 Introduction When designing a circuit, it is important to know the properties of the devices that you will be using. This lab will look at obtaining important device parameters from a BJT. Although many of these can be obtained from the data sheet, data sheets may not always include the information we want. Even if they do, it is also useful to perform our own tests and compare the results. This process is called device characterization. In addition, the tests you will be performing will help you get some experience working with your tools so you don't waste time fumbling around with them in future labs. In Day 1, you will be looking at the DC characteristics of your transistor. This will give you an idea of what the I-V curves look like, and how you would measure them. You will also have to build and test a current mirror, which should give you an idea of how they work and where their limitations are. -

Common Drain - Wikipedia, the Free Encyclopedia 10-5-17 下午7:07

Common drain - Wikipedia, the free encyclopedia 10-5-17 下午7:07 Common drain From Wikipedia, the free encyclopedia In electronics, a common-drain amplifier, also known as a source follower, is one of three basic single- stage field effect transistor (FET) amplifier topologies, typically used as a voltage buffer. In this circuit the gate terminal of the transistor serves as the input, the source is the output, and the drain is common to both (input and output), hence its name. The analogous bipolar junction transistor circuit is the common- collector amplifier. In addition, this circuit is used to transform impedances. For example, the Thévenin resistance of a combination of a voltage follower driven by a voltage source with high Thévenin resistance is reduced to only the output resistance of the voltage follower, a small resistance. That resistance reduction makes the combination a more ideal voltage source. Conversely, a voltage follower inserted between a small load resistance and a driving stage presents an infinite load to the driving stage, an advantage in coupling a voltage signal to a small load. Characteristics At low frequencies, the source follower pictured at right has the following small signal characteristics.[1] Voltage gain: Current gain: Input impedance: Basic N-channel JFET source Output impedance: (the parallel notation indicates the impedance follower circuit (neglecting of components A and B that are connected in parallel) biasing details). The variable gm that is not listed in Figure 1 is the transconductance of the device (usually given in units of siemens). References http://en.wikipedia.org/wiki/Common_drain Page 1 of 2 Common drain - Wikipedia, the free encyclopedia 10-5-17 下午7:07 1. -

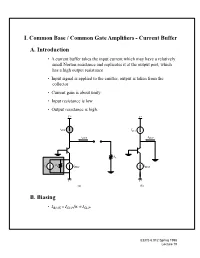

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Ltspice Tutorial Part 4- Intermediate Circuits

Sim Lab 8 P art 2 – E fficiency R evisited Prerequisites ● Please make sure you have completed the following: ○ LTspice tutorial part 1-4 Learn ing Objectives 1. Build circuits that control the motor speed with resistor network and with MOSFET usingLTSpice XVII. 2. By calculating the power efficiency of two speed control circuits, learn that the use of MOSFET in a speed control circuit can increase the power efficiency. Speed control by resist or network ● First, place the components as the following figure. For convenience, we use a resistor in series with an inductor to model the motor. Set the values of resistors, the inductor and the voltage source like the figure. Speed control by resist or network ● Next, connect the circuit as the following figure. We first connect the left three 100 Ω resistors to the circuit. Also, add a label net called “Vmotor_1” and place it right above R6. W e want to monitor the voltage across the motor in this way. ● At the same time, like what we did to a capacitor in previous labs, we also need to set initial conditions for an inductor. Click “Edit” -> Spice Directive -> set “.ic i(L1) = 0”. Speed control by resist or network ● Next, set the simulation condition as the left figure. We are ready to start the simulation. ● The reason to set the stop time as 0.1ms is to observe the change of Vmotor_1 through time from a transient state to steady state. Motor Model Speed control by resist or network ● Run the simulation. ● Plot Vmotor_1 and the current flowing through R6. -

Thyristors.Pdf

THYRISTORS Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Thyristors Thyristors are a class of semiconductor devices characterized by 4-layers of alternating p and n material. Four-layer devices act as either open or closed switches; for this reason, they are most frequently used in control applications. Some thyristors and their symbols are (a) 4-layer diode (b) SCR (c) Diac (d) Triac (e) SCS Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. The Four-Layer Diode The 4-layer diode (or Shockley diode) is a type of thyristor that acts something like an ordinary diode but conducts in the forward direction only after a certain anode to cathode voltage called the forward-breakover voltage is reached. The basic construction of a 4-layer diode and its schematic symbol are shown The 4-layer diode has two leads, labeled the anode (A) and the Anode (A) A cathode (K). p 1 n The symbol reminds you that it acts 2 p like a diode. It does not conduct 3 when it is reverse-biased. n Cathode (K) K Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. The Four-Layer Diode The concept of 4-layer devices is usually shown as an equivalent circuit of a pnp and an npn transistor. Ideally, these devices would not conduct, but when forward biased, if there is sufficient leakage current in the upper pnp device, it can act as base current to the lower npn device causing it to conduct and bringing both transistors into saturation. -

Bias Circuits for RF Devices

Bias Circuits for RF Devices Iulian Rosu, YO3DAC / VA3IUL, http://www.qsl.net/va3iul A lot of RF schematics mention: “bias circuit not shown”; when actually one of the most critical yet often overlooked aspects in any RF circuit design is the bias network. The bias network determines the amplifier performance over temperature as well as RF drive. The DC bias condition of the RF transistors is usually established independently of the RF design. Power efficiency, stability, noise, thermal runway, and ease to use are the main concerns when selecting a bias configuration. A transistor amplifier must possess a DC biasing circuit for a couple of reasons. • We would require two separate voltage supplies to furnish the desired class of bias for both the emitter-collector and the emitter-base voltages. • This is in fact still done in certain applications, but biasing was invented so that these separate voltages could be obtained from but a single supply. • Transistors are remarkably temperature sensitive, inviting a condition called thermal runaway. Thermal runaway will rapidly destroy a bipolar transistor, as collector current quickly and uncontrollably increases to damaging levels as the temperature rises, unless the amplifier is temperature stabilized to nullify this effect. Amplifier Bias Classes of Operation Special classes of amplifier bias levels are utilized to achieve different objectives, each with its own distinct advantages and disadvantages. The most prevalent classes of bias operation are Class A, AB, B, and C. All of these classes use circuit components to bias the transistor at a different DC operating current, or “ICQ”. When a BJT does not have an A.C. -

Robust Wireless Power Transfer Using a Nonlinear Parity–Time-Symmetric Circuit Sid Assawaworrarit1, Xiaofang Yu1 & Shanhui Fan1

LETTER doi:10.1038/nature22404 Robust wireless power transfer using a nonlinear parity–time-symmetric circuit Sid Assawaworrarit1, Xiaofang Yu1 & Shanhui Fan1 Considerable progress in wireless power transfer has been made in PT-symmetric systems are invariant under the joint parity and the realm of non-radiative transfer, which employs magnetic-field time reversal operation14,15. In optical systems, where the symmetry coupling in the near field1–4. A combination of circuit resonance conditions can be met by engineering the gain/loss regions and and impedance transformation is often used to help to achieve their coupling, PT-symmetric systems have exhibited unusual efficient transfer of power over a predetermined distance of about properties16–20. A linear PT-symmetric system supports two phases, the size of the resonators3,4. The development of non-radiative depending on the magnitude of the gain/loss relative to the coupling wireless power transfer has paved the way towards real-world strength. In the unbroken or exact phase, eigenmode frequencies applications such as wireless powering of implantable medical remain real and energy is equally distributed between the gain and devices and wireless charging of stationary electric vehicles1,2,5–8. loss regions; in the broken phase, one of the eigenmodes grows expo- However, it remains a fundamental challenge to create a wireless nentially while the other decays exponentially. Recently, the concept power transfer system in which the transfer efficiency is robust of PT symmetry has been extensively explored in laser structures21–24. against the variation of operating conditions. Here we propose Theoretically, the inclusion of nonlinear gain saturation in the analysis theoretically and demonstrate experimentally that a parity–time- of a PT-symmetric system causes that system to reach a steady state symmetric circuit incorporating a nonlinear gain saturation element in a laser-like fashion that still contains the following PT symmetry provides robust wireless power transfer. -

Lecture 19 Common-Gate Stage

4/7/2008 Lecture 19 OUTLINE • Common‐gate stage • Source follower • Reading: Chap. 7.3‐7.4 EE105 Spring 2008 Lecture 19, Slide 1Prof. Wu, UC Berkeley Common‐Gate Stage AvmD= gR • Common‐gate stage is similar to common‐base stage: a rise in input causes a rise in output. So the gain is positive. EE105 Spring 2008 Lecture 19, Slide 2Prof. Wu, UC Berkeley EE105 Fall 2007 1 4/7/2008 Signal Levels in CG Stage • In order to maintain M1 in saturation, the signal swing at Vout cannot fall below Vb‐VTH EE105 Spring 2008 Lecture 19, Slide 3Prof. Wu, UC Berkeley I/O Impedances of CG Stage 1 R = in λ =0 RRout= D gm • The input and output impedances of CG stage are similar to those of CB stage. EE105 Spring 2008 Lecture 19, Slide 4Prof. Wu, UC Berkeley EE105 Fall 2007 2 4/7/2008 CG Stage with Source Resistance 1 g vv= m Xin1 + RS gm 1 vv g AgR==out x m vmD1 vvxin + RS gm R gR ==D mD 1 1+ gRmS + RS gm • When a source resistance is present, the voltage gain is equal to that of a CS stage with degeneration, only positive. EE105 Spring 2008 Lecture 19, Slide 5Prof. Wu, UC Berkeley Generalized CG Behavior Rgout= (1++g mrR O) S r O • When a gate resistance is present it does not affect the gain and I/O impedances since there is no potential drop across it (at low frequencies). • The output impedance of a CG stage with source resistance is identical to that of CS stage with degeneration.