V. Amplifying Devices and Microelectronics

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

PH-218 Lec-12: Frequency Response of BJT Amplifiers

Analog & Digital Electronics Course No: PH-218 Lec-12: Frequency Response of BJT Amplifiers Course Instructors: Dr. A. P. VAJPEYI Department of Physics, Indian Institute of Technology Guwahati, India 1 High frequency Response of CE Amplifier At high frequencies, internal transistor junction capacitances do come into play, reducing an amplifier's gain and introducing phase shift as the signal frequency increases. In BJT, C be is the B-E junction capacitance, and C bc is the B-C junction capacitance. (output to input capacitance) At lower frequencies, the internal capacitances have a very high reactance because of their low capacitance value (usually only a few pf) and the low frequency value. Therefore, they look like opens and have no effect on the transistor's performance. As the frequency goes up, the internal capacitive reactance's go down, and at some point they begin to have a significant effect on the transistor's gain. High frequency Response of CE Amplifier When the reactance of C be becomes small enough, a significant amount of the signal voltage is lost due to a voltage-divider effect of the source resistance and the reactance of C be . When the reactance of Cbc becomes small enough, a significant amount of output signal voltage is fed back out of phase with the input (negative feedback), thus effectively reducing the voltage gain. 3 Millers Theorem The Miller effect occurs only in inverting amplifiers –it is the inverting gain that magnifies the feedback capacitance. vin − (−Av in ) iin = = vin 1( + A)× 2π × f ×CF X C Here C F represents C bc vin 1 1 Zin = = = iin 1( + A)× 2π × f ×CF 2π × f ×Cin 1( ) Cin = + A ×CF 4 High frequency Response of CE Amp.: Millers Theorem Miller's theorem is used to simplify the analysis of inverting amplifiers at high-frequencies where the internal transistor capacitances are important. -

Common Drain - Wikipedia, the Free Encyclopedia 10-5-17 下午7:07

Common drain - Wikipedia, the free encyclopedia 10-5-17 下午7:07 Common drain From Wikipedia, the free encyclopedia In electronics, a common-drain amplifier, also known as a source follower, is one of three basic single- stage field effect transistor (FET) amplifier topologies, typically used as a voltage buffer. In this circuit the gate terminal of the transistor serves as the input, the source is the output, and the drain is common to both (input and output), hence its name. The analogous bipolar junction transistor circuit is the common- collector amplifier. In addition, this circuit is used to transform impedances. For example, the Thévenin resistance of a combination of a voltage follower driven by a voltage source with high Thévenin resistance is reduced to only the output resistance of the voltage follower, a small resistance. That resistance reduction makes the combination a more ideal voltage source. Conversely, a voltage follower inserted between a small load resistance and a driving stage presents an infinite load to the driving stage, an advantage in coupling a voltage signal to a small load. Characteristics At low frequencies, the source follower pictured at right has the following small signal characteristics.[1] Voltage gain: Current gain: Input impedance: Basic N-channel JFET source Output impedance: (the parallel notation indicates the impedance follower circuit (neglecting of components A and B that are connected in parallel) biasing details). The variable gm that is not listed in Figure 1 is the transconductance of the device (usually given in units of siemens). References http://en.wikipedia.org/wiki/Common_drain Page 1 of 2 Common drain - Wikipedia, the free encyclopedia 10-5-17 下午7:07 1. -

Cascode Amplifiers by Dennis L. Feucht Two-Transistor Combinations

Cascode Amplifiers by Dennis L. Feucht Two-transistor combinations, such as the Darlington configuration, provide advantages over single-transistor amplifier stages. Another two-transistor combination in the analog designer's circuit library combines a common-emitter (CE) input configuration with a common-base (CB) output. This article presents the design equations for the basic cascode amplifier and then offers other useful variations. (FETs instead of BJTs can also be used to form cascode amplifiers.) Together, the two transistors overcome some of the performance limitations of either the CE or CB configurations. Basic Cascode Stage The basic cascode amplifier consists of an input common-emitter (CE) configuration driving an output common-base (CB), as shown above. The voltage gain is, by the transresistance method, the ratio of the resistance across which the output voltage is developed by the common input-output loop current over the resistance across which the input voltage generates that current, modified by the α current losses in the transistors: v R A = out = −α ⋅α ⋅ L v 1 2 β + + + vin RB /( 1 1) re1 RE where re1 is Q1 dynamic emitter resistance. This gain is identical for a CE amplifier except for the additional α2 loss of Q2. The advantage of the cascode is that when the output resistance, ro, of Q2 is included, the CB incremental output resistance is higher than for the CE. For a bipolar junction transistor (BJT), this may be insignificant at low frequencies. The CB isolates the collector-base capacitance, Cbc (or Cµ of the hybrid-π BJT model), from the input by returning it to a dynamic ground at VB. -

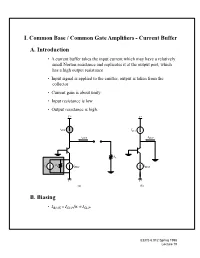

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Dynamic Microphone Amplifier

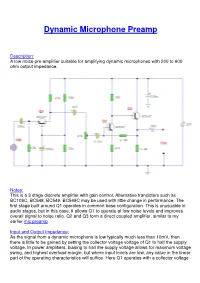

Dynamic Microphone Preamp Description: A low noise pre-amplifier suitable for amplifying dynamic microphones with 200 to 600 ohm output impedance. Notes: This is a 3 stage discrete amplifier with gain control. Alternative transistors such as BC109C, BC548, BC549, BC549C may be used with little change in performance. The first stage built around Q1 operates in common base configuration. This is unusuable in audio stages, but in this case, it allows Q1 to operate at low noise levels and improves overall signal to noise ratio. Q2 and Q3 form a direct coupled amplifier, similar to my earlier mic preamp . Input and Output Impedance: As the signal from a dynamic microphone is low typically much less than 10mV, then there is little to be gained by setting the collector voltage voltage of Q1 to half the supply voltage. In power amplifiers, biasing to half the supply voltage allows for maximum voltage swing, and highest overload margin, but where input levels are low, any value in the linear part of the operating characteristics will suffice. Here Q1 operates with a collector voltage of 2.4V and a low collector current of around 200uA. This low collector current ensures low noise performance and also raises the input impedance of the stage to around 400 ohms. This is a good match for any dynamic microphone having an impedances between 200 and 600 ohms. The output impedance at Q3 is low, the graph of input and output impedance versus frequency is shown below: Gain and Frequency Response: The overall gain of this pre-amplifier is around +39dB or about 90 times. -

Lecture23-Amplifier Frequency Response.Pptx

EE105 – Fall 2014 Microelectronic Devices and Circuits Prof. Ming C. Wu [email protected] 511 Sutardja Dai Hall (SDH) Lecture23-Amplifier Frequency Response 1 Common-Emitter Amplifier – ωH Open-Circuit Time Constant (OCTC) Method At high frequencies, impedances of coupling and bypass capacitors are small enough to be considered short circuits. Open-circuit time constants associated with impedances of device capacitances are considered instead. 1 ωH ≅ m ∑RioCi i=1 where Rio is resistance at terminals of ith capacitor C with all other v ! R $ i R = x = r #1+ g R + L & capacitors open-circuited. µ 0 π 0 m L ix " rπ 0 % For a C-E amplifier, assuming C = 0 L 1 1 ωH ≅ = Rπ 0 = rπ 0 Rπ 0Cπ + Rµ 0Cµ rπ 0CT Lecture23-Amplifier Frequency Response 2 1 Common-Emitter Amplifier High Frequency Response - Miller Effect • First, find the simplified small -signal model of the C-E amp. • Replace coupling and bypass capacitors with short circuits • Insert the high frequency small -signal model for the transistor ! # rπ 0 = rπ "rx +(RB RI )$ Lecture23-Amplifier Frequency Response 3 Common-Emitter Amplifier – ωH High Frequency Response - Miller Effect (cont.) v R r Input gain is found as A = b = in ⋅ π i v R R r r i I + in x + π R || R || (r + r ) r = 1 2 x π ⋅ π RI + R1 || R2 || (rx + rπ ) rx + rπ Terminal gain is vc Abc = = −gm (ro || RC || R3 ) ≅ −gm RL vb Using the Miller effect, we find CeqB = Cµ (1− Abc )+Cπ (1− Abe ) the equivalent capacitance at the base as: = Cµ (1−[−gm RL ])+Cπ (1− 0) = Cµ (1+ gm RL )+Cπ Chap 17-4 Lecture23-Amplifier Frequency Response 4 2 Common-Emitter Amplifier – ωH High Frequency Response - Miller Effect (cont.) ! # • The total equivalent resistance ReqB = rπ 0 = rπ "rx +(RB RI )$ at the base is • The total capacitance and CeqC = Cµ +CL resistance at the collector are ReqC = ro RC R3 = RL • Because of interaction through 1 ω = Cµ, the two RC time constants p1 ! # rπ 0 "Cπ +Cµ (1+ gm RL )$+ RL (Cµ +CL ) interact, giving rise to a dominant pole. -

Lecture 19 Common-Gate Stage

4/7/2008 Lecture 19 OUTLINE • Common‐gate stage • Source follower • Reading: Chap. 7.3‐7.4 EE105 Spring 2008 Lecture 19, Slide 1Prof. Wu, UC Berkeley Common‐Gate Stage AvmD= gR • Common‐gate stage is similar to common‐base stage: a rise in input causes a rise in output. So the gain is positive. EE105 Spring 2008 Lecture 19, Slide 2Prof. Wu, UC Berkeley EE105 Fall 2007 1 4/7/2008 Signal Levels in CG Stage • In order to maintain M1 in saturation, the signal swing at Vout cannot fall below Vb‐VTH EE105 Spring 2008 Lecture 19, Slide 3Prof. Wu, UC Berkeley I/O Impedances of CG Stage 1 R = in λ =0 RRout= D gm • The input and output impedances of CG stage are similar to those of CB stage. EE105 Spring 2008 Lecture 19, Slide 4Prof. Wu, UC Berkeley EE105 Fall 2007 2 4/7/2008 CG Stage with Source Resistance 1 g vv= m Xin1 + RS gm 1 vv g AgR==out x m vmD1 vvxin + RS gm R gR ==D mD 1 1+ gRmS + RS gm • When a source resistance is present, the voltage gain is equal to that of a CS stage with degeneration, only positive. EE105 Spring 2008 Lecture 19, Slide 5Prof. Wu, UC Berkeley Generalized CG Behavior Rgout= (1++g mrR O) S r O • When a gate resistance is present it does not affect the gain and I/O impedances since there is no potential drop across it (at low frequencies). • The output impedance of a CG stage with source resistance is identical to that of CS stage with degeneration. -

High-Frequency Amplifier Response

Section H5: High-Frequency Amplifier Response Now that we’ve got a high frequency models for the BJT, we can analyze the high frequency response of our basic amplifier configurations. Note: in the circuits that follow, the actual signal source (vS) and its associated source resistance (RS) have been included. As discussed in the low frequency response section of our studies, we always knew that this source and resistance was there but we just started our investigations with the input to the transistor (vin). Remember - the analysis process is the same and the relationship between vS and vin is a voltage divider! Again, in some instances in the following discussion, I will be using slightly different notation and taking a different approach than your author. As usual, if this results in confusion, or you are more comfortable with his technique, let me know and we’ll work it out. High Frequency Response of the CE and ER Amplifier The generic common-emitter amplifier circuit of Section D2 is reproduced to the left below and the small signal circuit using the high frequency BJT model is given below right (based on Figures 10.17a and 10.17b of your text). Note that all external capacitors are assumed to be short circuits at high frequencies and are not present in the high frequency equivalent circuit (since the external capacitors are large when compared to the internal capacitances – recall that Zc=1/jωC gets small as the frequency or capacitance gets large). We can simplify the small signal circuit by making the following observations and approximations: ¾ Cce is very small and may be neglected. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Tabulation of Published Data on Electron Devices of the U.S.S.R. Through December 1976

NAT'L INST. OF STAND ms & TECH R.I.C. Pubii - cations A111D4 4 Tfi 3 4 4 NBSIR 78-1564 Tabulation of Published Data on Electron Devices of the U.S.S.R. Through December 1976 Charles P. Marsden Electron Devices Division Center for Electronics and Electrical Engineering National Bureau of Standards Washington, DC 20234 December 1978 Final QC— U.S. DEPARTMENT OF COMMERCE 100 NATIONAL BUREAU OF STANDARDS U56 73-1564 Buraev of Standard! NBSIR 78-1564 1 4 ^79 fyr *'• 1 f TABULATION OF PUBLISHED DATA ON ELECTRON DEVICES OF THE U.S.S.R. THROUGH DECEMBER 1976 Charles P. Marsden Electron Devices Division Center for Electronics and Electrical Engineering National Bureau of Standards Washington, DC 20234 December 1978 Final U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary / Dr. Sidney Harman, Under Secretary Jordan J. Baruch, Assistant Secretary for Science and Technology NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Director - 1 TABLE OF CONTENTS Page Preface i v 1. Introduction 2. Description of the Tabulation ^ 1 3. Organization of the Tabulation ’ [[ ] in ’ 4. Terminology Used the Tabulation 3 5. Groups: I. Numerical 7 II. Receiving Tubes 42 III . Power Tubes 49 IV. Rectifier Tubes 53 IV-A. Mechanotrons , Two-Anode Diode 54 V. Voltage Regulator Tubes 55 VI. Current Regulator Tubes 55 VII. Thyratrons 56 VIII. Cathode Ray Tubes 58 VIII-A. Vidicons 61 IX. Microwave Tubes 62 X. Transistors 64 X-A-l . Integrated Circuits 75 X-A-2. Integrated Circuits (Computer) 80 X-A-3. Integrated Circuits (Driver) 39 X-A-4. Integrated Circuits (Linear) 89 X- B. -

Lecture 33 Multistage Amplifiers (Cont.)

Lecture 33 Multistage Amplifiers (Cont.) DC Coupling: General Trends * Goal: want both input and output to be “centered” at halfway between the positive and negative supplies (or ground, for a single supply) -- in order to have maximum possible swing at the input and at the output. Summary of DC shifts through the single stages: BJT Amp. npn version Type CE positive CB positive CC negative* MOS Amp. n-channel p-channel Type version version CS positive negative CG positive negative CD negative* positive* The DC voltage shifts for CC/CD stages are set by the VBE = 0.7 V drop or by the VGS of the transistor and can be specified by the designer. EE 105 Fall 2001 Lecture 33 DC Coupling Example * Common drain - common collector cascade (infinite input resistance, fairly low output resistance, unity voltage gain ... reasonable voltage buffer) For CC stage, the optimum output voltage of 2.5 V (centered between + 5 V and ground for maximum swing) --> VIN2 = DC input of CC amp = 2.5 + 0.7 V = 3.2 V The DC of the n-channel CD amplifier is then: VIN = DC input of CD amp = VIN2 + VGS1 = 3.2 V + 1.5 V = 4.7 V where we have assumed that VGS1 = 1.5 V as a typical gate-source voltage (actual number comes from ISUP1and (W/L)). * too close to the supply voltage -- input DC level should be centered at or near 2.5 V. EE 105 Fall 2001 Lecture 33 DC Biasing Example (Cont.) * Solution: use p-channel CD amplifier since it shifts the DC level in the positive direction from input to output Selection of large (W/L) for the p-channel --> input DC level can be adjusted closer to 2.5 V.