Cascode Amplifiers by Dennis L. Feucht Two-Transistor Combinations

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

PH-218 Lec-12: Frequency Response of BJT Amplifiers

Analog & Digital Electronics Course No: PH-218 Lec-12: Frequency Response of BJT Amplifiers Course Instructors: Dr. A. P. VAJPEYI Department of Physics, Indian Institute of Technology Guwahati, India 1 High frequency Response of CE Amplifier At high frequencies, internal transistor junction capacitances do come into play, reducing an amplifier's gain and introducing phase shift as the signal frequency increases. In BJT, C be is the B-E junction capacitance, and C bc is the B-C junction capacitance. (output to input capacitance) At lower frequencies, the internal capacitances have a very high reactance because of their low capacitance value (usually only a few pf) and the low frequency value. Therefore, they look like opens and have no effect on the transistor's performance. As the frequency goes up, the internal capacitive reactance's go down, and at some point they begin to have a significant effect on the transistor's gain. High frequency Response of CE Amplifier When the reactance of C be becomes small enough, a significant amount of the signal voltage is lost due to a voltage-divider effect of the source resistance and the reactance of C be . When the reactance of Cbc becomes small enough, a significant amount of output signal voltage is fed back out of phase with the input (negative feedback), thus effectively reducing the voltage gain. 3 Millers Theorem The Miller effect occurs only in inverting amplifiers –it is the inverting gain that magnifies the feedback capacitance. vin − (−Av in ) iin = = vin 1( + A)× 2π × f ×CF X C Here C F represents C bc vin 1 1 Zin = = = iin 1( + A)× 2π × f ×CF 2π × f ×Cin 1( ) Cin = + A ×CF 4 High frequency Response of CE Amp.: Millers Theorem Miller's theorem is used to simplify the analysis of inverting amplifiers at high-frequencies where the internal transistor capacitances are important. -

I. Common Base / Common Gate Amplifiers

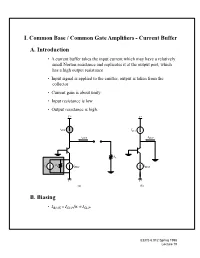

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

Dynamic Microphone Amplifier

Dynamic Microphone Preamp Description: A low noise pre-amplifier suitable for amplifying dynamic microphones with 200 to 600 ohm output impedance. Notes: This is a 3 stage discrete amplifier with gain control. Alternative transistors such as BC109C, BC548, BC549, BC549C may be used with little change in performance. The first stage built around Q1 operates in common base configuration. This is unusuable in audio stages, but in this case, it allows Q1 to operate at low noise levels and improves overall signal to noise ratio. Q2 and Q3 form a direct coupled amplifier, similar to my earlier mic preamp . Input and Output Impedance: As the signal from a dynamic microphone is low typically much less than 10mV, then there is little to be gained by setting the collector voltage voltage of Q1 to half the supply voltage. In power amplifiers, biasing to half the supply voltage allows for maximum voltage swing, and highest overload margin, but where input levels are low, any value in the linear part of the operating characteristics will suffice. Here Q1 operates with a collector voltage of 2.4V and a low collector current of around 200uA. This low collector current ensures low noise performance and also raises the input impedance of the stage to around 400 ohms. This is a good match for any dynamic microphone having an impedances between 200 and 600 ohms. The output impedance at Q3 is low, the graph of input and output impedance versus frequency is shown below: Gain and Frequency Response: The overall gain of this pre-amplifier is around +39dB or about 90 times. -

Cascode Techniques

Analysis and Design of Analog Integrated Circuits Lecture 8 Cascode Techniques Michael H. Perrott February 15, 2012 Copyright © 2012 by Michael H. Perrott All rights reserved. M.H. Perrott Review of Large Signal Analysis of Current Mirrors Vdd Δ V2 I I 1 2 1 μ W2 2 λ nCox (VGS2-VTH) (1+ 2Vds2) I2 2 L = 2 I 1 W 2 1 μ C 1(V -V ) (1+λ V ) 2 n ox GS1 TH 1 ds1 M L1 2 ΔV M1 Vds2 > Vdsat2 1 V +ΔV V +ΔV Δ Δ Δ Δ Vss=0 TH 1 TH 2 But, VTH+ V1=VTH+ V2 V1 = V2 λ I2 W2 L1 (1+ 2Vds2) I2 = λ I1 W1 L2 (1+ 1Vds1) M2 in Saturation Current Mismatch setting due to Vds based on difference M2 in Triode geometry Note: for accurate ratio, set L1 = L2 Vds2 Vdsat2 M.H. Perrott 2 The Issue of Vds Mismatch in Current Mirrors V λ dd I2 W2 (1+ 2Vds2) = λ I1 W1 (1+ 1Vds1) I1 I2 Current Mismatch setting due to Vds based on difference geometry V V ds1 ds2 Note: we are assuming L = L M1 M2 1 2 . Issue: Current I2 can vary significantly as a function of the drain voltage of M2 - We often want a tightly controlled current set only by I1 and transistor sizes . How do we improve the current mirror matching performance? M.H. Perrott 3 Cascoded Current Source I Rth R ref d3 thd3 Ibias Vbias V M bias 3 M3 M ro1 2 M1 . Offers increased output resistance - Reduces small signal dependence of output current on the output voltage of the current source - From Lecture 6, we derived: . -

Lecture23-Amplifier Frequency Response.Pptx

EE105 – Fall 2014 Microelectronic Devices and Circuits Prof. Ming C. Wu [email protected] 511 Sutardja Dai Hall (SDH) Lecture23-Amplifier Frequency Response 1 Common-Emitter Amplifier – ωH Open-Circuit Time Constant (OCTC) Method At high frequencies, impedances of coupling and bypass capacitors are small enough to be considered short circuits. Open-circuit time constants associated with impedances of device capacitances are considered instead. 1 ωH ≅ m ∑RioCi i=1 where Rio is resistance at terminals of ith capacitor C with all other v ! R $ i R = x = r #1+ g R + L & capacitors open-circuited. µ 0 π 0 m L ix " rπ 0 % For a C-E amplifier, assuming C = 0 L 1 1 ωH ≅ = Rπ 0 = rπ 0 Rπ 0Cπ + Rµ 0Cµ rπ 0CT Lecture23-Amplifier Frequency Response 2 1 Common-Emitter Amplifier High Frequency Response - Miller Effect • First, find the simplified small -signal model of the C-E amp. • Replace coupling and bypass capacitors with short circuits • Insert the high frequency small -signal model for the transistor ! # rπ 0 = rπ "rx +(RB RI )$ Lecture23-Amplifier Frequency Response 3 Common-Emitter Amplifier – ωH High Frequency Response - Miller Effect (cont.) v R r Input gain is found as A = b = in ⋅ π i v R R r r i I + in x + π R || R || (r + r ) r = 1 2 x π ⋅ π RI + R1 || R2 || (rx + rπ ) rx + rπ Terminal gain is vc Abc = = −gm (ro || RC || R3 ) ≅ −gm RL vb Using the Miller effect, we find CeqB = Cµ (1− Abc )+Cπ (1− Abe ) the equivalent capacitance at the base as: = Cµ (1−[−gm RL ])+Cπ (1− 0) = Cµ (1+ gm RL )+Cπ Chap 17-4 Lecture23-Amplifier Frequency Response 4 2 Common-Emitter Amplifier – ωH High Frequency Response - Miller Effect (cont.) ! # • The total equivalent resistance ReqB = rπ 0 = rπ "rx +(RB RI )$ at the base is • The total capacitance and CeqC = Cµ +CL resistance at the collector are ReqC = ro RC R3 = RL • Because of interaction through 1 ω = Cµ, the two RC time constants p1 ! # rπ 0 "Cπ +Cµ (1+ gm RL )$+ RL (Cµ +CL ) interact, giving rise to a dominant pole. -

CHAPTER 3 Frequency Response of Basic BJT and MOSFET Amplifiers (Review Materials in Appendices III and V)

CHAPTER 3 Frequency Response of Basic BJT and MOSFET Amplifiers (Review materials in Appendices III and V) In this chapter you will learn about the general form of the frequency domain transfer function of an amplifier. You will learn to analyze the amplifier equivalent circuit and determine the critical frequencies that limit the response at low and high frequencies. You will learn some special techniques to determine these frequencies. BJT and MOSFET amplifiers will be considered. You will also learn the concepts that are pursued to design a wide band width amplifier. Following topics will be considered. Review of Bode plot technique. Ways to write the transfer (i.e., gain) functions to show frequency dependence. Band-width limiting at low frequencies (i.e., DC to fL). Determination of lower band cut-off frequency for a single-stage amplifier – short circuit time constant technique. Band-width limiting at high frequencies for a single-stage amplifier. Determination of upper band cut-off frequency- several alternative techniques. Frequency response of a single device (BJT, MOSFET). Concepts related to wide-band amplifier design – BJT and MOSFET examples. 3.1 A short review on Bode plot technique Example: Produce the Bode plots for the magnitude and phase of the transfer function 10s Ts() , for frequencies between 1 rad/sec to 106 rad/sec. (1ss / 1025 )(1 / 10 ) We first observe that the function has zeros and poles in the numerical sequence 0 (zero), 2 5 2 10 (pole), and 10 (pole). Further at ω=1 rad/sec i.e., lot less than the first pole (at ω=10 rad/sec), Ts() 10 s. -

Optimal High Performance Self Cascode CMOS Current Mirror

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Global Journal of Computer Science and Technology (GJCST) Global Journal of Computer Science and Technology Volume 11 Issue 15 Version 1.0 September 2011 Type: Double Blind Peer Reviewed International Research Journal Publisher: Global Journals Inc. (USA) Online ISSN: 0975-4172 & Print ISSN: 0975-4350 Optimal High Performance Self Cascode CMOS Current Mirror By Vivek Pant, Shweta Khurana Kurukshetra University Kurukshetra Abstract - In this paper the current mirror presented, having low voltage and mixed mode structure has been proposed. The performance of self cascade MOSFET current mirror is optimized with high output impedance and can operate at 1 V or below. Simulation results conform to Analog Mentor tools having Design Architect for schematics and Eldonet for SPICE simulation, with input reference current of 20μA. This review paper presents a comparative performance study of self cascode current mirror with other current mirrors. Keywords : current mirrors, cascode current mirror, low voltage analog circuit. GJCST Classification : I.2.9 Optimal High Performance Self Cascode CMOS Current Mirror Strictly as per the compliance and regulations of: © 2011. Vivek Pant, Shweta Khurana.This is a research/review paper, distributed under the terms of the Creative Commons Attribution-Noncommercial 3.0 Unported License http://creativecommons.org/licenses/by-nc/3.0/), permitting all non commercial use, distribution, and reproduction in any medium, provided the original work is properly cited. Optimal High Performance Self Cascode CMOS Current Mirror Vivek Pantα, Shweta KhuranaΩ Abstract - In this paper the current mirror presented, having I = I (W/L) 2 (1+λVds2) (3) out ref low voltage and mixed mode structure has been proposed. -

Lecture 19 Common-Gate Stage

4/7/2008 Lecture 19 OUTLINE • Common‐gate stage • Source follower • Reading: Chap. 7.3‐7.4 EE105 Spring 2008 Lecture 19, Slide 1Prof. Wu, UC Berkeley Common‐Gate Stage AvmD= gR • Common‐gate stage is similar to common‐base stage: a rise in input causes a rise in output. So the gain is positive. EE105 Spring 2008 Lecture 19, Slide 2Prof. Wu, UC Berkeley EE105 Fall 2007 1 4/7/2008 Signal Levels in CG Stage • In order to maintain M1 in saturation, the signal swing at Vout cannot fall below Vb‐VTH EE105 Spring 2008 Lecture 19, Slide 3Prof. Wu, UC Berkeley I/O Impedances of CG Stage 1 R = in λ =0 RRout= D gm • The input and output impedances of CG stage are similar to those of CB stage. EE105 Spring 2008 Lecture 19, Slide 4Prof. Wu, UC Berkeley EE105 Fall 2007 2 4/7/2008 CG Stage with Source Resistance 1 g vv= m Xin1 + RS gm 1 vv g AgR==out x m vmD1 vvxin + RS gm R gR ==D mD 1 1+ gRmS + RS gm • When a source resistance is present, the voltage gain is equal to that of a CS stage with degeneration, only positive. EE105 Spring 2008 Lecture 19, Slide 5Prof. Wu, UC Berkeley Generalized CG Behavior Rgout= (1++g mrR O) S r O • When a gate resistance is present it does not affect the gain and I/O impedances since there is no potential drop across it (at low frequencies). • The output impedance of a CG stage with source resistance is identical to that of CS stage with degeneration. -

FJP2145 — ESBC™ Rated NPN Power Transistor MOS- (2) ™ March 2015 FDC655 FJP2145 S C G B Figure 3

FJP2145 — ESBC™ Rated ESBC™ FJP2145 — March 2015 FJP2145 ESBC™ Rated NPN Power Transistor ESBC Features (FDC655 MOSFET) Description NPN Power Transistor (1) The FJP2145 is a low-cost, high-performance power VCS(ON) IC Equiv. RCS(ON) switch designed to provide the best performance when 0.21 V 2 A 0.105 Ω used in an ESBC™ configuration in applications such as: • Low Equivalent On Resistance power supplies, motor drivers, smart grid, or ignition • Very Fast Switch: 150 kHz switches. The power switch is designed to operate up to 1100 volts and up to 5 amps, while providing exception- • Wide RBSOA: Up to 1100 V ally low on-resistance and very low switching losses. •Avalanche Rated ™ • Low Driving Capacitance, No Miller Capacitance The ESBC switch can be driven using off-the-shelf power supply controllers or drivers. The ESBC™ MOS- • Low Switching Losses FET is a low-voltage, low-cost, surface-mount device that • Reliable HV Switch: No False Triggering due to combines low-input capacitance and fast switching. The High dv/dt Transients ESBC™ configuration further minimizes the required driv- ing power because it does not have Miller capacitance. Applications The FJP2145 provides exceptional reliability and a large • High-Voltage, High-Speed Power Switch operating range due to its square reverse-bias-safe-oper- • Emitter-Switched Bipolar/MOSFET Cascode ating-area (RBSOA) and rugged design. The device is (ESBC™) avalanche rated and has no parasitic transistors, so is not prone to static dv/dt failures. • Smart Meters, Smart Breakers, SMPS, HV Industrial Power Supplies The power switch is manufactured using a dedicated • Motor Drivers and Ignition Drivers high-voltage bipolar process and is packaged in a high- voltage TO-220 package. -

Experiment No. 7 - BJT Amplifier Input/Output Impedances

UNIVERSITY OF NORTH CAROLINA AT CHARLOTTE Department of Electrical and Computer Engineering Experiment No. 7 - BJT Amplifier Input/Output Impedances Overview: The purpose of this lab is to familiarize the student with the measurement of the input and output impedances of a Bipolar Junction Transistor single-stage amplifier. In previous experiments the DC biasing and AC amplification in BJT amplifiers has been investigated. This BJT experiment will build upon these previous experiments as well as expand into the investigation of input and output impedances. The amplifier chosen for study is the common-emmitter type as shown in Figure 1. Techniques for properly biasing the BJT amplifier and setting up AC amplification will be further utilized and methods for measuring imput and output impedances will be introduced. While the input impedance of an amplifier is in general a complex quantity, in the midband range it is predominantly resistive. Input impedance is defined as the ratio of imput voltage to input current. It is calculated from the AC equivalent circuit as the equivalent resistance looking into the input with all current cources replaced by an open and all voltage sources replaced by a short. The significance of input impedance is that it provides a measure of the loading effect of the amplifier. A low input impedance translates to a poor low-frequency response and a large input power requirement. For example, Op-Amps have a very large input impedance, and therefore, a good low- frequency response and a low input power requirement. Likewise, output impedance is in general a complex quantity, but is predominantly resistive in the midband range. -

Designing a Common-Collector Amplifier

SCHOOL OF ENGINEERING AND APPLIED SCIENCE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING ECE 2115: ENGINEERING ELECTRONICS LABORATORY Tutorial #6: Designing a Common-Collector Amplifier BACKGROUND In the previous lab, you designed a common-emitter (CE) amplifier. Voltage gain (AV) is easy to achieve with this type of amplifier. As you discovered, the input impedance (Rin) of the CE amplifier is moderate- to-high (on the order of a few kΩ). The output impedance (Rout) is high (roughly the value of RC). This makes the common-emitter amplifier a poor choice for “driving” small loads. A common-collector (CC) amplifier typically has a high input impedance (typically in the hundred kΩ range) and a very low output impedance (on the order of 1Ω or 10Ω). This makes the common- collector amplifier excellent for “driving” small loads. As you discovered in Lab 6, the common-collector amplifier has a voltage gain of about 1, or unity gain. The common-collector amplifier is considered a voltage-buffer since the voltage gain is unity. The voltage signal applied at the input will be duplicated at the output; for this reason, the common-collector amplifier is typically called an emitter-follow amplifier. The common-collector amplifier can be thought of as a current amplifier. When the common-emitter amplifier is cascaded to a common-collector amplifier, the CC amplifier can be thought of as an “impedance transformer.” It can take the high output impedance of the CE amplifier and “transform” it to a low output impedance capable of driving small loads. Figure 1 shows a typical configuration for a common-collector amplifier. -

BJT Small-Signal Model

EE105 – Fall 2014 Microelectronic Devices and Circuits Prof. Ming C. Wu [email protected] 511 Sutardja Dai Hall (SDH) Lecture12-Small Signal Model-BJT 1 Introduction to Amplifiers • Amplifiers: transistors biased in the flat-part of the i-v curves – BJT: forward-active region – MOSFET: saturation region • In these regions, transistors can provide high voltage, current and power gains • Bias is provided to stabilize the operating point (the Q-Point) in the desired region of operation • Q-point also determines – Small-signal parameters of transistor – Voltage gain, input resistance, output resistance – Maximum input and output signal amplitudes – Power consumption Lecture12-Small Signal Model-BJT 2 1 Transistor Amplifiers BJT Amplifier Concept The BJT is biased in the active region by dc voltage source VBE. e.g., Q-point is set at (IC, VCE) = (1.5 mA, 5 V) with IB = 15 µA (βF = 100) Total base-emitter voltage is: vBE = VBE + vbe Collector-emitter voltage is: vCE = VCC – iCRC This is the load line equation. Lecture12-Small Signal Model-BJT 3 Transistor Amplifiers BJT Amplifier (cont.) If changes in operating currents and voltages are small enough, then iC and vCE waveforms are undistorted replicas of the input signal. A small voltage change at the base causes a large voltage change at collector. Voltage gain is given by: o Vce 1.65∠180 o Av = = o = 206∠180 = −206 8 mV peak change in vBE gives 5 mA Vbe 0.008∠0 change in iB and 0.5 mA change in iC. Minus sign indicates 180o phase 0.5 mA change in iC produces a 1.65 shift between the input and output V change in vCE .