Pin Information for the Intel® Arria® 10 10AX115 Device Version 1.6

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

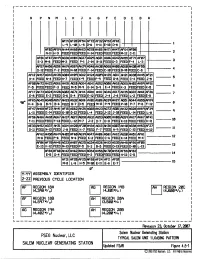

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

Connecting Bangladesh: Economic Corridor Network

Connecting Bangladesh: Economic Corridor Network Economic corridors are anchored on transport corridors, and international experience suggests that the higher the level of connectivity within and across countries, the higher the level of economic growth. In this paper, a new set of corridors is being proposed for Bangladesh—a nine-corridor comprehensive integrated multimodal economic corridor network resembling the London Tube map. This paper presents the initial results of the research undertaken as an early step of that development effort. It recommends an integrated approach to developing economic corridors in Bangladesh that would provide a strong economic foundation for the construction of world-class infrastructure that, in turn, could support the growth of local enterprises and attract foreign investment. About the Asian Development Bank COnnecTING BANGLADESH: ADB’s vision is an Asia and Pacific region free of poverty. Its mission is to help its developing member countries reduce poverty and improve the quality of life of their people. Despite the region’s many successes, it remains home to a large share of the world’s poor. ADB is committed to reducing poverty through inclusive economic growth, environmentally sustainable growth, and regional integration. ECONOMIC CORRIDOR Based in Manila, ADB is owned by 67 members, including 48 from the region. Its main instruments for helping its developing member countries are policy dialogue, loans, equity investments, guarantees, grants, NETWORK and technical assistance. Mohuiddin Alamgir -

Road Investment Strategy 2: 2020-2025

Road Investment Strategy 2: 2020–2025 March 2020 CORRECTION SLIP Title: Road Investment Strategy 2: 2020-25 Session: 2019-21 ISBN: 978-1-5286-1678-2 Date of laying: 11th March 2020 Correction: Removing duplicate text on the M62 Junctions 20-25 smart motorway Text currently reads: (Page 95) M62 Junctions 20-25 – upgrading the M62 to smart motorway between junction 20 (Rochdale) and junction 25 (Brighouse) across the Pennines. Together with other smart motorways in Lancashire and Yorkshire, this will provide a full smart motorway link between Manchester and Leeds, and between the M1 and the M6. This text should be removed, but the identical text on page 96 remains. Correction: Correcting a heading in the eastern region Heading currently reads: Under Construction Heading should read: Smart motorways subject to stocktake Date of correction: 11th March 2020 Road Investment Strategy 2: 2020 – 2025 Presented to Parliament pursuant to section 3 of the Infrastructure Act 2015 © Crown copyright 2020 This publication is licensed under the terms of the Open Government Licence v3.0 except where otherwise stated. To view this licence, visit nationalarchives.gov.uk/doc/ open-government-licence/version/3. Where we have identified any third party copyright information you will need to obtain permission from the copyright holders concerned. This publication is available at https://www.gov.uk/government/publications. Any enquiries regarding this publication should be sent to us at https://forms.dft.gov.uk/contact-dft-and-agencies/ ISBN 978-1-5286-1678-2 CCS0919077812 Printed on paper containing 75% recycled fibre content minimum. Printed in the UK by the APS Group on behalf of the Controller of Her Majesty’s Stationery Office. -

Tracer Modelling and Heat Mining Calculations for the Ahuachapan Geothermal Field El Salv Ador C.A

" Q~ The United Nations zrs: University GEOTHERMAL TRAINING PROGRAMME Reports 1996 Orkustofnun, Grensasvegur 9, Number 2 IS-108 Reykjavik, Iceland IAEA Project ELS/B/005 TRACER MODELLING AND HEAT MINING CALCULATIONS FOR THE AHUACHAPAN GEOTHERMAL FIELD EL SALV ADOR C.A. Francisco E. Montalvo L. Com isi6n Ejecutiva Hidroelectrica del Rio Lempa (C .E.L.), Centra de Investigaciones Geotermicas (C.LG.). km 11 Y2 Carretera al Puerto La Libertad, Santa Teela, La Libertad, EL SAL V ADOR C.A. ABSTRACT Nine tracer test experiments using Ill\ and one using Jl l' were carried out in the Ahuachapan geothermal field during 1987 to 1992. In only six of the tests some tracer recovery was reported ranging from 0.1 % to 28% for individual wells. In order to obtain a one-dimensional fracture flow model estimate of reservoir geometry parameters, several simulations were carried out using the TRJNV code for selected tests that show the higher tracer recovery values. The simulations provide a support for the conceptual reservoir model as the tracer velocities in the southern upflow zone of the field, are more than 10 times higher than when the tracer is injected in the north-east part, where colder downflow influences the reservoir. The results of the tracer simulations were used as input for simulating heat mining from the reservoir during long tenn injection. A reservoir parameters sensitivity study was carried out using different values of porosity, injection temperatures, formation temperatures, constant and variable injection flow rates, fracture thickness and height. Additional high pressure steam and additional thermal power recovery due to the injection were also estimated. -

Asia-Europe Connectivity Vision 2025

Asia–Europe Connectivity Vision 2025 Challenges and Opportunities The Asia–Europe Meeting (ASEM) enters into its third decade with commitments for a renewed and deepened engagement between Asia and Europe. After 20 years, and with tremendous global and regional changes behind it, there is a consensus that ASEM must bring out a new road map of Asia–Europe connectivity and cooperation. It is commonly understood that improved connectivity and increased cooperation between Europe and Asia require plans that are both sustainable and that can be upscaled. Asia–Europe Connectivity Vision 2025: Challenges and Opportunities, a joint work of ERIA and the Government of Mongolia for the 11th ASEM Summit 2016 in Ulaanbaatar, provides the ideas for an ASEM connectivity road map for the next decade which can give ASEM a unity of purpose comparable to, if not more advanced than, the integration and cooperation efforts in other regional groups. ASEM has the platform to create a connectivity blueprint for Asia and Europe. This ASEM Connectivity Vision Document provides the template for this blueprint. About ERIA The Economic Research Institute for ASEAN and East Asia (ERIA) was established at the Third East Asia Summit (EAS) in Singapore on 21 November 2007. It is an international organisation providing research and policy support to the East Asia region, and the ASEAN and EAS summit process. The 16 member countries of EAS—Brunei Darussalam, Cambodia, Indonesia, Lao PDR, Malaysia, Myanmar, Philippines, Singapore, Thailand, Viet Nam, Australia, China, India, Japan, Republic of Korea, and New Zealand—are members of ERIA. Anita Prakash is the Director General of Policy Department at ERIA. -

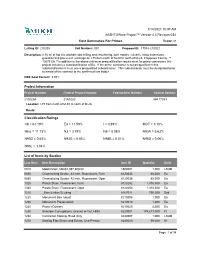

Aashtoware Project™ Version 4.4 Revision 034 1/14/2021 10:37 AM

1/14/2021 10:37 AM AASHTOWare Project™ Version 4.4 Revision 034 Cost Summaries For Primes Report v1 Letting ID: 210205 Call Number: 001 Proposal ID: 17033-210022 Description: 8.30 mi of hot mix asphalt cold milling and resurfacing, joint repairs, culverts, ramp extensions, guardrail and pavement markings on I-75 from north of M-80 to north of M-28, Chippewa County. ** 12075 Cb **In addition to the above minimum prequalification requirement for prime contractors this project includes a subclassification of Ea. If the prime contractor is not prequalified in this subclassification it must use a prequalified subcontractor. This subcontractor must be designated prior to award of the contract to the confirmed low bidder. DBE Goal Percent: 3.00% Project Information Project Number Federal Project Number Federal Item Number Control Section 210022A 21A0220 NH 17033 Location: I-75 from north of M-80 to north of M-28. Route: Classification Ratings Cb = 61.19% Ea = 11.59% I = 0.89% MOT = 3.10% Misc = 11.73% N3 = 3.79% N6 = 0.08% N93A = 5.63% N93D = 0.05% N93G = 0.85% N94B = 0.01% N95D = 0.06% N96L = 1.04% List of Items by Section Line Num Item Description Item ID Quantity Units 0010 Mobilization, Max$1,097,800.00 1500001 1.000 LSUM 0850 Channelizing Device, 42 inch, Fluorescent, Furn 8120035 65.000 Ea 0860 Channelizing Device, 42 inch, Fluorescent, Oper 8120036 65.000 Ea 1020 Plastic Drum, Fluorescent, Furn 8120252 1,310.000 Ea 1030 Plastic Drum, Fluorescent, Oper 8120253 1,310.000 Ea 1210 _Bioretention Seeding 8167011 750.000 Syd 1220 Monument Box -

Powering an I.MX 6SX-Based System Using the PF3000 PMIC

NXP Semiconductors Document Number: AN5161 Application Note Rev. 1.0, 7/2016 Powering an i.MX 6SX-based system using the PF3000 PMIC 1 Introduction Contents 1 Introduction. 1 The PF3000 is a highly integrated Power Management IC ideally suited to power NXP's i.MX 6SX, i.MX 6SL, i.MX 6S, i.MX 6DL, 2 PF3000 voltage regulators . 2 i.MX 6UL and the i.MX 7 series of applications processors. This 3 i.MX 6SX power management using the PF3000 . 3 Application Note discusses the power tree configuration for 4 PF3000 power input . 4 powering an i.MX 6SX based system using the PF3000. NXP analog ICs are manufactured using the SMARTMOS 5 PF3000 layout guidelines . 5 process, a combinational BiCMOS manufacturing flow that 6 PF3000 software support . 5 integrates precision analog, power functions and dense CMOS 7 Schematics. 6 logic together on a single cost-effective die. 8 References . 27 9 Revision history . 28 © 2016 NXP B.V. PF3000 voltage regulators 2 PF3000 voltage regulators Table 1 shows a summary of the voltage regulators in the PF3000. Output voltage and startup sequence of the regulators is programmed into the PMIC through One Time Programmable (OTP) memory. For more details, refer to the product datasheet. Table 1. PF3000 voltage regulators Regulator Output voltage range Load current rating 0.7 V to 1.425 V SW1A 1.8 V 1000 mA 3.3 V SW1B 0.7 V to 1.475 V 1750 mA 1.5 V to 1.85 V SW2 1250 mA 2.5 V to 3.3 V SW3 0.9 V to 1.65 V 1500 mA SWBST 5.0 V to 5.15 V 600 mA VSNVS 3.0 V 1.0 mA VLDO1 1.8 V to 3.3 V 100 mA VLDO2 0.8 V to 1.55 V 250 mA VLDO3 1.8 V to 3.3 V 100 mA VLDO4 1.8 V to 3.3 V 350 mA 1.8 V to 1.85 V VCC_SD 100 mA 2.85 V to 3.3 V V33 2.85 V to 3.3 V 350 mA VREFDDR VINREFDDR/2 10 mA Powering an i.MX 6SX-based system using the PF3000 PMIC, Rev. -

Grand Trunk Road Improvement Project

NATIONALHIGHWAYS AUTHORITY OFINDIA NotMm Trmk ROL" in Mncit inba (bp( M&%p&uryon) Public Disclosure Authorized Grand Trunk Road Improvement Project Environmentl Management Plan Package IVA t \' ~~N4rChzT">k Rouh5G E432 C -, Volume 10 Public Disclosure Authorized Northws Tnk Read r- 1I O iCeftury 'a , ,¢,,-t4 (G.T. Road) ;-Robad 1`44twofit S t s. / Public Disclosure Authorized l ; /h-r r' d (2007aA.d.) Propoead TrUOl4NU Mpoi -~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~- Public Disclosure Authorized / ~~FIL1E GOPY i ; _~ ss Siouth Asia Pvt. 'Ltd.- -- _ AQVS WJ 99 ........-----------..-.... .Nd SaN.VaNv 1nuinoLLsoH 5 S.C LI 99.................................... I................................................................... NION3 1 4 VICv 1, S9... --- --- ------- ------ '-'-'S3UUiOnW.S NOIUV9 ZVCL' pg.....................-........ I.......-..............----.--.-----.....-''........ ONIUM d0N'33 1 19 .-.--.--..-- ---- --- ----- --- - - W3O803NI3j B'£V' I 85'9 ',.. ,..... .------- '-'''-'-(DNWILLlH9 VHV NIELN~3o)WOUM flS0ISC 8 £ I 99. .............................-.....................-----..-..............................nS NOM Y3ON03 L£ i, -- 'oSM .S---- SMIDISI 9~£ I .ZSilO ~~~~3soo~~~~~00dI~~~~~ dYwvc1 SC £ I 19 ... s~3juINmB~ Z£C 1 Z9., . I........"I,,'-",.. - - - ........- b1V'-'sMS-flre VCV i, .- _ _ - OM-J.N3VE14IN WJN3V4NOAEN3 U0 SNLVOIO CII 94..n-------------------------- SIN3V31N33N*f~VN3 1VldAj -- Z. [K[ s., ... .. ...... .. ... .-......- ......... sno100W dN Zs -................................................................- ONMON -

Vol. 27 (T1) 2019 Vol

Pertanika Journal of Social Sciences & Humanities Vol. 27 (T1) 2019 Journal of Social Sciences & Humanities Contents Forward i Abu Bakar Salleh The Effect of Brand Equity and Perceived Value to Marketing Mix 1 Faransyah Jaya, Muhtosim Arief, Pantri Heriyati and Dyah Budiastuti Enhancing the Employability of Graduates through an Industry-led 11 Initiative Nora Zakaria and Ramesh Nair A Comparison of Customer Attendance Motivations at Victoria Park and 27 Manning Farmers’ Markets, Perth, Western Australia Mark Azavedo and John Walsh 45 Exploratory Approach Journal of Social Sciences & Humanities Sun-Hae Hyun, Moon-Kyo Seo and Se Kyung Choi Impact of Product Costing for Branding and Business Support on Small 59 and Medium Enterprises in Malaysia 27 (T1) 2019 Vol. Diana Rose Faizal, Zariyawati Mohd Ashhari, Norazlina Kamarohim and Annuar Md Nassir Establishing Green Practice Constructs among Secondary School 75 Hanifah Mahat, Nasir Nayan, Yazid Saleh, Mohmadisa Hashim and Siti Mariam Shahirah Haron Underlying Structure of Job Competency Scale in Climate-Smart 93 Agricultural Extension Service Sulaiman Umar, Norsida Man, Nolila Mohd Nawi, Ismail Abd. Latif and Bashir Garba Muktar Practiced Culture toward Firm Competitiveness Performance: Evidence 113 from Indonesia VOL. 27 (T1) 2019 Journal of Social Sciences & Humanities Prio Utomo and Dyah Budiastuti Thematic Edition Survival through Strategic Performance Measurement System in Coal 125 Mines Nandang Sukmana, Sri Bramantoro Abdinagoro and Dyah Budiastuti Management Studies Pertanika Editorial Oce, Journal Division Oce of the Deputy Vice Chancellor (R&I) 1st Floor, IDEA Tower II UPM-MTDC Technology Centre Universiti Putra Malaysia 43400 UPM Serdang Selangor Darul Ehsan Malaysia http://www.pertanika.upm.edu.my/ E-mail: [email protected] Tel: +603 8947 1622 Journal of Social Sciences & Humanities About the Journal Overview Pertanika Journal of Social Sciences & Humanities (JSSH) is the official journal of Universiti Putra Malaysia published by UPM Press. -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

Asian Highway Handbook United Nations

ECONOMIC AND SOCIAL COMMISSION FOR ASIA AND THE PACIFIC ASIAN HIGHWAY HANDBOOK UNITED NATIONS New York, 2003 ST/ESCAP/2303 The Asian Highway Handbook was prepared under the direction of the Transport and Tourism Division of the United Nations Economic and Social Commission for Asia and the Pacific. The team of staff members of the Transport and Tourism Division who prepared the Handbook comprised: Fuyo Jenny Yamamoto, Tetsuo Miyairi, Madan B. Regmi, John R. Moon and Barry Cable. Inputs for the tourism- related parts were provided by an external consultant: Imtiaz Muqbil. The designations employed and the presentation of the material in this publication do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations concerning the legal status of any country, territory, city or area or of its authorities, or concerning the delimitation of its frontiers or boundaries. This publication has been issued without formal editing. CONTENTS I. INTRODUCTION TO THE ASIAN HIGHWAY………………. 1 1. Concept of the Asian Highway Network……………………………… 1 2. Identifying the Network………………………………………………. 2 3. Current status of the Asian Highway………………………………….. 3 4. Formalization of the Asian Highway Network……………………….. 7 5. Promotion of the Asian Highway……………………………………... 9 6. A Vision of the Future………………………………………………… 10 II. ASIAN HIGHWAY ROUTES IN MEMBER COUNTRIES…... 16 1. Afghanistan……………………………………………………………. 16 2. Armenia……………………………………………………………….. 19 3. Azerbaijan……………………………………………………………... 21 4. Bangladesh……………………………………………………………. 23 5. Bhutan…………………………………………………………………. 27 6. Cambodia……………………………………………………………… 29 7. China…………………………………………………………………... 32 8. Democratic People’s Republic of Korea……………………………… 36 9. Georgia………………………………………………………………... 38 10. India…………………………………………………………………… 41 11. Indonesia………………………………………………………………. 45 12. Islamic Republic of Iran………………………………………………. 49 13 Japan………………………………………………………………….. -

PPP Resources for Treasure Coast Businesses

PPP Resources for Treasure Coast Businesses Nine Practical Steps 1. Find the The Laws • H.R. 748 = CARES Act; PPP = Sections 1101, 1102 and 1106 • 1101, 1102 = PPP definition • 1106 = Loan Forgiveness • H.R. 266 = PPP & HCE Act • H.R. 7010 = PPPFA 2. See what the agencies say 3. Google PPP FAQ… 48 as of this writing 4. Keep up with Interim Final Rules CARES Act - PPP Interim Final Rules • Google: 3245-AH34, SBA unless otherwise noted Federal 3245-AH35, 3245-AH36, RIN Register Page Effective Date 1st 3245-AH34 20811 4/15/20 2nd 3245-AH35 20817 4/15/20 etc. 3rd 3245-AH36 21747 4/20/20 4th 3245-AH37 23450 4/28/20 Treasury #1 1505-AC67 23917 4/30/20 AND 5th 3245-AH38 26321 5/4/20 6th 3245-AH39 26324 5/4/20 1505-AC67, 1505-AC69, 7th 3245-AH40 27287 5/8/20 8th 3245-AH41 29845 5/19/20 9th 3245-AH42 29842 5/19/20 etc. 10th 3245-AH43 29847 5/19/20 11th 3245-AH44 30835 5/21/20 12th 3245-AH45 31357 5/26/20 13th 3245-AH46 33004 5/28/20 Treasury #2 1505-AC69 33004 5/28/20 14th 3245-AH47 33010 5/28/20 15th 3245-AH48 pending publication 16th 3245-AH49 17th 3245-AH50 5. UH -OH… “We’re from the IRS and we’re here to help” IRS Notice 2020-32 • PPP says loan forgiveness is tax exempt, but… • Expenses paid by loan forgiveness are NON-DEDUCTIBLE. • Was this the legislative intent? • Congress chose not to address this issue in PPPFA.