MPC8572E Powerquicc III Integrated Processor Hardware Specifications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Tracer Modelling and Heat Mining Calculations for the Ahuachapan Geothermal Field El Salv Ador C.A

" Q~ The United Nations zrs: University GEOTHERMAL TRAINING PROGRAMME Reports 1996 Orkustofnun, Grensasvegur 9, Number 2 IS-108 Reykjavik, Iceland IAEA Project ELS/B/005 TRACER MODELLING AND HEAT MINING CALCULATIONS FOR THE AHUACHAPAN GEOTHERMAL FIELD EL SALV ADOR C.A. Francisco E. Montalvo L. Com isi6n Ejecutiva Hidroelectrica del Rio Lempa (C .E.L.), Centra de Investigaciones Geotermicas (C.LG.). km 11 Y2 Carretera al Puerto La Libertad, Santa Teela, La Libertad, EL SAL V ADOR C.A. ABSTRACT Nine tracer test experiments using Ill\ and one using Jl l' were carried out in the Ahuachapan geothermal field during 1987 to 1992. In only six of the tests some tracer recovery was reported ranging from 0.1 % to 28% for individual wells. In order to obtain a one-dimensional fracture flow model estimate of reservoir geometry parameters, several simulations were carried out using the TRJNV code for selected tests that show the higher tracer recovery values. The simulations provide a support for the conceptual reservoir model as the tracer velocities in the southern upflow zone of the field, are more than 10 times higher than when the tracer is injected in the north-east part, where colder downflow influences the reservoir. The results of the tracer simulations were used as input for simulating heat mining from the reservoir during long tenn injection. A reservoir parameters sensitivity study was carried out using different values of porosity, injection temperatures, formation temperatures, constant and variable injection flow rates, fracture thickness and height. Additional high pressure steam and additional thermal power recovery due to the injection were also estimated. -

Vol. 27 (T1) 2019 Vol

Pertanika Journal of Social Sciences & Humanities Vol. 27 (T1) 2019 Journal of Social Sciences & Humanities Contents Forward i Abu Bakar Salleh The Effect of Brand Equity and Perceived Value to Marketing Mix 1 Faransyah Jaya, Muhtosim Arief, Pantri Heriyati and Dyah Budiastuti Enhancing the Employability of Graduates through an Industry-led 11 Initiative Nora Zakaria and Ramesh Nair A Comparison of Customer Attendance Motivations at Victoria Park and 27 Manning Farmers’ Markets, Perth, Western Australia Mark Azavedo and John Walsh 45 Exploratory Approach Journal of Social Sciences & Humanities Sun-Hae Hyun, Moon-Kyo Seo and Se Kyung Choi Impact of Product Costing for Branding and Business Support on Small 59 and Medium Enterprises in Malaysia 27 (T1) 2019 Vol. Diana Rose Faizal, Zariyawati Mohd Ashhari, Norazlina Kamarohim and Annuar Md Nassir Establishing Green Practice Constructs among Secondary School 75 Hanifah Mahat, Nasir Nayan, Yazid Saleh, Mohmadisa Hashim and Siti Mariam Shahirah Haron Underlying Structure of Job Competency Scale in Climate-Smart 93 Agricultural Extension Service Sulaiman Umar, Norsida Man, Nolila Mohd Nawi, Ismail Abd. Latif and Bashir Garba Muktar Practiced Culture toward Firm Competitiveness Performance: Evidence 113 from Indonesia VOL. 27 (T1) 2019 Journal of Social Sciences & Humanities Prio Utomo and Dyah Budiastuti Thematic Edition Survival through Strategic Performance Measurement System in Coal 125 Mines Nandang Sukmana, Sri Bramantoro Abdinagoro and Dyah Budiastuti Management Studies Pertanika Editorial Oce, Journal Division Oce of the Deputy Vice Chancellor (R&I) 1st Floor, IDEA Tower II UPM-MTDC Technology Centre Universiti Putra Malaysia 43400 UPM Serdang Selangor Darul Ehsan Malaysia http://www.pertanika.upm.edu.my/ E-mail: [email protected] Tel: +603 8947 1622 Journal of Social Sciences & Humanities About the Journal Overview Pertanika Journal of Social Sciences & Humanities (JSSH) is the official journal of Universiti Putra Malaysia published by UPM Press. -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

Europe Price List

2019 Europe Price List EUROPE PRICE LIST 2019 Terms and Conditions of Sale Conditions générales de vente Condizioni generali di vendita Allgemeine Verkaufsbedingungen By placing an order, the customer Toutes les commandes passées Tutti gli ordini effettuati com- Mit Aufgabe einer Bestellung er- fully accepts the following Terms impliquent que l’acheteur accep- portano la piena accettazione, kennt der Kunde die folgenden and Conditions of Sale: te intégralement les Conditions da parte dell’acquirente, delle Allgemeinen Verkaufsbedingun- générales de vente suivantes : seguenti Condizioni Generali di gen in vollem Umfang an: 0. Validity Vendita: Price list valid from 18/02/2019. 0. Validité 0. Gültigkeit Tarif valable à partir de 18/02/2019. 0. Validità Die Preisliste gilt ab dem 1. Prices Listino valido dal 18/02/2019. 18/02/2019. The prices applied will be those 1. Prix valid on the date of reception of Les tarifs en vigueur s’appliquent 1. Prezzi 1. Preise the order (RRP, VAT not included). à la date de réception de la com- Verranno applicate le tariffe Es werden die Preise berechnet, All prices featured in the price list mande (prix PVPR, TVA non com- vigenti alla data di ricezione die am Tag des Auftrageingangs include the WEEE eco-fee. prise). Tous les prix indiqués dans dell’ordine (prezzi di vendita al gelten (UVP ohne Mehrwerts- la liste des tarifs comprennent pubblico consigliati, IVA esclusa). teuer). Alle angegebenen Preise 2. Delivery times l’éco-participation DEEE. Tutti i prezzi indicati nel listino sind einschließlich WEEE Gebühr. Delivery times will be confirmed at prezzi sono con contributo ECO- the moment of placing the order 2. -

Leds-C4 2018 Inicio 9 Fevereiro.Pdf

TARIFA P. V.P.R TARIFA 2018 - P. V.P.R Condiciones generales de venta Todos los pedidos cursados implican la aceptación un error de suministro por parte de la empresa, integra, por parte del comprador, de las siguientes corriendo los portes a cargo de ésta. Condiciones Generales de Venta: 6. Abonos 0. Validez Los abonos que por diversas causas se puedan Tarifa válida a partir del 9/02/2018. producir serán descontados de la primera factura que se origine (o se enviará un cheque bancario al 1. Precios cliente), siempre que el cliente esté al corriente de Se aplicarán las tarifas vigentes en la fecha de sus obligaciones de pago. recepción del pedido (precios P.V.P.R., IVA no incluido). 7. Muestras Las muestras de material deberán ser solicitadas 2. Plazos mediante pedido y serán facturadas. En el caso de Los plazos de entrega se confirmarán en el que sean devueltas (portes a cargo del comprador) momento de cursar el pedido y serán siempre a y la mercancía esté en perfecto estado, el importe título orientativo. correspondiente será pertinentemente abonado. 3. Transporte 8. Jurisdicción Para pedidos superiores a 360 € (importe neto), En caso de litigio, se considerarán competentes la mercancía viajará a portes pagados (en los Juzgados y Tribunales de Cervera (Lleida), península). Para pedidos por un importe inferior renunciando el comprador a su propio fuero de se cargará en factura 10 €, viajando la mercancía conformidad con lo dispuesto en el artículo 55 de a portes pagados hasta destino (en península). la L.E.C. El transporte se realizará a través de nuestra agencia de transporte habitual. -

Pin Information for the Intel® Arria® 10 10AX115 Device Version 1.6

Pin Information for the Intel® Arria® 10 10AX115 Device Version 1.6 Bank Index within I/O Bank (1) VREF Pin Name/Function Optional Function(s) Configuration Dedicated Tx/Rx Soft CDR Support HF34 DQS for X4 DQS for X8/X9 DQS for X16/X18 DQS for X32/X36 Number Function Channel 1F REFCLK_GXBL1F_CHTp M28 1F REFCLK_GXBL1F_CHTn M27 1F GXBL1F_TX_CH5n B31 1F GXBL1F_TX_CH5p B32 1F GXBL1F_RX_CH5n,GXBL1F_REFCLK5n C29 1F GXBL1F_RX_CH5p,GXBL1F_REFCLK5p C30 1F GXBL1F_TX_CH4n D31 1F GXBL1F_TX_CH4p D32 1F GXBL1F_RX_CH4n,GXBL1F_REFCLK4n E29 1F GXBL1F_RX_CH4p,GXBL1F_REFCLK4p E30 1F GXBL1F_TX_CH3n F31 1F GXBL1F_TX_CH3p F32 1F GXBL1F_RX_CH3n,GXBL1F_REFCLK3n G29 1F GXBL1F_RX_CH3p,GXBL1F_REFCLK3p G30 1F GXBL1F_TX_CH2n H31 1F GXBL1F_TX_CH2p H32 1F GXBL1F_RX_CH2n,GXBL1F_REFCLK2n J29 1F GXBL1F_RX_CH2p,GXBL1F_REFCLK2p J30 1F GXBL1F_TX_CH1n C33 1F GXBL1F_TX_CH1p C34 1F GXBL1F_RX_CH1n,GXBL1F_REFCLK1n K31 1F GXBL1F_RX_CH1p,GXBL1F_REFCLK1p K32 1F GXBL1F_TX_CH0n E33 1F GXBL1F_TX_CH0p E34 1F GXBL1F_RX_CH0n,GXBL1F_REFCLK0n L29 1F GXBL1F_RX_CH0p,GXBL1F_REFCLK0p L30 1F REFCLK_GXBL1F_CHBp P28 1F REFCLK_GXBL1F_CHBn P27 1E REFCLK_GXBL1E_CHTp T28 1E REFCLK_GXBL1E_CHTn T27 1E GXBL1E_TX_CH5n G33 1E GXBL1E_TX_CH5p G34 1E GXBL1E_RX_CH5n,GXBL1E_REFCLK5n M31 1E GXBL1E_RX_CH5p,GXBL1E_REFCLK5p M32 1E GXBL1E_TX_CH4n J33 1E GXBL1E_TX_CH4p J34 1E GXBL1E_RX_CH4n,GXBL1E_REFCLK4n N29 1E GXBL1E_RX_CH4p,GXBL1E_REFCLK4p N30 1E GXBL1E_TX_CH3n L33 1E GXBL1E_TX_CH3p L34 1E GXBL1E_RX_CH3n,GXBL1E_REFCLK3n P31 1E GXBL1E_RX_CH3p,GXBL1E_REFCLK3p P32 1E GXBL1E_TX_CH2n N33 1E GXBL1E_TX_CH2p N34 1E GXBL1E_RX_CH2n,GXBL1E_REFCLK2n -

The Effect of Road Upgrading to Overland Trade in Asian Highway Network Ziyodullo PARPIEV ∗ Jamshid SODIKOV **

Eurasian Journal of Business and Economics 2008, 1 (2), 85-101. The Effect of Road Upgrading to Overland Trade in Asian Highway Network Ziyodullo PARPIEV ∗ Jamshid SODIKOV ** Abstract This paper investigates an impact of road upgrading and improvement on overland trade in 18 out of 32 Asian Highway Network member countries. A regression based cost model was developed. The results indicate that approximately 6.5 billion US dollars is required to upgrade and improve surface condition of the selected roads with total length of 15,842 km. The gravity model approach was adopted to quantitatively evaluate overland trade expansion assuming pessimistic and optimistic scenarios: improvements in road quality indices up to 50 and up to 75, respectively. The results suggests that in the first scenario total intra-regional trade will increase by about 20 percent or 48.7 billion US dollars annually, while second scenario predicts that trade will increase by about 35 percent or 89.5 billion US dollars annually. Keywords: Asian Highway Network, road transport, gravity model. Jel Classification: F12, F15, F17. ∗ Advisor-Economist, UNDP Uzbekistan Country Office, Email: [email protected] ** Chief Engineer, Road Research Institute, Tashkent, Uzbekistan The views expressed in this paper are those of the author(s) and do not necessarily represent those of organizations the authors are associated with. Ziyodullo PARPIEV & Jamshid SODIKOV 1. Introduction In 1992, the United Nations Economic and Social Commission for Asia and the Pacific (ESCAP) endorsed the Asian Land Transport Infrastructure Development (ALTID) project comprising of the Asian Highway and the Trans-Asian Railway network. The formalization of the Asian Highway, through the Intergovernmental Agreement on Asian Highway Network (AHN), was adopted in November 2003. -

Growing Together Articulates a Number of Proposals That Can Help the Region Exploit Its Huge Untapped Potential for Regional Economic Integration

i Photo by Warren Field ii FOREWORD For the global economy, these are difficult times. The world is emerging from a crisis whose aftershocks continue to resonate – trapping some of the richest economies in recession and shaking the foundations of one of the world’s major currencies. Here at ESCAP, there are historical echoes. What is now the Economic and Social Commission for Asia and the Pacific was founded more than 60 years ago – also in the aftermath of a global crisis. The countries of Asia and the Pacific established their new Commission partly to assist them in rebuilding their economies as they came out of the yoke of colonialism and the Second World War. The newly established ECAFE, as ESCAP was called then, held a ministerial conference on regional economic cooperation in 1963 that resolved to set up the Asian Development Bank with the aim of assisting the countries in the region in rebuilding their economies. Fifty years later, the Asia-Pacific region is again at a crossroads, on this occasion seeking ways and means to sustain its dynamism in a dramatically changed global context in the aftermath of a global financial and economic crisis. An important change is the fact that, burdened by huge debts and global imbalances, the advanced economies of the West are no longer able to play the role of engines of growth for the Asia-Pacific region that they played in the past. Hence, the Asia-Pacific region has to look for new engines of growth. The secretariat of ESCAP has argued over the past few years that regional developmental challenges, such as poverty and wide disparities in social and physical infrastructure, can be turned into opportunities for sustaining growth in the future. -

Asian Highway Handbook

ECONOMIC AND SOCIAL COMMISSION FOR ASIA AND THE PACIFIC ASIAN HIGHWAY HANDBOOK UNITED NATIONS New York, 2003 ST/ESCAP/2303 The Asian Highway Handbook was prepared under the direction of the Transport and Tourism Division of the United Nations Economic and Social Commission for Asia and the Pacific. The team of staff members of the Transport and Tourism Division who prepared the Handbook comprised: Fuyo Jenny Yamamoto, Tetsuo Miyairi, Madan B. Regmi, John R. Moon and Barry Cable. Inputs for the tourism- related parts were provided by an external consultant: Imtiaz Muqbil. The designations employed and the presentation of the material in this publication do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations concerning the legal status of any country, territory, city or area or of its authorities, or concerning the delimitation of its frontiers or boundaries. This publication has been issued without formal editing. CONTENTS I. INTRODUCTION TO THE ASIAN HIGHWAY………………. 1 1. Concept of the Asian Highway Network……………………………… 1 2. Identifying the Network………………………………………………. 2 3. Current status of the Asian Highway………………………………….. 3 4. Formalization of the Asian Highway Network……………………….. 7 5. Promotion of the Asian Highway……………………………………... 9 6. A Vision of the Future………………………………………………… 10 II. ASIAN HIGHWAY ROUTES IN MEMBER COUNTRIES…... 16 1. Afghanistan……………………………………………………………. 16 2. Armenia……………………………………………………………….. 19 3. Azerbaijan……………………………………………………………... 21 4. Bangladesh……………………………………………………………. 23 5. Bhutan…………………………………………………………………. 27 6. Cambodia……………………………………………………………… 29 7. China…………………………………………………………………... 32 8. Democratic People’s Republic of Korea……………………………… 36 9. Georgia………………………………………………………………... 38 10. India…………………………………………………………………… 41 11. Indonesia………………………………………………………………. 45 12. Islamic Republic of Iran………………………………………………. 49 13 Japan………………………………………………………………….. -

ASIAN HIGHWAY ROUTE MAP 500 Km

40° E 60° E 80° E 100° E 120° E 140° E 500 Km. Vyborg Torpynovka 60° N St. Petersburg ASIAN HIGHWAY ROUTE MAP 500 Km. 60° N RUSSIAN FEDERATION AH8 Yekaterinburg AH7 AH6 Moscow AH6 AH6 Krasnoyarsk AH6 Ufa Petuhovo AH6 Chelyabinsk E30 Chistoe Isilkul AH6 Omsk Novosibirsk E30 AH60 Krasnoe Petropavlovsk Karakuga E30 AH4 AH8 Troisk AH6 Samara Cherlak E119 Kaerak AH7 AH62 Pnirtyshskoe E30 Kostanai AH64 Barnaul AH30 E123 Kokshetau AH60 AH30 E125 AH63 E127 Tambov E121 Pavlodar AH64 Irkutsk Ulan-Ude Borysoglebsk Saratov Kurlin AH7 AH64 Chita Kursk AH61 Pogodaevo AH60 AH6 Ozinki AH64 (AH64) AH6 E38 Shiderty (AH67) AH3 AH61 Voronezh Ural'sk AH62 Astana E127 Veseloyarskyj AH4 AH6 Krupets Kamenka AH7 (AH67) Belogorsk E38 AH8 Zhaisan E123 Krasny Aul E119 E125 Kyahta AH61 Arkalyk AH67 Semipalatinsk Heihe AH63 Altanbulag Zabaykalsk Blagoveshchensk E38 Aktobe Karabutak Karaganda AH60 E121 Tashanta (AH67) Ulaanbaishint Darkhan Georgievka AH3 Manzhouli AH30 Volgograd AH61 AH4 AH6 Donetsk AH70 E38 AH67 Khabarovsk AH32 E40 E40 AH60 (AH67) Ulaanbaatar Nalayh AH8 AH7 Hovd AH32 Sumber Arshan E119 Zhezkazgan AH32 Qiqihar AH31 Tongjiang (AH70) Atyrau AH63 E125 Taskesken Choybalsan (AH70) KAZAKHSTAN Uliastay Kotyaevka AH70 E105 Numrug Port of Odessa E40 Aralsk Baketu Ondorhaan AH62 Bakhty AH35 AH33 Astrakhan E121 E123 AH67 Takeshkan Choir Ucharal AH3 AH32 E40 AH68 MONGOLIA Yarantai Harbin AH30 Beyneu E014 Dostyk Bichigt E119 Kyzylorda AH60 AH8 Burubaital Alatawshankou AH4 E40 AH35 Daut-ota Saynshand AH6 AH60 AH5 AH31 Pogranichny AH70 AH5 Port of Constantza 500 -

Pub 2424 Fulltext 0.Pdf

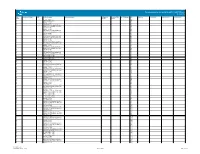

ESCAP is the regional development arm of the United Nations and serves as the main economic and social development centre for the United Nations in Asia and the Pacific. Its mandate is to foster cooperation between its 53 members and 9 associate members. ESCAP provides the strategic link between global and country-level programmes and issues. It supports Governments of the region in consolidating regional positions and advocates regional approaches to meeting the region’s unique socio-economic challenges in a globalizing world. The ESCAP office is located in Bangkok, Thailand. Please visit our website at www.unescap.org for further information. The shaded areas of the map indicate ESCAP members and associate members. ECONOMIC AND SOCIAL COMMISSION FOR ASIA AND THE PACIFIC Priority Investment Needs for the Development of the Asian Highway Network United Nations New York, 2006 ST/ESCAP/2424 This publication was prepared under the direction of the Transport and Tourism Division of the Economic and Social Commission for Asia and the Pacific. Inputs related to priority investment needs and projects were provided by national experts and representatives of member countries at three subregional expert group meetings. The designations employed and the presentation of the material in this publication do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations concerning the legal status of any country, territory, city or area, or of its authorities, or the delineation of its frontiers or boundaries. This publication has been issued without formal editing. ii CONTENTS Page INTRODUCTION ................................................................................................................................... 1 I. STATUS OF THE ASIAN HIGHWAY NETWORK ................................................................. -

Natural Capital Approaches for Sustainable Development

Natural Capital Approaches for Sustainable Development Emily McKenzie Chief Adviser, Economics and Sustainability © Anton Vorauer / WWF Outline 1. Natural capital and the SDGs 2. The case of Myanmar 3. What tools are available? 4. Natural capital in business decisions 2 27-Jun-17 1 Natural Capital and the SDGs © BRANDON COLE/WWW.NATUREPL.COM 2 5 27-Jun-17 © Azote Images for Stockholm Resilience Centre 6 What is natural capital? Natural Capital is the stock of renewable and non-renewable natural resources, (e.g. plants, animals, air, water, soils, minerals) that combine to yield a flow of benefits to people Food, fuel, fiber Climate Pollination regulation Coastal Clean protection water Spiritual Fulfilment 7 27-Jun-17 8 Multiple forms of capital Financial capital Manufactured capital Intellectual Human capital capital Social and relationship capital Natural capital <IR> capitals framework 9 10 11 12 13 Millennium Ecosystem Assessment • 60% of ecosystem services are being degraded or used unsustainably • Degradation of ecosystem services causes significant harm to human well-being 14 27-Jun-17 © Christy Williams / WWF Sustainable Securing Sustainable, Standards for Safe, Resilient Development Freshwater Livable Cities the Private Coastal Planning Sector Communities Working together to account for nature’s values, toward shared outcomes THEORY OF CHANGE Robust evidence of Build and tell Create user-friendly conditions for success stories, approaches & tools success engage leaders Get information about natural capital into decisions Make decisions