Lab 2: Common Source Amplifier

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET Datasheet

JFE150 SLPS732 – JUNE 2021 JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET 1 Features and yields excellent noise performance for currents from 50 μA to 20 mA. When biased at 5 mA, the • Ultra-low noise: device yields 0.8 nV/√Hz of input-referred noise, – Voltage noise: giving ultra-low noise performance with extremely high input impedance (> 1 TΩ). The JFE150 also • 0.8 nV/√Hz at 1 kHz, IDS = 5 mA features integrated diodes connected to separate • 0.9 nV/√Hz at 1 kHz, IDS = 2 mA – Current noise: 1.8 fA/√Hz at 1 kHz clamp nodes to provide protection without the addition • Low gate current: 10 pA (max) of high leakage, nonlinear external diodes. • Low input capacitance: 24 pF at VDS = 5 V The JFE150 can withstand a high drain-to-source • High gate-to-drain and gate-to-source breakdown voltage of 40-V, as well as gate-to-source and gate- voltage: –40 V to-drain voltages down to –40 V. The temperature • High transconductance: 68 mS range is specified from –40°C to +125°C. The device • Packages: Small SC70 and SOT-23 (Preview) is offered in 5-pin SOT-23 and SC-70 packages. 2 Applications Device Information • Microphone inputs PART NUMBER PACKAGE(1) BODY SIZE (NOM) • Hydrophones and marine equipment SOT-23 (5) - Preview 2.90 mm × 1.60 mm JFE150 • DJ controllers, mixers, and other DJ equipment SC-70 (5) 2.00 mm × 1.25 mm • Professional audio mixer or control surface • Guitar amplifier and other music instrument (1) For all available packages, see the package option addendum at the end of the data sheet. -

Experiment #6- Part-1 the FET Common Source Amplifier

University of Anbar Lab. Name: Electronic I Experiment no.: 7 College of Engineering Lab. Supervisor: Munther N. Thiyab Dept. of Electrical Engineering Experiment #6- Part-1 The FET Common Source Amplifier Object The purpose of this experiment is to test the performance of the common source amplifier using the self-bias circuit. Required Parts and Equipment's 1. Electronic Test Board. (M110) 2. Dual Polarity Variable DC Power Supply 3. Digital Multimeters. 4. Dual-Channel Oscilloscope. 5. Function Generator. 6. N-Channel JFET 2N3823 7. Resistors, R5=100KΩ, R6=10KΩ, R8=1KΩ, R7=2.2KΩ Theory The common source amplifier configuration is widely used amongst other JFET configurations and can provide both high voltages gain and large input impedance. In this configuration, the input signal is applied to the gate and the output signal is taken from the drain, while the source terminal being the reference or common. In order to work as an amplifier, the JFET should be properly biased by setting the gate-source voltage which results in the required drain current. The N-channel JFET requires that the gate-source voltage always be less negative than the pinch-off voltage, but less than zero. Since virtually no gate current flows due to the JFET’s high input impedance, the gate voltage is essentially at ground level. Consequently, using only a drain-supply voltage, the required negative quiescent gate-source voltage is developed by the voltage drop across the source resistor of the self-bias circuit shown in Fig.1. This circuit is one of the simplest and practical bias circuits for JFET amplifiers in which a single power supply is used. -

Lecture 24 Multistage Amplifiers (I) MULTISTAGE AMPLIFIER

Lecture 24 Multistage Amplifiers (I) MULTISTAGE AMPLIFIER Outline 1. Introduction 2. CMOS multi-stage voltage amplifier 3. BiCMOS multistage voltage amplifier 4. BiCMOS current buffer 5. Coupling amplifier stages Reading Assignment: Howe and Sodini, Chapter 9, Sections 9-1-9.3 6.012 Spring 2007 Lecture 24 1 1. Introduction Most often, single stage amplifier does not accomplish design goals: • Need more gain than could be provided by a single stage • Need to adapt to specified RS and RL to maximize efficiency ⇒ Multistage amplifier VBIAS Issues: • What amplifying stages should be used and in what order? • What devices should be used, BJT or MOSFET? • How is biasing to be done? 6.012 Spring 2007 Lecture 24 2 Summary of single stage amplifier characteristics Key Stage A , A R R vo io in out Function Common Transcon- ∞ ro // roc ductance Source Avo =−gm(ro //roc) amplifier Common gm 1 Voltage Avo ≈ ∞ Drain gm + gmb gm + gmb Buffer Current Common A ≈ −1 1 r //[r (1+ g R )] io oc o m S buffer Gate gm + gmb Common Transcon- Avo=−gm(ro//roc) r Emitter π ro // roc ductance amplifier Common 1 RS Voltage Avo ≈1 rπ + βo (ro // roc // RL ) + Collector gm βo buffer Common Current Aio ≈ −1 1 r //[r (1+ g ()r // R )] oc o m π S buffer Base gm Differences between BJT’s and MOSFETs BJT MOSFET βo rπ = gmb ∝ gm gm IC W gm = > gm = 2 µCox ID Vth L VA 1 ro = > ro = IC λI D 6.012 Spring 2007 Lecture 24 3 2. CMOS Multistage Voltage Amplifier Goals: • High voltage gain, Avo • High input resistance, Rin • Low output resistance, Rout Good starting point: Common-Source stage: •Rin=∞ •Avo=-gm(ro//roc), probably insufficient •Rout= (ro//roc), too high 6.012 Spring 2007 Lecture 24 4 CMOS Multistage Voltage Amplifier (contd.) Add second CS stage to get more gain: •Rin=∞ •Avo=gm1(ro1//roc1) gm2(ro2//roc2) •Rout= (ro2//roc2), still too high Add CD stage at output (to reduce Rout): •Rin=∞ gm3 • Avo = gm1()ro1 || roc1 gm2()ro2 || roc2 1 gm3 + gmb3 • Rout = gm3 + gmb3 6.012 Spring 2007 Lecture 24 5 3. -

Common Gate Amplifier

© 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company COMMON GATE AMPLIFIER • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Common Gate Amplifier A common-gate amplifier is one of three basic single-stage field-effect transistor (FET) amplifier topologies, typically used as a current buffer or voltage amplifier. In the circuit the source terminal of the transistor serves as the input, the drain is the output and the gate is connected to ground, or common, hence its name. The analogous bipolar junction transistor circuit is the common-base amplifier. Input signal is applied to the source, output is taken from the drain. current gain is about unity, input resistance is low, output resistance is high a CG stage is a current buffer. It takes a current at the input that may have a relatively small Norton equivalent resistance and replicates it at the output port, which is a good current source due to the high output resistance. • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Circuit Topology • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Waveforms Input Voltage Output Voltage • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company The common-source and common-drain configurations have extremely high input resistances because the gate is the input terminal. In contrast, the common-gate configuration where the source is the input terminal has a low input resistance. Common gate FET configuration provides a low input impedance while offering a high output impedance. -

Lecture 20 Transistor Amplifiers (II) Other Amplifier Stages

Lecture 20 Transistor Amplifiers (II) Other Amplifier Stages Outline • Common-drain amplifier • Common-gate amplifier Reading Assignment: Howe and Sodini; Chapter 8, Sections 8.7-8.9 6.012 Spring 2007 1 1. Common-drain amplifier VDD signal source RS signal vs + load iSUP RL vOUT VBIAS - VSS • A voltage buffer takes the input voltage which may have a relatively large Thevenin resistance and replicates the voltage at the output port, which has a low output resistance • Input signal is applied to the gate • Output is taken from the source • To first order, voltage gain ≈ 1 • Input resistance is high • Output resistance is low – Effective voltage buffer stage How does it work? •vgate ↑⇒ iD cannot change ⇒ vsource ↑ – Source follower 6.012 Spring 2007 2 Biasing the Common-drain amplifier VDD signal source RS VSS signal + load vs iSUP RL vOUT VBIAS - VSS • Assume device in saturation; neglect RS and RL; neglect CLM (λ = 0) • Obtain desired output bias voltage – Typically set VOUT to”halfway” between VSS and VDD. • Output voltage maximum VDD-VDSsat • Output voltage minimum set by voltage requirement across ISUP. VBIAS = VGS + VOUT I V = V (V ) + SUP GS Tn SB W µ C 2L n ox 6.012 Spring 2007 3 Small-signal Analysis Unloaded small-signal equivalent circuit model: D G + gmvgs ro S vin + roc vout - - + vgs - + + vin gmvgs ro//roc vout - - vin = vgs + vout vout = gmvgs(ro // roc ) Then: g A m 1 vo = 1 ≈ gm + ro // roc 6.012 Spring 2007 4 Input and Output Resistance Input Impedance : Rin = ∞ Output Impedance: i + v - t + gs + RS vin gmvgs ro//roc vt -

Lecture 17: Common Source/Gate/Drain Amplifiers

EECS 105 Fall 2003, Lecture 17 Lecture 17: Common Source/Gate/Drain Amplifiers Prof. Niknejad Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Lecture Outline MOS Common Source Amp Current Source Active Load Common Gate Amp Common Drain Amp Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Common-Source Amplifier Isolate DC level Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Load-Line Analysis to find Q V −V I = DD out RD RD Q 1 5V slope = I = 10k D 10k 0V I = D 10k Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Small-Signal Analysis =∞ Rin Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Two-Port Parameters: Generic Transconductance Amp Rs + vs Rin Gmvin RL vin Rout − Find Rin, Rout, Gm =∞ Rin = = Gm gm RrRout o|| D Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Two-Port CS Model Reattach source and load one-ports: Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. A. Niknejad Maximize Gain of CS Amp =− AgRrv mD|| o Increase the gm (more current) Increase RD (free? Don’t need to dissipate extra power) Limit: Must keep the device in saturation =− > VVIRVDS DD D D DS, sat For a fixed current, the load resistor can only be chosen so large To have good swing we’d also like to avoid getting to close to saturation Department of EECS University of California, Berkeley EECS 105 Fall 2003, Lecture 17 Prof. -

A Comparison Between Common-Source and Cascode Topologies for 60Ghz Amplifier Design in 65Nm CMOS Qinghong Bu, Ning Li, Kenichi Okada and Akira Matsuzawa

A Comparison between Common-source and Cascode Topologies for 60GHz Amplifier Design in 65nm CMOS Qinghong Bu, Ning Li, Kenichi Okada and Akira Matsuzawa Department of Physical Electronics, Tokyo Institute of Technology 2-12-1-S3-27 Ookayama, Meguro-ku, Tokyo, 152-8552, Japan. Tel & Fax: +81-3-5734-3764, E-mail: [email protected] voltage Vdd are the 1.2 V. Fig. 2 (a) shows that the maxi- 1. Introduction mum gain of the cascode topology decreased faster than the Although RF front-end amplifiers are implemented at CS topology as the frequency increases. The same maxi- low noise amplifiers and power amplifiers with different mum gain can be obtained around 60 GHz. The gain-boost specifications due to the different functions they perform, cascode topology achieves a 3-dB higher maximum gain sufficient gain and low power consumption are the general than the CS and the common cascode topologies. Both the requirements. For the design consideration, the active de- cascode topology and the gain-boost cascode topology have vice structure and models should be optimized at 60 GHz. about -30dB reverse isolation at 60GHz while the reverse Both common-source (CS) and cascode topologies are isolation of CS topology is only -13dB at 60GHz as shown utilized in millimeter-wave (MMW) circuit design. CS to- in Fig. 2(b). The stability factor is shown in Fig. 2(c). pology, which has reasonable power gain and small noise Common cascode topology and the gain-boost cascode figure, is widely used in MMW amplifier designs. The topology have much better stability factor than the CS to- good isolation between input and output of cascode topol- pology at 60GHz. -

CMOS Inverter As Analog Circuit: an Overview

Journal of Low Power Electronics and Applications Review CMOS Inverter as Analog Circuit: An Overview Woorham Bae 1,2 1 Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA 94720, USA; [email protected] 2 Ayar Labs, Santa Clara, CA 95054, USA Received: 24 June 2019; Accepted: 17 August 2019; Published: 20 August 2019 Abstract: Since the CMOS technology scaling has focused on improving digital circuit, the design of conventional analog circuits has become more and more difficult. To overcome this challenge, there have been a lot of efforts to replace conventional analog circuits with digital implementations. Among those approaches, this paper gives an overview of the latest achievement on utilizing a CMOS inverter as an analog circuit. Analog designers have found that a simple resistive feedback pulls a CMOS inverter into an optimum biasing for analog operation. Recently developed applications of the resistive-feedback inverter, including CMOS inverter as amplifier, high-speed buffer, and output driver for high-speed link, are introduced and discussed in this paper. Keywords: analog; analog and mixed signal; amplifier; CMOS; driver; high-speed buffer; high-speed I/O; Integrated circuit; Inverter 1. Introduction Since the 1960s, scaling of silicon technologies (Moore’s law) has dominantly driven the semiconductor industry, as the scaling is actually the almighty knob for all the challenges we have had; lower power consumption, higher speed, and higher density. However, the main focus of the scaling has been the improvement of digital circuit, for example high Ion/Ioff ratio, as the computing capability has been constrained by the power consumption, instead of the speed of the transistor [1,2]. -

EE 501 Lab 1 Exploring Transistor Characteristics and Design Common-Source Amplifiers

EE 501 Lab 1 Exploring Transistor Characteristics and Design Common-Source Amplifiers Lab report due on September 11, 2014 Objectives: 1. Be familiar with characteristics of MOSFET such as gain, speed, power, transconductance, output impedance and etc. 2. Explore how MOSFET I-V curves, gm, gds and Vth vary with device parameters and operation conditions. 3. Explore the MOSFET speed and gain in term of device parameters and operations conditions 4. Practice the design of Common-Source Amplifier. 5. Examine trade-off between Gain Bandwidth Product (GBW), open loop gain (Av0), power (Id), area (transistors size) and linear output range. Pre-labs: Assuming: transistors operate only in three possible regions: cut-off region, linear region or saturation region and follow square law in saturation region. Vth , NMOS 0.68V Vth , PMOS 0.85V Temp 27C nCox 110 S / V p Cox 25 S / V Derive the following relationships and plot them for both a NMOS and PMOS transistor with size of W/L=N*1.5um/0.9um, N=1, 4, 16 1. gm vs. VGS , assuming VGS 0 ~ 5V , VDS 5V 2. gm I vs. D I W D L 3. You could use MATLAB to build your own MOSFET model to plot the relationship in subthreshold region and saturation region. For those who are interested in compact model for MOSFET, you could refer to the instruction files and MATLAB codes posted on our lab homepage. However, it is not required, just for you to understand the characteristics of MOSFET Attention: 1. Please carefully read this instruction and there are tips and examples at the end of this instruction about efficient simulation of multiple parameters. -

The Common Source JFET Amplifier

The Common Source JFET Amplifier Small signal amplifiers can also be made using Field Effect Transistors or FET's for short. These devices have the advantage over bipolar transistors of having an extremely high input impedance along with a low noise output making them ideal for use in amplifier circuits that have very small input signals. The design of an amplifier circuit based around a junction field effect transistor or "JFET", (N- channel FET for this tutorial) or even a metal oxide silicon FET or "MOSFET" is exactly the same principle as that for the bipolar transistor circuit used for a Class A amplifier circuit we looked at in the previous tutorial. Firstly, a suitable quiescent point or "Q-point" needs to be found for the correct biasing of the JFET amplifier circuit with single amplifier configurations of Common-source (CS), Common- drain (CD) or Source-follower (SF) and the Common-gate (CG) available for most FET devices. These three JFET amplifier configurations correspond to the common-emitter, emitter-follower and the common-base configurations using bipolar transistors. In this tutorial about FET amplifiers we will look at the popular Common Source JFET Amplifier as this is the most widely used JFET amplifier design. Consider the Common Source JFET Amplifier circuit configuration below. Common Source JFET Amplifier The amplifier circuit consists of an N-channel JFET, but the device could also be an equivalent N-channel depletion-mode MOSFET as the circuit diagram would be the same just a change in the FET, connected in a common source configuration. The JFET gate voltage Vg is biased through the potential divider network set up by resistors R1 and R2 and is biased to operate within its saturation region which is equivalent to the active region of the bipolar junction transistor. -

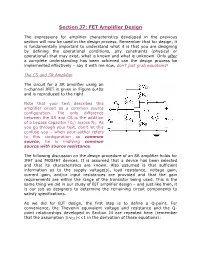

Section J7: FET Amplifier Design

Section J7: FET Amplifier Design The expressions for amplifier characteristics developed in the previous section will now be used in the design process. Remember that for design, it is fundamentally important to understand what it is that you are designing by defining the operational conditions, any constraints (physical or operational) that may exist, what is known and what is unknown. Only after a complete understanding has been achieved can the design process be implemented effectively – say it with me now, don’t just grab equations! The CS and SR Amplifier The circuit for a SR amplifier using an n-channel JFET is given in Figure 6.40a and is reproduced to the right Note that your text describes this amplifier circuit as a common source configuration. The only difference between the SR and CS is the addition of a bypass capacitor (CS) across RS. As you go through your text, don’t let this confuse you – when your author refers to this configuration as common source, he is implying common source with source resistance. The following discussion on the design procedure of an SR amplifier holds for JFET and MOSFET devices. It is assumed that a device has been selected and that its characteristics are known. Also assumed is that sufficient information as to the supply voltage(s), load resistance, voltage gain, current gain, and/or input resistances are provided and that the gain requirements are within the range of the transistor being used. This is the same thing we did in our study of BJT amplifier design – and just like then, it is our job as designers to determine the remaining circuit components to satisfy specifications.