Project 15 MOSFET Amplifiers with Current Source Biasing

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

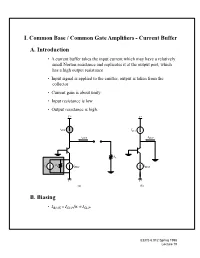

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Precision Current Sources and Sinks Using Voltage References

Application Report SNOAA46–June 2020 Precision Current Sources and Sinks Using Voltage References Marcoo Zamora ABSTRACT Current sources and sinks are common circuits for many applications such as LED drivers and sensor biasing. Popular current references like the LM134 and REF200 are designed to make this choice easier by requiring minimal external components to cover a broad range of applications. However, sometimes the requirements of the project may demand a little more than what these devices can provide or set constraints that make them inconvenient to implement. For these cases, with a voltage reference like the TL431 and a few external components, one can create a simple current bias with high performance that is flexible to fit meet the application requirements. Current sources and sinks have been covered extensively in other Texas Instruments application notes such as SBOA046 and SLYC147, but this application note will cover other common current sources that haven't been previously discussed. Contents 1 Precision Voltage References.............................................................................................. 1 2 Current Sink with Voltage References .................................................................................... 2 3 Current Source with Voltage References................................................................................. 4 4 References ................................................................................................................... 6 List of Figures 1 Current -

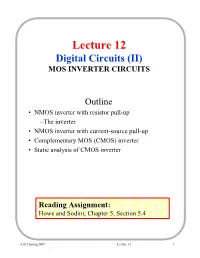

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS Outline • NMOS inverter with resistor pull-up –The inverter • NMOS inverter with current-source pull-up • Complementary MOS (CMOS) inverter • Static analysis of CMOS inverter Reading Assignment: Howe and Sodini; Chapter 5, Section 5.4 6.012 Spring 2007 Lecture 12 1 1. NMOS inverter with resistor pull-up: Dynamics •CL pull-down limited by current through transistor – [shall study this issue in detail with CMOS] •CL pull-up limited by resistor (tPLH ≈ RCL) • Pull-up slowest VDD VDD R R VOUT: VOUT: HI LO LO HI V : VIN: IN C LO HI CL HI LO L pull-down pull-up 6.012 Spring 2007 Lecture 12 2 1. NMOS inverter with resistor pull-up: Inverter design issues Noise margins ↑⇒|Av| ↑⇒ •R ↑⇒|RCL| ↑⇒ slow switching •gm ↑⇒|W| ↑⇒ big transistor – (slow switching at input) Trade-off between speed and noise margin. During pull-up we need: • High current for fast switching • But also high incremental resistance for high noise margin. ⇒ use current source as pull-up 6.012 Spring 2007 Lecture 12 3 2. NMOS inverter with current-source pull-up I—V characteristics of current source: iSUP + 1 ISUP r i oc vSUP SUP _ vSUP Equivalent circuit models : iSUP + ISUP r r vSUP oc oc _ large-signal model small-signal model • High current throughout voltage range vSUP > 0 •iSUP = 0 for vSUP ≤ 0 •iSUP = ISUP + vSUP/ roc for vSUP > 0 • High small-signal resistance roc. 6.012 Spring 2007 Lecture 12 4 NMOS inverter with current-source pull-up Static Characteristics VDD iSUP VOUT VIN CL Inverter characteristics : iD = V 4 3 VIN VGS I + DD SUP roc 2 1 = vOUT vDS VDD (a) VOUT 1 2 3 4 VIN (b) High roc ⇒ high noise margins 6.012 Spring 2007 Lecture 12 5 PMOS as current-source pull-up I—V characteristics of PMOS: + S + VSG _ VSD G B − _ + IDp 5 V + D − V + G − V − D − ID(VSG,VSD) (a) = VSG 3.5 V 300 V = V + V = V − 1 V 250 (triode SD SG Tp SG region) V = 3 V 200 SG − IDp (µA) (saturation region) 150 = VSG 25 100 = 0, 0.5, VSG 1 V (cutoff region) V = 2 V 50 SG = VSG 1.5 V 12345 VSD (V) (b) Note: enhancement-mode PMOS has VTp <0. -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

Transistor Current Source

PY 452 Advanced Physics Laboratory Hans Hallen Electronics Labs One electronics project should be completed. If you do not know what an op-amp is, do either lab 2 or lab 3. A written report is due, and should include a discussion of the circuit with inserted equations and plots as appropriate to substantiate the words and show that the measurements were taken. The report should not consist of the numbered items below and short answers, but should be one coherent discussion that addresses most of the issues brought out in the numbered items below. This is not an electronics course. Familiarity with electronics concepts such as input and output impedance, noise sources and where they matter, etc. are important in the lab AND SHOULD APPEAR IN THE REPORT. The objective of this exercise is to gain familiarity with these concepts. Electronics Lab #1 Transistor Current Source Task: Build and test a transistor current source, , +V with your choice of current (but don't exceed the transistor, power supply, or R ratings). R1 Rload You may wish to try more than one current. (1) Explain your choice of R1, R2, and Rsense. VCE (a) In particular, use the 0.6 V drop of VBE - rule for current flow to calculate I in R2 VBE Rsense terms of Rsense, and the Ic/Ib rule to estimate Ib hence the values of R1&R2. (2) Try your source over a wide range of Rload values, plot Iload vs. Rload and interpret. You may find it instructive to look at VBE and VCE with a floating (neither side grounded) multimeter. -

JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET Datasheet

JFE150 SLPS732 – JUNE 2021 JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET 1 Features and yields excellent noise performance for currents from 50 μA to 20 mA. When biased at 5 mA, the • Ultra-low noise: device yields 0.8 nV/√Hz of input-referred noise, – Voltage noise: giving ultra-low noise performance with extremely high input impedance (> 1 TΩ). The JFE150 also • 0.8 nV/√Hz at 1 kHz, IDS = 5 mA features integrated diodes connected to separate • 0.9 nV/√Hz at 1 kHz, IDS = 2 mA – Current noise: 1.8 fA/√Hz at 1 kHz clamp nodes to provide protection without the addition • Low gate current: 10 pA (max) of high leakage, nonlinear external diodes. • Low input capacitance: 24 pF at VDS = 5 V The JFE150 can withstand a high drain-to-source • High gate-to-drain and gate-to-source breakdown voltage of 40-V, as well as gate-to-source and gate- voltage: –40 V to-drain voltages down to –40 V. The temperature • High transconductance: 68 mS range is specified from –40°C to +125°C. The device • Packages: Small SC70 and SOT-23 (Preview) is offered in 5-pin SOT-23 and SC-70 packages. 2 Applications Device Information • Microphone inputs PART NUMBER PACKAGE(1) BODY SIZE (NOM) • Hydrophones and marine equipment SOT-23 (5) - Preview 2.90 mm × 1.60 mm JFE150 • DJ controllers, mixers, and other DJ equipment SC-70 (5) 2.00 mm × 1.25 mm • Professional audio mixer or control surface • Guitar amplifier and other music instrument (1) For all available packages, see the package option addendum at the end of the data sheet. -

Bias Circuits for RF Devices

Bias Circuits for RF Devices Iulian Rosu, YO3DAC / VA3IUL, http://www.qsl.net/va3iul A lot of RF schematics mention: “bias circuit not shown”; when actually one of the most critical yet often overlooked aspects in any RF circuit design is the bias network. The bias network determines the amplifier performance over temperature as well as RF drive. The DC bias condition of the RF transistors is usually established independently of the RF design. Power efficiency, stability, noise, thermal runway, and ease to use are the main concerns when selecting a bias configuration. A transistor amplifier must possess a DC biasing circuit for a couple of reasons. • We would require two separate voltage supplies to furnish the desired class of bias for both the emitter-collector and the emitter-base voltages. • This is in fact still done in certain applications, but biasing was invented so that these separate voltages could be obtained from but a single supply. • Transistors are remarkably temperature sensitive, inviting a condition called thermal runaway. Thermal runaway will rapidly destroy a bipolar transistor, as collector current quickly and uncontrollably increases to damaging levels as the temperature rises, unless the amplifier is temperature stabilized to nullify this effect. Amplifier Bias Classes of Operation Special classes of amplifier bias levels are utilized to achieve different objectives, each with its own distinct advantages and disadvantages. The most prevalent classes of bias operation are Class A, AB, B, and C. All of these classes use circuit components to bias the transistor at a different DC operating current, or “ICQ”. When a BJT does not have an A.C. -

Current Source & Source Transformation Notes

EE301 – CURRENT SOURCES / SOURCE CONVERSION Learning Objectives a. Analyze a circuit consisting of a current source, voltage source and resistors b. Convert a current source and a resister into an equivalent circuit consisting of a voltage source and a resistor c. Evaluate a circuit that contains several current sources in parallel Ideal sources An ideal source is an active element that provides a specified voltage or current that is completely independent of other circuit elements. DC Voltage DC Current Source Source Constant Current Sources The voltage across the current source (Vs) is dependent on how other components are connected to it. Additionally, the current source voltage polarity does not have to follow the current source’s arrow! 1 Example: Determine VS in the circuit shown below. Solution: 2 Example: Determine VS in the circuit shown above, but with R2 replaced by a 6 k resistor. Solution: 1 8/31/2016 EE301 – CURRENT SOURCES / SOURCE CONVERSION 3 Example: Determine I1 and I2 in the circuit shown below. Solution: 4 Example: Determine I1 and VS in the circuit shown below. Solution: Practical voltage sources A real or practical source supplies its rated voltage when its terminals are not connected to a load (open- circuited) but its voltage drops off as the current it supplies increases. We can model a practical voltage source using an ideal source Vs in series with an internal resistance Rs. Practical current source A practical current source supplies its rated current when its terminals are short-circuited but its current drops off as the load resistance increases. We can model a practical current source using an ideal current source in parallel with an internal resistance Rs. -

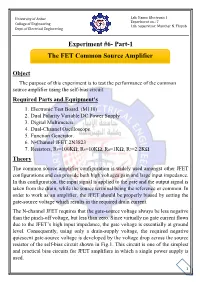

Experiment #6- Part-1 the FET Common Source Amplifier

University of Anbar Lab. Name: Electronic I Experiment no.: 7 College of Engineering Lab. Supervisor: Munther N. Thiyab Dept. of Electrical Engineering Experiment #6- Part-1 The FET Common Source Amplifier Object The purpose of this experiment is to test the performance of the common source amplifier using the self-bias circuit. Required Parts and Equipment's 1. Electronic Test Board. (M110) 2. Dual Polarity Variable DC Power Supply 3. Digital Multimeters. 4. Dual-Channel Oscilloscope. 5. Function Generator. 6. N-Channel JFET 2N3823 7. Resistors, R5=100KΩ, R6=10KΩ, R8=1KΩ, R7=2.2KΩ Theory The common source amplifier configuration is widely used amongst other JFET configurations and can provide both high voltages gain and large input impedance. In this configuration, the input signal is applied to the gate and the output signal is taken from the drain, while the source terminal being the reference or common. In order to work as an amplifier, the JFET should be properly biased by setting the gate-source voltage which results in the required drain current. The N-channel JFET requires that the gate-source voltage always be less negative than the pinch-off voltage, but less than zero. Since virtually no gate current flows due to the JFET’s high input impedance, the gate voltage is essentially at ground level. Consequently, using only a drain-supply voltage, the required negative quiescent gate-source voltage is developed by the voltage drop across the source resistor of the self-bias circuit shown in Fig.1. This circuit is one of the simplest and practical bias circuits for JFET amplifiers in which a single power supply is used. -

Lecture 24 Multistage Amplifiers (I) MULTISTAGE AMPLIFIER

Lecture 24 Multistage Amplifiers (I) MULTISTAGE AMPLIFIER Outline 1. Introduction 2. CMOS multi-stage voltage amplifier 3. BiCMOS multistage voltage amplifier 4. BiCMOS current buffer 5. Coupling amplifier stages Reading Assignment: Howe and Sodini, Chapter 9, Sections 9-1-9.3 6.012 Spring 2007 Lecture 24 1 1. Introduction Most often, single stage amplifier does not accomplish design goals: • Need more gain than could be provided by a single stage • Need to adapt to specified RS and RL to maximize efficiency ⇒ Multistage amplifier VBIAS Issues: • What amplifying stages should be used and in what order? • What devices should be used, BJT or MOSFET? • How is biasing to be done? 6.012 Spring 2007 Lecture 24 2 Summary of single stage amplifier characteristics Key Stage A , A R R vo io in out Function Common Transcon- ∞ ro // roc ductance Source Avo =−gm(ro //roc) amplifier Common gm 1 Voltage Avo ≈ ∞ Drain gm + gmb gm + gmb Buffer Current Common A ≈ −1 1 r //[r (1+ g R )] io oc o m S buffer Gate gm + gmb Common Transcon- Avo=−gm(ro//roc) r Emitter π ro // roc ductance amplifier Common 1 RS Voltage Avo ≈1 rπ + βo (ro // roc // RL ) + Collector gm βo buffer Common Current Aio ≈ −1 1 r //[r (1+ g ()r // R )] oc o m π S buffer Base gm Differences between BJT’s and MOSFETs BJT MOSFET βo rπ = gmb ∝ gm gm IC W gm = > gm = 2 µCox ID Vth L VA 1 ro = > ro = IC λI D 6.012 Spring 2007 Lecture 24 3 2. CMOS Multistage Voltage Amplifier Goals: • High voltage gain, Avo • High input resistance, Rin • Low output resistance, Rout Good starting point: Common-Source stage: •Rin=∞ •Avo=-gm(ro//roc), probably insufficient •Rout= (ro//roc), too high 6.012 Spring 2007 Lecture 24 4 CMOS Multistage Voltage Amplifier (contd.) Add second CS stage to get more gain: •Rin=∞ •Avo=gm1(ro1//roc1) gm2(ro2//roc2) •Rout= (ro2//roc2), still too high Add CD stage at output (to reduce Rout): •Rin=∞ gm3 • Avo = gm1()ro1 || roc1 gm2()ro2 || roc2 1 gm3 + gmb3 • Rout = gm3 + gmb3 6.012 Spring 2007 Lecture 24 5 3.