FET) Field Effect Transistor Projects

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Bias Circuits for RF Devices

Bias Circuits for RF Devices Iulian Rosu, YO3DAC / VA3IUL, http://www.qsl.net/va3iul A lot of RF schematics mention: “bias circuit not shown”; when actually one of the most critical yet often overlooked aspects in any RF circuit design is the bias network. The bias network determines the amplifier performance over temperature as well as RF drive. The DC bias condition of the RF transistors is usually established independently of the RF design. Power efficiency, stability, noise, thermal runway, and ease to use are the main concerns when selecting a bias configuration. A transistor amplifier must possess a DC biasing circuit for a couple of reasons. • We would require two separate voltage supplies to furnish the desired class of bias for both the emitter-collector and the emitter-base voltages. • This is in fact still done in certain applications, but biasing was invented so that these separate voltages could be obtained from but a single supply. • Transistors are remarkably temperature sensitive, inviting a condition called thermal runaway. Thermal runaway will rapidly destroy a bipolar transistor, as collector current quickly and uncontrollably increases to damaging levels as the temperature rises, unless the amplifier is temperature stabilized to nullify this effect. Amplifier Bias Classes of Operation Special classes of amplifier bias levels are utilized to achieve different objectives, each with its own distinct advantages and disadvantages. The most prevalent classes of bias operation are Class A, AB, B, and C. All of these classes use circuit components to bias the transistor at a different DC operating current, or “ICQ”. When a BJT does not have an A.C. -

The Bipolar Junction Transistor (BJT)

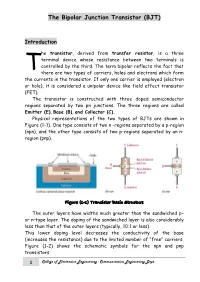

The Bipolar Junction Transistor (BJT) Introduction he transistor, derived from transfer resistor, is a three terminal device whose resistance between two terminals is controlled by the third. The term bipolar reflects the fact that T there are two types of carriers, holes and electrons which form the currents in the transistor. If only one carrier is employed (electron or hole), it is considered a unipolar device like field effect transistor (FET). The transistor is constructed with three doped semiconductor regions separated by two pn junctions. The three regions are called Emitter (E), Base (B), and Collector (C). Physical representations of the two types of BJTs are shown in Figure (1–1). One type consists of two n -regions separated by a p-region (npn), and the other type consists of two p-regions separated by an n- region (pnp). Figure (1-1) Transistor Basic Structure The outer layers have widths much greater than the sandwiched p– or n–type layer. The doping of the sandwiched layer is also considerably less than that of the outer layers (typically, 10:1 or less). This lower doping level decreases the conductivity of the base (increases the resistance) due to the limited number of “free” carriers. Figure (1-2) shows the schematic symbols for the npn and pnp transistors 1 College of Electronics Engineering - Communication Engineering Dept. Figure (1-2) standard transistor symbol Transistor operation Objective: understanding the basic operation of the transistor and its naming In order for the transistor to operate properly as an amplifier, the two pn junctions must be correctly biased with external voltages. -

THE DESIGN, SIMULATION and FABRICATION of a GALLIUM ARSENIDE MONOLITHIC SAMPLE and HOLD CIRCUIT by WILLEM G. DURTLER B.Eng. Mcgi

THE DESIGN, SIMULATION AND FABRICATION OF A GALLIUM ARSENIDE MONOLITHIC SAMPLE AND HOLD CIRCUIT by WILLEM G. DURTLER B.Eng. McGill University A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF APPLIED SCIENCE in THE FACULTY OF GRADUATE STUDIES DEPARTMENT OF ELECTRICAL ENGINEERING We accept this thesis as conforming to the required standard THE UNIVERSITY OF BRITISH COLUMBIA June 1986 © Willem G. Durtler 1986 In presenting this thesis in partial fulfilment of the requirements for an advanced degree at the University of British Columbia, I agree that the Library shall make it freely available for reference and study. I further agree that permission for extensive copying of this thesis for scholarly purposes may be granted by the head of my department or by his or her representatives. It is understood that copying or publication of this thesis for financial gain shall not be allowed without my written permission. Department of ELECTRICAL ENGINEERING The .University of British Columbia 1956 Main Mall Vancouver, Canada V6T 1Y3 1986 06 12 ABSTRACT This thesis describes work done towards the development of a gallium arsenide monolithic sample-and-hold circuit. The literature relevant to high-speed electronic sampling is reviewed, and the different types of high• speed sampling circuits are discussed. The requirements of a sampling circuit for use in a distributed sampling amplifier are analyzed, and it is found that the most important requirement is a high input impedance. A circuit suitable for monolithic integration is designed and analyzed using the computer program mwSPICE. The different fabrication technologies for gallium arsenide integrated circuits are discussed, with emphasis on the self-aligned gate technologies, which can give reduced parasitic source and drain resistances. -

Low Cost Field Effect Transistor Measurements and Applications

Calhoun: The NPS Institutional Archive Theses and Dissertations Thesis Collection 1967-09 Low cost field effect transistor measurements and applications Holt, Ben Ford Monterey, California. U.S. Naval Postgraduate School http://hdl.handle.net/10945/12569 N PS ARCHIVE 1967 HHSSBBG™ HOLT, B. mammHI "•KMin «H WW RUSH 3W COST FIELD EFFECT TRANSISTOR :••';•'.••;. '•..','. •'•;• ."'•• • v ; i ' * • ' HOLT, JfL .'-.•' 5 Met V p- 3 LOW COST FIELD EFFECT TRANSISTOR MEASUREMENTS AND APPLICATIONS by Ben Ford Holt, Jr. Lieutenant, United States Navy B.S., Naval Academy, 1959 Submitted in partial fulfillment of the requirements for the degree of MA.STER OF SCIENCE IN ENGINEERING ELECTRONICS from the NAVAL POSTGRADUATE SCHOOL September, 1967 KcTT DU \, C>, ABSTRACT The field effect transistor (FET) has emerged as an important active device. Low cost FETs (about one dollar) are now available which should substantially enlarge the FET market. Measurements on and applications of various low cost FETs are discussed pointing out advantages and disadvantages of particular devices and circuits. Basic FET operation and terminology is discussed including the specification sheet, DC biasing, small signal representation^ and measurements of device parameters. Mixer, tuned amplifier, oscillator, and detector circuits were constructed and tested. Low noise character- istics are examined and a brief treatment of other applications is given. LIBRAKY NAVAL POSTGRADUATE SCHOOL MONTEREY, CALIF. 93940 TABLE OF CONTENTS Section Page 1. Introduction 11 2. Basic FET Operation and Terminology 12 3. The Specification Sheet 16 4. Direct Current Biasing 19 5. Small Signal Representation 24 6. Basic Measurements 27 7. The FET Mixer 34 8. Design of a 5 MHz Tuned Amplifier 42 9. -

An L-Band Stacked SOI CMOS Amplifier

ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) j.inst.Korean.electr.electron.eng.Vol.20,No.3,279∼284,September 2016 논문번호 16-03-10 http://dx.doi.org/10.7471/ikeee.2016.20.3.279 71 An L-band Stacked SOI CMOS Amplifier ★ Young-Gi Kim* , Jae-Yeon Hwang* Abstract This paper presents a two stage L-band power amplifier realized with a 0.32 μm Silicon-On-Insulator (SOI) CMOS technology. To overcome a low breakdown voltage limit of MOSFET, stacked-FET structures are employed, where three transistors in the first stage amplifier and four transistors in the second stage amplifier are connected in series so that their output voltage swings are added in phase. The stacked-FET structures enable the proposed amplifier to achieve a 21.5 dB small-signal gain and 15.7 dBm output 1-dB compression power at 1.9 GHz with a 122 mA DC current from a 4 V supply. The amplifier delivers a 19.7 dBm. This paper presents a two stage L-band power amplifier realized with a 0.32 μm Silicon-On-Insulator (SOI) CMOS technology. To overcome a low breakdown voltage limit of MOSFET, stacked-FET structures are employed, where three transistors in the first stage amplifier and four transistors in the second stage amplifier are connected in series so that their output voltage swings are added in phase. The stacked-FET structures enable the proposed amplifier to achieve a 21.5 dB small-signal gain and 15.7 dBm output 1-dB compression power at 1.9 GHz with a 122 mA DC current from a 4 V supply. -

Project 15 MOSFET Amplifiers with Current Source Biasing

Electronics Laboratory Project 15 - MOSFET Amps with CS (FET) - 1 Project 15 MOSFET Amplifiers with Current Source Biasing Objective: This project will focus on the use of FET current mirrors to provide the DC biasing for Common Source and Common Drain amplifiers, two of the primary FET amplifier stages. The design of each amplifier type (CS and CD) to achieve a specific design goal using current biasing will be examined. The frequency response and feedback adjustments will also be investigated. Components: 2N7000 FET Introduction: One of the primary differences between discrete and integrated amplifier design, as mentioned in Project 11, is the use of biasing resistors. The savings in “semiconductor real estate” is even more dramatic when the resistor area is compared to that of the active FETs. The ability to easily change the W/L ratios for the FETs used in the current source (see project 13 for additional discussion) provides great flexibility in selecting the size of the required power supply(ies) as well as in the value of the load currents. As in most semiconductor device fabrication, “exact” parameter values are difficult and expensive to obtain while matched device parameters are basically a “side effect” of the overall process. This “side effect” makes FET based current sources well suited for integrated circuits since the FETs are used for the entire source. This project will examine the use of an FET current mirror, as discussed in Project 13, to provide the DC bias for a Common Source and a Common Drain amplifier. The actual AC amplifier analysis and design is the same for both discrete and integrated circuits once the related changes due to the new biasing network have been incorporated. -

WIDE BAND GAP SEMICONDUCTOR TECHNOLOGY (Sic Mesfets and Gan Hemts) and THEIR RESPONSE in DIFFERENT CLASSES of POWER AMPLIFIERS

Linköping Studies in Science and Technology Thesis No. 1374 Wide Bandgap Semiconductor (SiC & GaN) Power Amplifiers in Different Classes S h e r A z a m LIU-TEK-LIC-2008:32 Material Science Division Department of Physics, Chemistry and Biology Linköpings universitet, SE-581 83 Linköping, Sweden Linköping 2008 LIU-TEK-LIC-2008:32 ISBN: 978-91-7393-855-6 ISSN: 0280-7971 http://urn.kb.se/resolve?urn=urn:nbn:se:liu:diva-11786 Printed by Liutryck, Linköping, Sweden To my Parents, family and all those who pray for the successful completion of this research work ACKNOWLEDGMENTS All praise is due to our God (ALLAH) who enabled me to do this research work. I’m deeply indebted to my supervisor, Docent Qamar ul Wahab, for his guidance and encouragement during this research work. He introduced me to the most experienced and pronounced researchers of professional world, like my co-supervisor Professor Christer Sevensson, department of electrical engineering (ISY) and Mr. Rolf Jonsson, sensor group (previous Microwave Technology group) at Swedish Defence Research Agency (FOI). I am thankful to them for useful recommendations, excellent guidance and giving me fantastic feedback. I would say I was lucky to meet people like them, who advice and assistance me during my work. I acknowledge FOI for technical and financial support in this work. I also acknowledge Mr. Stig Leijon at FOI, for manufacturing amplifiers and help with the development of the measurement fixtures. Of course I cannot forget my colleagues at Material Science Division and Eva Wibom for the help in administrative work. -

Stacked-FET Based Gaas Monolithic Microwave High-Power Amplifiers for Active Electronically Scanned Array Radar Front-Ends

Stacked-FET based GaAs Monolithic Microwave High-Power Amplifiers for Active Electronically Scanned Array Radar Front-Ends Gijsbert van der Bent PROMOTIECOMMISSIE: Voorzitter/secretaris prof. dr. J.N. Kok Universiteit Twente Promotor prof. dr. ir. F.E. van Vliet Universiteit Twente Referent dr. ir. W.J.A de Heij Thales Netherlands Leden prof. dr. ir. B. Nauta Universiteit Twente prof. dr. A.A. Stoorvogel Universiteit Twente prof. S. Mahon Macquarie University prof. dr. D.M.W. Leenaerts Technische Universiteit Eindhoven The work presented in this thesis has been supported by the Dutch Radar Centre of Expertise (D-RACE), a strategic alliance of Thales Netherlands and TNO. Cover: Ilse Modder, www.ilsemodder.nl Printed by Gildeprint Drukkerijen. ISBN: 978-90-365-4766-6 DOI: 10.3990/1.9789036547666 Copyright © 2019 by Gijsbert van der Bent All rights reserved. No parts of this thesis may be reproduced, stored in a retrieval system or transmitted in any form or by any means without permission of the author. Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd, in enige vorm of op enige wijze, zonder voorafgaande schriftelijke toestemming van de auteur. Stacked-FET based GaAs Monolithic Microwave High-Power Amplifiers for Active Electronically Scanned Array Radar Front-Ends PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. T.T.M. Palstra, volgens besluit van het College voor Promoties in het openbaar te verdedigen op vrijdag 3 mei 2019 om 16:45 uur door Gijsbert van der Bent geboren op 11 februari 1975 te Leiden Dit proefschrift is goedgekeurd door: De promotor: prof. -

Designing with Field-Effect Transistors

DESIGNING WITH FIELD-EFFECT TRANSISTORS DESIGNING WITH FIELD-EFFECT TRA~SISTORS SILICONIX INC. Editor in Chief Arthur D. Evans McGRAW-HILL BOOK COMPANY New York St. Louis San Francisco Auckland Bogota Hamburg Johannesburg London Madrid Mexico Montreal New Delhi Panama Paris Sao Paulo Singapore Sydney Tokyo Toronto Library of Congress Cataloging in Publication Data Siliconix Incorporated. Designing with field-effect transistors. Includes index. 1. Field-effect transistors. 2. Transistor cir cuits. 3. Electronic circuit design. I. Evans, Arthur D. II. Title. TK7871.95.S54 1981 621.3815'284 80-15690 ISBN 0-07-057449-9 Copyright ® 1981 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. 567890 KPKP 89876543 The editors for this book were Tyler G. Hicks and Geraldine Fahey, the designer was Elliot Epstein, and the production supervisor was Sally Fliess. It was set in Baskerville by The Kingsport Press. Printed and bound by The Kingsport Press. CONTENTS Preface lX 1 FIELD-EFFECf TRANSISTOR THEORY 1 2 PARAMETERS AND SPECIFICATIONS 25 3 LOW-FREQUENCY CIRCUITS 61 4 HIGH-FREQUENCY CIRCUITS 137 5 ANALOG SWITCHES 193 6 VOLTAGE-CONTROLLED RESISTORS AND FET CURRENT SOURCES 233 7 POWERFETs 255 8 FETs IN INTEGRATED CIRCUITS 281 INDEX 289 v I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I CONTRIBUTORS Written by the Applications Engineering Staff of Siliconix Incorporated Editor in Chief ARTHUR D. -

Theory and Applications of Field-Effect Transistors

"HEORY AND APPLICATIONS ^^ FIELD-L""7~^CT TPJ\NSlf""70"\r by /&? COE WILLAP.D TOLIVER 3. S., Prairie View as: College, 1952 A MASTER'S REPORT sv-bnitted in partial fulfillment of requirements for the FAST"?. 0? SCIENCE Department of Electrical Engineering KANSAS STATS UNIVE"^T '" Manhattan, Kansas 19S7 Approved by: ] 2 i Major Professor / LU Hi " CONTENTS Page INTRODUCTION 1 CONSTRUCTION OF FIELD-EFFECT TRANSISTORS 4 THE FIELD-EFFECT TRANSISTOR 7 FIELD-EFFECT TRANSISTOR THEORY 10 The Conductive Channel 11 Depletion Layer Potential 13 Channel Current 17 Characteristics of Field-effect Transistors 21 Mutual Transconductance 22 Determining the Field-effect Transistor Pinch-off Voltage 26 Temperature Dependence of I 2 8 BIASING FIELD-EFFECT TRANSISTORS 30 SELECTING THE 3S~T FIELD-EFFECT TRANSISTOR 36 tCUIT DESIGN 3 8 SMALL-SIGNAL LOW FREQUENCY-PROPERTIES 41 SMALL-SIGNAL EQUIVALENT CIRCUIT 45 FIELD EFFECT TRANSISTOR AMPLIFIERS 49 Basic FET Amplifier Configurations 49 Voltage Amplifier Circuit 50 The Source-follov;er Circuit 51 FET Cascade with 3ipolar Transistor 53 THE POWER FIELD-EFFECT TRANSISTOR 59 CONCLUSIONS 61 Ill Page REFERENCES 64 ACKNOWLEDGEMENT 66 LIST OF PRINCIPAL SYMBOLS 67 . INTRODUCTION In 1952, shortly after the invention of the junction transistor, Shockley (18) described theoretically a new active device based on the modulation of a majority-carrier current. The principle of operation of this device, which he termed a unipolar field-effect transistor, is radically different from that of the junction transistor in that the majority - rather than minority-carrier current is modulated by altering the width of a conducting channel through the narrowing or widen- ing of a p-n junction depletion layer. -

Chapter 8:Field Effect Transistors (FET's)

Chapter 8:Field Effect Transistors (FET’s) The FET The idea for a field-effect transistor (FET) was first proposed by Julius Lilienthal, a physicist and inventor. In 1930 he was granted a U.S. patent for the device. His ideas were later refined and developed into the FET. Materials were not available at the time to build his device. A practical FET was not constructed until the 1950’s. Today FETs are the most widely used components in integrated circuits. 1 8-1: The Junction Field Effect Transistor (JFET) Basic Structure The JFET ( junction field-effect transistor) is a type of FET that operates with a reverse-biased pn junction to control current in a channel. JFETs has two categories, n channel or p channel. For n-channel JFET shown; the drain (D) is at the upper end, and the source (D) is at the lower end. Two p-type regions are diffused in the n-type material to form a channel, and both p-type regions are connected to the gate (G) lead. for p-channel, the gate is connected to n-type regions forming basic structure of the two the channel into the p-type material types of JFET. 8-1: The Junction Field Effect Transistor (JFET) Basic Operation Biasing of JFET is shown in the figure VDD provide drain-to-source voltage Æ current flow from drain to source VGG sets the reverse bias between the gate and the source Æ sets the depletion region along the pn junction Æ restricting channel width Æ increase channel resistance 2 8-1: The Junction Field Effect Transistor (JFET) Basic Operation Depletion region By varying the gate voltage (VGG) Æincreasing –ve voltage between G and S Æ varying the channel width Æ controlling the amount of drain current (ID); As VGG increase Æ depletion region increase Æ channel decrease Æ higher resistance Æ lower current The schematic symbols for both n-channel and p-channel JFETs are shown in the adjacent figure; the arrow on the gate points “in” for n channel and “out” for p channel. -

Advanced High Efficiency and Broadband Power Amplifiers Based on Gan HEMT for Wireless Applications

Politecnico di Torino Porto Institutional Repository [Doctoral thesis] Advanced High Efficiency and Broadband Power Amplifiers Based on GaN HEMT for Wireless Applications Original Citation: Iqbal, Mustazar (2017). Advanced High Efficiency and Broadband Power Amplifiers Based on GaN HEMT for Wireless Applications. PhD thesis Availability: This version is available at : http://porto.polito.it/2672421/ since: May 2017 Published version: DOI:10.6092/polito/porto/2672421 Terms of use: This article is made available under terms and conditions applicable to Open Access Policy Article ("Public - All rights reserved") , as described at http://porto.polito.it/terms_and_conditions. html Porto, the institutional repository of the Politecnico di Torino, is provided by the University Library and the IT-Services. The aim is to enable open access to all the world. Please share with us how this access benefits you. Your story matters. (Article begins on next page) Doctoral Dissertation Doctoral Program in Electronic Engineering (29th Cycle) Advanced High Efficiency and Broadband Power Amplifiers Based on GaN HEMT for Wireless Applications By Mustazar Iqbal ****** Supervisor(s): Prof. Marco Pirola, Supervisor Doctoral Examination Committee: Prof. Alessandro Cidronali, University of Firenze Prof. Antonio Raffo, University of Ferrara Politecnico di Torino 2016 Declaration I hereby declare that, the contents and organization of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data. Mustazar Iqbal 2016 * This dissertation is presented in partial fulfillment of the requirements for Ph.D. degree in the Graduate School of Politecnico di Torino (ScuDo). I would like to dedicate this thesis to my loving parents Acknowledgment Foremost, I would like to express my sincere gratitude to my adviser Professor Marco Pirola, for the continuous support of my PhD study and research, for his patience, enthusiasm, motivation and extensive knowledge.