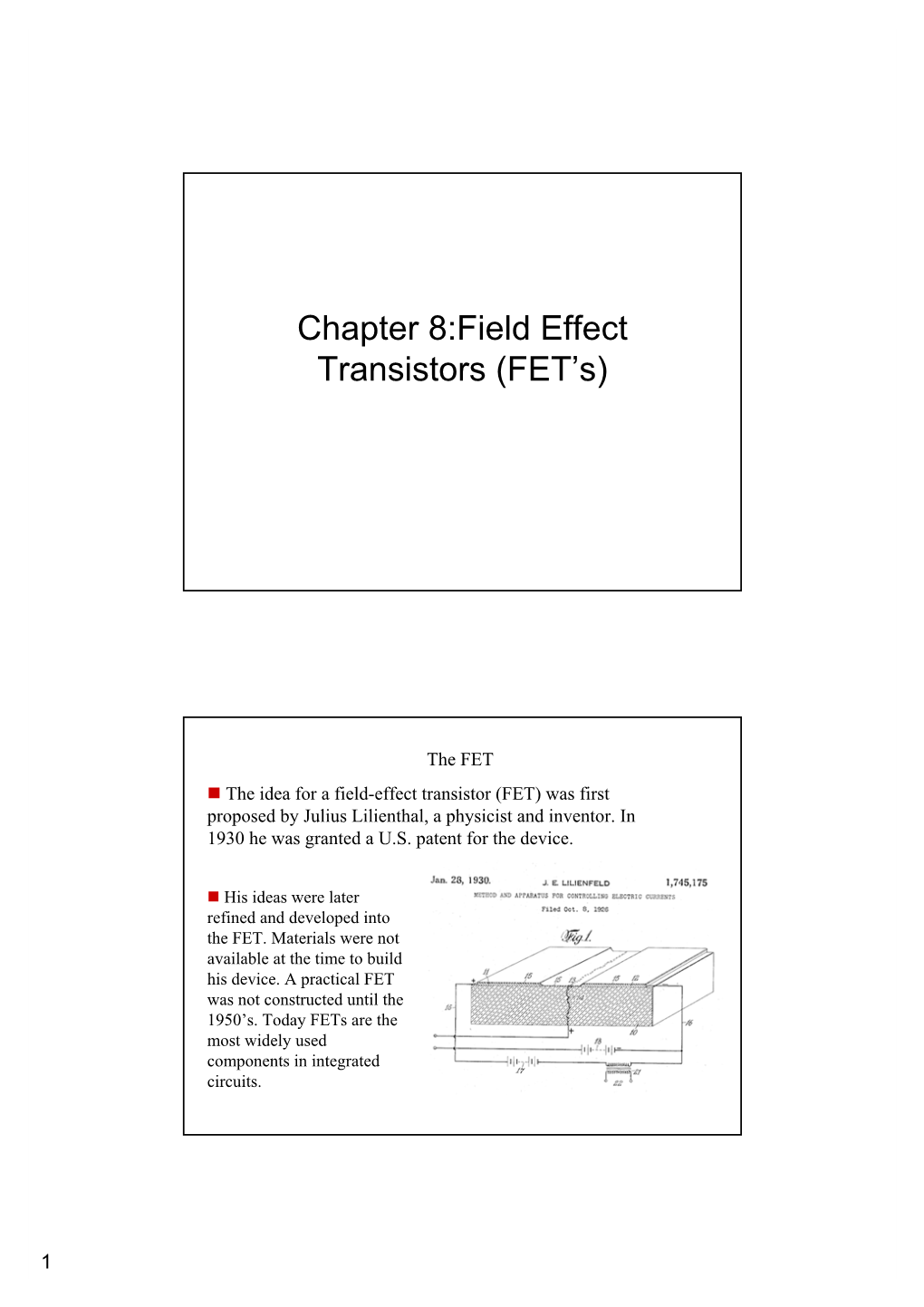

Chapter 8:Field Effect Transistors (FET's)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Role of Mosfets Transconductance Parameters and Threshold Voltage in CMOS Inverter Behavior in DC Mode

Preprints (www.preprints.org) | NOT PEER-REVIEWED | Posted: 28 July 2017 doi:10.20944/preprints201707.0084.v1 Article Role of MOSFETs Transconductance Parameters and Threshold Voltage in CMOS Inverter Behavior in DC Mode Milaim Zabeli1, Nebi Caka2, Myzafere Limani2 and Qamil Kabashi1,* 1 Department of Engineering Informatics, Faculty of Mechanical and Computer Engineering ([email protected]) 2 Department of Electronics, Faculty of Electrical and Computer Engineering ([email protected], [email protected]) * Correspondence: [email protected]; Tel.: +377-44-244-630 Abstract: The objective of this paper is to research the impact of electrical and physical parameters that characterize the complementary MOSFET transistors (NMOS and PMOS transistors) in the CMOS inverter for static mode of operation. In addition to this, the paper also aims at exploring the directives that are to be followed during the design phase of the CMOS inverters that enable designers to design the CMOS inverters with the best possible performance, depending on operation conditions. The CMOS inverter designed with the best possible features also enables the designing of the CMOS logic circuits with the best possible performance, according to the operation conditions and designers’ requirements. Keywords: CMOS inverter; NMOS transistor; PMOS transistor; voltage transfer characteristic (VTC), threshold voltage; voltage critical value; noise margins; NMOS transconductance parameter; PMOS transconductance parameter 1. Introduction CMOS logic circuits represent the family of logic circuits which are the most popular technology for the implementation of digital circuits, or digital systems. The small dimensions, low power of dissipation and ease of fabrication enable extremely high levels of integration (or circuits packing densities) in digital systems [1-5]. -

Junction Field Effect Transistor (JFET)

Junction Field Effect Transistor (JFET) The single channel junction field-effect transistor (JFET) is probably the simplest transistor available. As shown in the schematics below (Figure 6.13 in your text) for the n-channel JFET (left) and the p-channel JFET (right), these devices are simply an area of doped silicon with two diffusions of the opposite doping. Please be aware that the schematics presented are for illustrative purposes only and are simplified versions of the actual device. Note that the material that serves as the foundation of the device defines the channel type. Like the BJT, the JFET is a three terminal device. Although there are physically two gate diffusions, they are tied together and act as a single gate terminal. The other two contacts, the drain and source, are placed at either end of the channel region. The JFET is a symmetric device (the source and drain may be interchanged), however it is useful in circuit design to designate the terminals as shown in the circuit symbols above. The operation of the JFET is based on controlling the bias on the pn junction between gate and channel (note that a single pn junction is discussed since the two gate contacts are tied together in parallel – what happens at one gate-channel pn junction is happening on the other). If a voltage is applied between the drain and source, current will flow (the conventional direction for current flow is from the terminal designated to be the gate to that which is designated as the source). The device is therefore in a normally on state. -

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

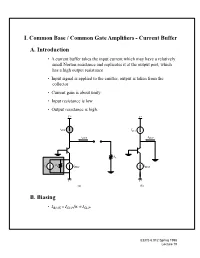

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

Precision Current Sources and Sinks Using Voltage References

Application Report SNOAA46–June 2020 Precision Current Sources and Sinks Using Voltage References Marcoo Zamora ABSTRACT Current sources and sinks are common circuits for many applications such as LED drivers and sensor biasing. Popular current references like the LM134 and REF200 are designed to make this choice easier by requiring minimal external components to cover a broad range of applications. However, sometimes the requirements of the project may demand a little more than what these devices can provide or set constraints that make them inconvenient to implement. For these cases, with a voltage reference like the TL431 and a few external components, one can create a simple current bias with high performance that is flexible to fit meet the application requirements. Current sources and sinks have been covered extensively in other Texas Instruments application notes such as SBOA046 and SLYC147, but this application note will cover other common current sources that haven't been previously discussed. Contents 1 Precision Voltage References.............................................................................................. 1 2 Current Sink with Voltage References .................................................................................... 2 3 Current Source with Voltage References................................................................................. 4 4 References ................................................................................................................... 6 List of Figures 1 Current -

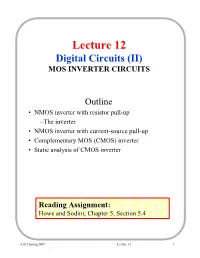

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS Outline • NMOS inverter with resistor pull-up –The inverter • NMOS inverter with current-source pull-up • Complementary MOS (CMOS) inverter • Static analysis of CMOS inverter Reading Assignment: Howe and Sodini; Chapter 5, Section 5.4 6.012 Spring 2007 Lecture 12 1 1. NMOS inverter with resistor pull-up: Dynamics •CL pull-down limited by current through transistor – [shall study this issue in detail with CMOS] •CL pull-up limited by resistor (tPLH ≈ RCL) • Pull-up slowest VDD VDD R R VOUT: VOUT: HI LO LO HI V : VIN: IN C LO HI CL HI LO L pull-down pull-up 6.012 Spring 2007 Lecture 12 2 1. NMOS inverter with resistor pull-up: Inverter design issues Noise margins ↑⇒|Av| ↑⇒ •R ↑⇒|RCL| ↑⇒ slow switching •gm ↑⇒|W| ↑⇒ big transistor – (slow switching at input) Trade-off between speed and noise margin. During pull-up we need: • High current for fast switching • But also high incremental resistance for high noise margin. ⇒ use current source as pull-up 6.012 Spring 2007 Lecture 12 3 2. NMOS inverter with current-source pull-up I—V characteristics of current source: iSUP + 1 ISUP r i oc vSUP SUP _ vSUP Equivalent circuit models : iSUP + ISUP r r vSUP oc oc _ large-signal model small-signal model • High current throughout voltage range vSUP > 0 •iSUP = 0 for vSUP ≤ 0 •iSUP = ISUP + vSUP/ roc for vSUP > 0 • High small-signal resistance roc. 6.012 Spring 2007 Lecture 12 4 NMOS inverter with current-source pull-up Static Characteristics VDD iSUP VOUT VIN CL Inverter characteristics : iD = V 4 3 VIN VGS I + DD SUP roc 2 1 = vOUT vDS VDD (a) VOUT 1 2 3 4 VIN (b) High roc ⇒ high noise margins 6.012 Spring 2007 Lecture 12 5 PMOS as current-source pull-up I—V characteristics of PMOS: + S + VSG _ VSD G B − _ + IDp 5 V + D − V + G − V − D − ID(VSG,VSD) (a) = VSG 3.5 V 300 V = V + V = V − 1 V 250 (triode SD SG Tp SG region) V = 3 V 200 SG − IDp (µA) (saturation region) 150 = VSG 25 100 = 0, 0.5, VSG 1 V (cutoff region) V = 2 V 50 SG = VSG 1.5 V 12345 VSD (V) (b) Note: enhancement-mode PMOS has VTp <0. -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

Design of Cascode-Based Transconductance Amplifiers With

Design of Cascode-Based Transconductance Amplifiers with Low-Gain PVT Variability and Gain Enhancement Using a Body-Biasing Technique Nuno Pereira, Luis Oliveira, João Goes To cite this version: Nuno Pereira, Luis Oliveira, João Goes. Design of Cascode-Based Transconductance Amplifiers with Low-Gain PVT Variability and Gain Enhancement Using a Body-Biasing Technique. 4th Doctoral Conference on Computing, Electrical and Industrial Systems (DoCEIS), Apr 2013, Costa de Caparica, Portugal. pp.590-599, 10.1007/978-3-642-37291-9_64. hal-01348806 HAL Id: hal-01348806 https://hal.archives-ouvertes.fr/hal-01348806 Submitted on 25 Jul 2016 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Distributed under a Creative Commons Attribution| 4.0 International License Design of Cascode-based Transconductance Amplifiers with Low-gain PVT Variability and Gain Enhancement Using a Body-biasing Technique Nuno Pereira 2, Luis B. Oliveira 1,2 and João Goes 1,2 1 Centre for Technologies and Systems (CTS) – UNINOVA 2 Dept. of Electrical Engineering (DEE), Universidade Nova de Lisboa (UNL) Campus FCT/UNL, 2829-516, Caparica, Portugal [email protected], [email protected], [email protected] Abstract. -

Bias Circuits for RF Devices

Bias Circuits for RF Devices Iulian Rosu, YO3DAC / VA3IUL, http://www.qsl.net/va3iul A lot of RF schematics mention: “bias circuit not shown”; when actually one of the most critical yet often overlooked aspects in any RF circuit design is the bias network. The bias network determines the amplifier performance over temperature as well as RF drive. The DC bias condition of the RF transistors is usually established independently of the RF design. Power efficiency, stability, noise, thermal runway, and ease to use are the main concerns when selecting a bias configuration. A transistor amplifier must possess a DC biasing circuit for a couple of reasons. • We would require two separate voltage supplies to furnish the desired class of bias for both the emitter-collector and the emitter-base voltages. • This is in fact still done in certain applications, but biasing was invented so that these separate voltages could be obtained from but a single supply. • Transistors are remarkably temperature sensitive, inviting a condition called thermal runaway. Thermal runaway will rapidly destroy a bipolar transistor, as collector current quickly and uncontrollably increases to damaging levels as the temperature rises, unless the amplifier is temperature stabilized to nullify this effect. Amplifier Bias Classes of Operation Special classes of amplifier bias levels are utilized to achieve different objectives, each with its own distinct advantages and disadvantages. The most prevalent classes of bias operation are Class A, AB, B, and C. All of these classes use circuit components to bias the transistor at a different DC operating current, or “ICQ”. When a BJT does not have an A.C. -

Analog Integrated Current Drivers for Bioimpedance Applications: a Review

sensors Review Analog Integrated Current Drivers for Bioimpedance Applications: A Review Nazanin Neshatvar * , Peter Langlois, Richard Bayford and Andreas Demosthenous Department of Electronic and Electrical Engineering, University College London, Torrington Place, London WC1E 7JE, UK; [email protected] (P.L.); [email protected] (R.B.); [email protected] (A.D.) * Correspondence: [email protected] Received: 17 January 2019; Accepted: 4 February 2019; Published: 13 February 2019 Abstract: An important component in bioimpedance measurements is the current driver, which can operate over a wide range of impedance and frequency. This paper provides a review of integrated circuit analog current drivers which have been developed in the last 10 years. Important features for current drivers are high output impedance, low phase delay, and low harmonic distortion. In this paper, the analog current drivers are grouped into two categories based on open loop or closed loop designs. The characteristics of each design are identified. Keywords: bioimpedance measurement; current driver; integrated circuit; linear feedback; nonlinear feedback; transconductance 1. Introduction Bioimpedance measurement is defined as the study of biological tissue/cell in response to an alternating electric field, which can cover a frequency range from tens of Hz to several MHz [1,2]. The electrical properties of tissue/cell (conductive and dielectric properties) are characterized by frequency variable complex electrical bioimpedance providing important information about the tissue/cell physiology and pathology. In order to measure the bioimpedance, a current stimulus is required to be provided through a set of electrodes and measuring the corresponding potential via the same, or another, pair of electrodes. -

Transistor Biasing

Module 2:BJT Biasing Quote of the day "Peace cannot be kept by force. It can only be achieved by understanding”. ― Albert Einstein DC Load line and Bias Point • DC Load Line – For a transistor a straight line drawn on transistor output characteristics. IC – For CE circuit, the load line is a graph of collector current I versus V for a fixed C CE IB + value of R and supply voltage V C CC + VCE – Load Line? VCC VCE I C RC VBE - - V V I R – From Figure VCE=? CE CC C C – If VBE =0 then IC=0, VCE = VCC plot this point on characteristics(A). – Now assume that ICRC = VCC, i.e. IC = VCC /RC then VCE =0. Plot this point on characteristics(B). – Join points A and B by a straight line. DC Load line contd.. VCE VCC I C RC VV IC CC CE IC RC V CC B IC(sat) RC DC load line VVCE(off ) CC V A CE Example 1. Plot the dc load line for the circuit shown in Fig. Then, find the values of VCE for IC = 1, 2, 5 mA respectively. VVIRCE CC C C VCE 10 for I c 0 10 I 10mA c 110 3 IC (mA) VCE (V) 1 9 2 8 5 5 4 Example 2. For the circuit shown and Plot of the dc load line in Fig. find the values of IC for VCE = 0V and VCE for IC = 0. VVIRCE CC C C 5 I C 4.54mA V CC15V For the previous circuit shown observe the Plot of the dc load line with Rc=4.8 K find the values of IC for VCE = 0V and VCE for IC = 0. -

Channel Length Modulation • I Have Been Saying That for a MOSFET in Saturation, the Drain Current Is Independent of the Drain-To-Source Voltage 푉퐷푆 I.E

ECE315 / ECE515 Lecture-2 Date: 06.08.2015 • NMOS I/V Characteristics • Discussion on I/V Characteristics • MOSFET – Second Order Effect ECE315 / ECE515 NMOS I-V Characteristics Gradual Channel Approximation: Cut-off → Linear/Triode → Pinch-off/Saturation Assumptions: • VSB = 0 • VT is constant along the channel • 퐸푥 dominates 퐸푦 => need to consider current flow only in the 푥 −direction • Cutoff Mode: ퟎ ≤ 푽푮푺 ≤ 푽푻 IDS(cutoff) =0 This relationship is very simple—if the MOSFET is in cutoff, the drain current is simply zero ! ECE315 / ECE515 Linear Mode: 푽푮푺 ≥ 푽푻, ퟎ ≤ 푽푫푺 ≤ 푽푫(푺푨푻) => 푽푫푺 ≤ 푽푮푺 − 푽푻 • The channel reaches the drain. Gate VS=0 VDS<VDSAT VGS>VT Oxide Source Drain (p+) (p+) n+ n+ y Channel x x=0 x=L Substrate (p-Si) Depletion region VB=0 • 푉푐(푥): Channel voltage with respect to the source at position 푥. • Boundary Conditions: 푉푐 푥 = 0 = 푉푆 = 0; 푉푐 푥 = 퐿 = 푉퐷푆 ECE315 / ECE515 Linear Mode (Contd.) 푄푑: the charge density along the direction of current = W퐶표푥[푉퐺푆 − 푉푇] where, W = width of the channel and WCox is the capacitance per unit length yd Drain end dx Channel Source end • Now, since the channel potential varies from 0 at source to VDS at the drain 푄푑 푥 = 푊퐶표푥 푉퐺푆 − 푉푐(푥) − 푉푇 , where, Vc(x) = channel potential at 푥. • Subsequently we can write: 퐼퐷 푥 = 푄푑 푥 . 푣 , where, 푣 = velocity of charge (m/s) ECE315 / ECE515 Linear Mode (Contd.) 푣 = 휇푛퐸 ; where, 휇푛 = mobility of charge carriers (electron) dV E = electric field in the channel given by: Ex () dx dV Therefore, I()() x WC V V x V D ox GS c T n dx • Applying the boundary conditions for 푉푐(푥) we can write: xL VV DS IxI().().