NOP (code)

Top View

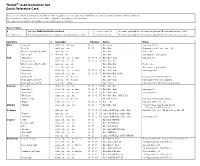

- X86 Assembly Language Reference Manual

- 80C186xl 80C188xl 16-Bit High-Integration Embedded

- SH-4 32-Bit CPU Core Architecture

- Intel X86 Assembly Language Cheat Sheet

- Armv6-M Architecture Reference Manual

- Pipelined MIPS

- Hardware and Instruction Set Architecture Simple Computer

- Tms320c28x CPU and Instruction Set Reference Guide

- Instruction Set Architecture

- Nios II Classic Processor Reference Guide

- Tms320c28x Assembly Language Tools V18.1.0.LTS User's Guide

- Lecture 09: RISC-V Pipeline Implementa8on

- HCS12 Reference Manual

- The RISC-V Instruction Set Manual Volume I: Unprivileged ISA Document Version 20190608-Base-Ratified

- MIPS Processor Implementation

- PPC Instruction Detail

- UNIVERSITY of CALIFORNIA, SAN DIEGO JIT Spraying Threats on ARM and Defense by Diversification a Dissertation Submitted in Parti

- SPARC Assembly Language Reference Manual