HCS12 Reference Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

EMEA Arrow EMEA Design Partner Network Catalogue

EMEA Arrow EMEA Design Partner Network Catalogue [email protected] Engineering Solutions Center Expertise | Enablement | Support The mission of Arrow’s Engineering Solutions Center is to support the field team in their design activities ranging from NPI proposals, consultancy in complex areas like software, IoT, FPGAs, high-end to complete system concepts and Arrow’s ready-to-use solutions. Through the TestDrive board loan program, the ESC provides many supplier development boards and Arrow developed solutions to enable quick design starts. Design, customization, prototyping and certification services are available from Arrow’s comprehensive 3rd Party Network. 2 Editorial Dear Arrow Colleagues, A warm welcome to what I hope you will find to be a useful and informative first edition of the Arrow EMEA Design Partner Catalogue. To stay competitive, our customers must continuously leverage leading edge technologies while shortening design cycles. Further, the majority of today’s innovations are happening at the level of software, applications, sensing capabilities, connectivity and security. These dynamics require new skills and capabilities that our customers may lack. This is where the Arrow EMEA Design Partner Network can help. Our partners provide immediate access to pre-screened, Minimize design time qualified, and certified third-party design services companies. Arrow’s network of some of the best and speed time-to-market engineering design services companies can save your customers time and money and allow them to bring by enabling the Arrow products to market faster. Partners can support them EMEA Partner Network all the way from specification development to turnkey board design or be an extension to their engineering to get involved early in team. -

Superh RISC Engine SH-1/SH-2

SuperH RISC Engine SH-1/SH-2 Programming Manual September 3, 1996 Hitachi America Ltd. Notice When using this document, keep the following in mind: 1. This document may, wholly or partially, be subject to change without notice. 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi’s permission. 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user’s unit according to this document. 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi’s semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein. 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd. 6. MEDICAL APPLICATIONS: Hitachi’s products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi’s sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi’s products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS. Introduction The SuperH RISC engine family incorporates a RISC (Reduced Instruction Set Computer) type CPU. A basic instruction can be executed in one clock cycle, realizing high performance operation. A built-in multiplier can execute multiplication and addition as quickly as DSP. -

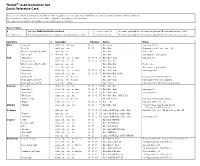

Thumb® 16-Bit Instruction Set Quick Reference Card

Thumb® 16-bit Instruction Set Quick Reference Card This card lists all Thumb instructions available on Thumb-capable processors earlier than ARM®v6T2. In addition, it lists all Thumb-2 16-bit instructions. The instructions shown on this card are all 16-bit in Thumb-2, except where noted otherwise. All registers are Lo (R0-R7) except where specified. Hi registers are R8-R15. Key to Tables § See Table ARM architecture versions. <loreglist+LR> A comma-separated list of Lo registers. plus the LR, enclosed in braces, { and }. <loreglist> A comma-separated list of Lo registers, enclosed in braces, { and }. <loreglist+PC> A comma-separated list of Lo registers. plus the PC, enclosed in braces, { and }. Operation § Assembler Updates Action Notes Move Immediate MOVS Rd, #<imm> N Z Rd := imm imm range 0-255. Lo to Lo MOVS Rd, Rm N Z Rd := Rm Synonym of LSLS Rd, Rm, #0 Hi to Lo, Lo to Hi, Hi to Hi MOV Rd, Rm Rd := Rm Not Lo to Lo. Any to Any 6 MOV Rd, Rm Rd := Rm Any register to any register. Add Immediate 3 ADDS Rd, Rn, #<imm> N Z C V Rd := Rn + imm imm range 0-7. All registers Lo ADDS Rd, Rn, Rm N Z C V Rd := Rn + Rm Hi to Lo, Lo to Hi, Hi to Hi ADD Rd, Rd, Rm Rd := Rd + Rm Not Lo to Lo. Any to Any T2 ADD Rd, Rd, Rm Rd := Rd + Rm Any register to any register. Immediate 8 ADDS Rd, Rd, #<imm> N Z C V Rd := Rd + imm imm range 0-255. -

MEK6800D2 Manual 2Ed 1977.Pdf

MOTOROLA Semiconductor Products Inc. MEK6800D2 MANUAL Circuit diagrams external to Motorola products are included as a means of illustrating typical Microprocessor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this manual has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others. Motorola reserves the right to change specifications without notice. EXORciser, JBUG and MINlbug are trademarks of Motorola Inc. Second Edition © MOTOROLA INC., 1977 First Edition © 1976 "All Rights Reserved" Printed in U.S.A. TABLE OF CONTENTS CHAPTER 1: Introduction 1-1 General Description and Capability . 1-1 1-2 Preparation for Use . 1-4 1-2.1 Construction Hints ..................................................... 1-5 1-3 Start-up Procedure . 1-6 1-4 Operating Procedures . 1-6 1-4.1 Memory Examine and Change ............................................ 1-7 1-4.2 Escape (Abort) ........................................................ 1-7 1-4.3 Register Display ....................................................... 1-7 1-4.4 Go to User Program .................................................... 1-9 1-4.5 Punch from Memory to Tape ............................................. 1-9 1-4.6 Load from Tape to Memory ............................................. -

Readingsample

Embedded Robotics Mobile Robot Design and Applications with Embedded Systems Bearbeitet von Thomas Bräunl Neuausgabe 2008. Taschenbuch. xiv, 546 S. Paperback ISBN 978 3 540 70533 8 Format (B x L): 17 x 24,4 cm Gewicht: 1940 g Weitere Fachgebiete > Technik > Elektronik > Robotik Zu Inhaltsverzeichnis schnell und portofrei erhältlich bei Die Online-Fachbuchhandlung beck-shop.de ist spezialisiert auf Fachbücher, insbesondere Recht, Steuern und Wirtschaft. Im Sortiment finden Sie alle Medien (Bücher, Zeitschriften, CDs, eBooks, etc.) aller Verlage. Ergänzt wird das Programm durch Services wie Neuerscheinungsdienst oder Zusammenstellungen von Büchern zu Sonderpreisen. Der Shop führt mehr als 8 Millionen Produkte. CENTRAL PROCESSING UNIT . he CPU (central processing unit) is the heart of every embedded system and every personal computer. It comprises the ALU (arithmetic logic unit), responsible for the number crunching, and the CU (control unit), responsible for instruction sequencing and branching. Modern microprocessors and microcontrollers provide on a single chip the CPU and a varying degree of additional components, such as counters, timing coprocessors, watchdogs, SRAM (static RAM), and Flash-ROM (electrically erasable ROM). Hardware can be described on several different levels, from low-level tran- sistor-level to high-level hardware description languages (HDLs). The so- called register-transfer level is somewhat in-between, describing CPU compo- nents and their interaction on a relatively high level. We will use this level in this chapter to introduce gradually more complex components, which we will then use to construct a complete CPU. With the simulation system Retro [Chansavat Bräunl 1999], [Bräunl 2000], we will be able to actually program, run, and test our CPUs. -

Reverse Engineering X86 Processor Microcode

Reverse Engineering x86 Processor Microcode Philipp Koppe, Benjamin Kollenda, Marc Fyrbiak, Christian Kison, Robert Gawlik, Christof Paar, and Thorsten Holz, Ruhr-University Bochum https://www.usenix.org/conference/usenixsecurity17/technical-sessions/presentation/koppe This paper is included in the Proceedings of the 26th USENIX Security Symposium August 16–18, 2017 • Vancouver, BC, Canada ISBN 978-1-931971-40-9 Open access to the Proceedings of the 26th USENIX Security Symposium is sponsored by USENIX Reverse Engineering x86 Processor Microcode Philipp Koppe, Benjamin Kollenda, Marc Fyrbiak, Christian Kison, Robert Gawlik, Christof Paar, and Thorsten Holz Ruhr-Universitat¨ Bochum Abstract hardware modifications [48]. Dedicated hardware units to counter bugs are imperfect [36, 49] and involve non- Microcode is an abstraction layer on top of the phys- negligible hardware costs [8]. The infamous Pentium fdiv ical components of a CPU and present in most general- bug [62] illustrated a clear economic need for field up- purpose CPUs today. In addition to facilitate complex and dates after deployment in order to turn off defective parts vast instruction sets, it also provides an update mechanism and patch erroneous behavior. Note that the implementa- that allows CPUs to be patched in-place without requiring tion of a modern processor involves millions of lines of any special hardware. While it is well-known that CPUs HDL code [55] and verification of functional correctness are regularly updated with this mechanism, very little is for such processors is still an unsolved problem [4, 29]. known about its inner workings given that microcode and the update mechanism are proprietary and have not been Since the 1970s, x86 processor manufacturers have throughly analyzed yet. -

Pipeliningpipelining

ChapterChapter 99 PipeliningPipelining Jin-Fu Li Department of Electrical Engineering National Central University Jungli, Taiwan Outline ¾ Basic Concepts ¾ Data Hazards ¾ Instruction Hazards Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 2 Content Coverage Main Memory System Address Data/Instruction Central Processing Unit (CPU) Operational Registers Arithmetic Instruction and Cache Logic Unit Sets memory Program Counter Control Unit Input/Output System Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 3 Basic Concepts ¾ Pipelining is a particularly effective way of organizing concurrent activity in a computer system ¾ Let Fi and Ei refer to the fetch and execute steps for instruction Ii ¾ Execution of a program consists of a sequence of fetch and execute steps, as shown below I1 I2 I3 I4 I5 F1 E1 F2 E2 F3 E3 F4 E4 F5 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 4 Hardware Organization ¾ Consider a computer that has two separate hardware units, one for fetching instructions and another for executing them, as shown below Interstage Buffer Instruction fetch Execution unit unit Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 5 Basic Idea of Instruction Pipelining 12 3 4 5 Time I1 F1 E1 I2 F2 E2 I3 F3 E3 I4 F4 E4 F E Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 6 A 4-Stage Pipeline 12 3 4 567 Time I1 F1 D1 E1 W1 I2 F2 D2 E2 W2 I3 F3 D3 E3 W3 I4 F4 D4 E4 W4 D: Decode F: Fetch Instruction E: Execute W: Write instruction & fetch operation results operands B1 B2 B3 Advanced Reliable Systems (ARES) Lab. -

Freescale.Com

MC9S08QE32 MC9S08QE16 Reference Manual Related Documentation: HCS08 Microcontrollers • MC9S08QE32 (Data Sheet) Contains pin assignments and diagrams, all electrical specifications, and mechanical drawing outlines. Find the most current versions of all documents at: http://www.freescale.com MC9S08QE32RM Rev. 3 9/2011 freescale.com MC9S08QE32 Features Features – ACMPx — Two analog comparators with selectable interrupt • 8-Bit HCS08 Central Processor Unit (CPU) on rising, falling, or either edge of comparator output; – Up to 50.33 MHz HCS08 CPU at 3.6V to 2.4V, 40 MHz CPU compare option to fixed internal bandgap reference voltage; at 2.4 V to 2.1 V and 20 MHz CPU at 2.1 V to 1.8 V across outputs can be optionally routed to TPM module; operation in temperature range of –40 °C to 85 °C stop3 – HC08 instruction set with added BGND instruction – SCIx — Two serial communications interface modules with – Support for up to 32 interrupt/reset sources optional 13-bit break; full duplex non-return to zero (NRZ); •On-Chip Memory LIN master extended break generation; LIN slave extended – Flash read/program/erase over full operating voltage and break detection; wake up on active edge temperature – SPI — One serial peripheral interface; full-duplex or – Random-access memory (RAM) single-wire bidirectional; double-buffered transmit and – Security circuitry to prevent unauthorized access to RAM and receive; master or slave mode; MSB-first or LSB-first shifting flash contents – IIC — One IIC; up to 100 kbps with maximum bus loading; • Power-Saving Modes multi-master -

An Introduction to Openvg™ FTF-AUT-F0465

An Introduction to OpenVG™ FTF-AUT-F0465 Oliver Tian | Auto FAE M A Y . 2 0 1 4 TM External Use Agenda • Trend of Graphics in Vehicle • Roadmap of Cluster • Introduction of Rainbow/Vybrid • OpenVG Scenario • Development Ecosystem • Conclusion TM External Use 1 Trend of Graphics in Vehicle TM External Use 2 The Connected Vehicle Infotainment + Communication + Security • Consumer electronics trends are dictating features in the car • Always connected, applications driven, advanced graphics • Infotainment systems becoming battleground for Auto differentiation • As more connected systems get introduced into the vehicle, the need for security is critical − Increasing external communication features (Bluetooth, TPMS, Ethernet, Wi-Fi, etc). − Future interface for vehicle-to-vehicle and vehicle-to-infrastructure. TM External Use 3 Mobility for Everyone Affordable Solutions for Emerging Markets • 100M vehicles annually forecasted before 2020, on top of motorcycle & e-bike growth • 80% of quantity growth after 2015 happening in emerging markets • Safety and emissions reduction are key for a sustainable development Source: IHS Automotive, February 2014 TM External Use 4 More, More, More for Less, Less, Less More performance, more embedded memory, more safety for less cost, less power and less development effort More • Electronic complexity • ECUs per car (50+) • MCUs per car (100+) • In-car Wi-Fi ® (7.2Mbps and 3.7Bpcs by 2017) iSuppli Less Reuse • Other markets have less critical applications • Some automotive specific challenges TM External Use 5 Today’s Car • Complex computerized control − Millions of lines of code, from multiple vendors − Dozens of distinct ECUs, from multiple vendors • Shared internal networking (e.g., CAN, FlexRay) − Increasing external communications features . -

Cyclone LC Programmers User Manual Purchase Agreement

Cyclone LC Programmers User Manual Purchase Agreement P&E Microcomputer Systems, Inc. reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. P&E Microcomputer Systems, Inc. does not assume any liability arising out of the application or use of any product or circuit described herein. This software and accompanying documentation are protected by United States Copyright law and also by International Treaty provisions. Any use of this software in violation of copyright law or the terms of this agreement will be prosecuted. All the software described in this document is copyrighted by P&E Microcomputer Systems, Inc. Copyright notices have been included in the software. P&E Microcomputer Systems authorizes you to make archival copies of the software and documentation for the sole purpose of back-up and protecting your investment from loss. Under no circumstances may you copy this software or documentation for the purpose of distribution to others. Under no conditions may you remove the copyright notices from this software or documentation. This software may be used by one person on as many computers as that person uses, provided that the software is never used on two computers at the same time. P&E expects that group programming projects making use of this software will purchase a copy of the software and documentation for each user in the group. Contact P&E for volume discounts and site licensing agreements. P&E Microcomputer Systems does not assume any liability for the use of this software beyond the original purchase price of the software. -

CFPRM, Coldfire ® Family Programmer™S

ColdFire® Family Programmer’s Reference Manual Document Number: CFPRM Rev. 3 03/2005 How to Reach Us: Home Page: www.freescale.com E-mail: [email protected] USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 Information in this document is provided solely to enable system and +1-800-521-6274 or +1-480-768-2130 software implementers to use Freescale Semiconductor products. There are [email protected] no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the Europe, Middle East, and Africa: information in this document. Freescale Halbleiter Deutschland GmbH Technical Information Center Freescale Semiconductor reserves the right to make changes without further Schatzbogen 7 notice to any products herein. Freescale Semiconductor makes no warranty, 81829 Muenchen, Germany representation or guarantee regarding the suitability of its products for any +44 1296 380 456 (English) particular purpose, nor does Freescale Semiconductor assume any liability +46 8 52200080 (English) arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or +49 89 92103 559 (German) incidental damages. “Typical” parameters that may be provided in Freescale +33 1 69 35 48 48 (French) Semiconductor data sheets and/or specifications can and do vary in different [email protected] applications and actual performance may vary over time. All operating parameters, including “Typicals”, must be validated for each customer Japan: application by customer’s technical experts. Freescale Semiconductor does Freescale Semiconductor Japan Ltd. -

Security Target RUGGEDCOM ROS V4.2.2.F 1 2 3 4 5 6 7

Introduction 1 Conformance Claims 2 Security Problem 3 Security Target Security Objectives for the Operational Environment 4 RUGGEDCOM ROS v4.2.2.F Extended Components 5 Security Requirements 6 TOE Summary Specification 7 Conformance Claims Rationale 8 Acronyms and Terms 9 Reference Guide 08/2018 RC1407-EN-01 Reference Guide Copyright © 2018 Siemens Canada Ltd Dissemination or reproduction of this document, or evaluation and communication of its contents, is permitted. Disclaimer Of Liability Siemens has verified the contents of this document against the hardware and/or software described. However, deviations between the product and the documentation may exist. Siemens shall not be liable for any errors or omissions contained herein or for consequential damages in connection with the furnishing, performance, or use of this material. The information given in this document is reviewed regularly and any necessary corrections will be included in subsequent editions. We appreciate any suggested improvements. We reserve the right to make technical improvements without notice. Registered Trademarks RUGGEDCOM™ and ROS™ are trademarks of Siemens Canada Ltd. Other designations in this manual might be trademarks whose use by third parties for their own purposes would infringe the rights of the owner. Third Party Copyrights Siemens recognizes the following third party copyrights: • Copyright © 2004 GoAhead Software, Inc. All Rights Reserved. Open Source RUGGEDCOM ROS contains Open Source Software. For license conditions, refer to the associated License Conditions document. Security Information Siemens provides products and solutions with industrial security functions that support the secure operation of plants, machines, equipment and/or networks. They are important components in a holistic industrial security concept.