Internal Memory Memory Cell

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 3 Semiconductor Memories

Chapter 3 Semiconductor Memories Jin-Fu Li Department of Electrical Engineering National Central University Jungli, Taiwan Outline Introduction Random Access Memories Content Addressable Memories Read Only Memories Flash Memories Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 2 Overview of Memory Types Semiconductor Memories Read/Write Memory or Random Access Memory (RAM) Read Only Memory (ROM) Random Access Non-Random Access Memory (RAM) Memory (RAM) •Mask (Fuse) ROM •Programmable ROM (PROM) •Erasable PROM (EPROM) •Static RAM (SRAM) •FIFO/LIFO •Electrically EPROM (EEPROM) •Dynamic RAM (DRAM) •Shift Register •Flash Memory •Register File •Content Addressable •Ferroelectric RAM (FRAM) Memory (CAM) •Magnetic RAM (MRAM) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 3 Memory Elements – Memory Architecture Memory elements may be divided into the following categories Random access memory Serial access memory Content addressable memory Memory architecture 2m+k bits row decoder row decoder 2n-k words row decoder row decoder column decoder k column mux, n-bit address sense amp, 2m-bit data I/Os write buffers Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 4 1-D Memory Architecture S0 S0 Word0 Word0 S1 S1 Word1 Word1 S2 S2 Word2 Word2 A0 S3 S3 A1 Decoder Ak-1 Sn-2 Storage Sn-2 Wordn-2 element Wordn-2 Sn-1 Sn-1 Wordn-1 Wordn-1 m-bit m-bit Input/Output Input/Output n select signals are reduced n select signals: S0-Sn-1 to k address signals: A0-Ak-1 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 5 Memory Architecture S0 Word0 Wordi-1 S1 A0 A1 Ak-1 Row Decoder Sn-1 Wordni-1 A 0 Column Decoder Aj-1 Sense Amplifier Read/Write Circuit m-bit Input/Output Advanced Reliable Systems (ARES) Lab. -

Error Detection and Correction Methods for Memories Used in System-On-Chip Designs

International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-8, Issue-2S2, January 2019 Error Detection and Correction Methods for Memories used in System-on-Chip Designs Gunduru Swathi Lakshmi, Neelima K, C. Subhas ABSTRACT— Memory is the basic necessity in any SoC Static Random Access Memory (SRAM): It design. Memories are classified into single port memory and consists of a latch or flipflop to store each bit of multiport memory. Multiport memory has ability to source more memory and it does not required any refresh efficient execution of operation and high speed performance operation. SRAM is mostly used in cache memory when compared to single port. Testing of semiconductor memories is increasing because of high density of current in the and in hand-held devices. It has advantages like chips. Due to increase in embedded on chip memory and memory high speed and low power consumption. It has density, the number of faults grow exponentially. Error detection drawback like complex structure and expensive. works on concept of redundancy where extra bits are added for So, it is not used for high capacity applications. original data to detect the error bits. Error correction is done in Read Only Memory (ROM): It is a non-volatile memory. two forms: one is receiver itself corrects the data and other is It can only access data but cannot modify data. It is of low receiver sends the error bits to sender through feedback. Error detection and correction can be done in two ways. One is Single cost. Some applications of ROM are scanners, ID cards, Fax bit and other is multiple bit. -

Low Voltage, One-Time Programmable, Read-Only Memory

Features • Fast read access time – 90ns • Dual voltage range operation – Low voltage power supply range, 3.0V to 3.6V, or – Standard power supply range, 5V 10% • Compatible with JEDEC standard Atmel® AT27C512R • Low-power CMOS operation – 20µA max standby (less than 1µA, typical) for VCC = 3.6V – 29mW max active at 5MHz for VCC = 3.6V 512K (64K x 8) • JEDEC standard package – 32-lead PLCC Low Voltage, • High-reliability CMOS technology One-time – 2,000V ESD protection Programmable, – 200mA latchup immunity • Rapid programming algorithm – 100µs/byte (typical) Read-only Memory • CMOS- and TTL-compatible inputs and outputs – JEDEC standard for LVTTL • Integrated product identification code Atmel AT27LV512A • Industrial temperature range • Green (Pb/halide-free) packaging option 1. Description The Atmel AT27LV512A is a high-performance, low-power, low-voltage, 524,288-bit, one- time programmable, read-only memory (OTP EPROM) organized as 64K by 8 bits. It requires only one supply in the range of 3.0 to 3.6V in normal read mode operation, making it ideal for fast, portable systems using battery power. The Atmel innovative design techniques provide fast speeds that rival 5V parts, while keep- ing the low power consumption of a 3.3V supply. At VCC = 3.0V, any byte can be accessed in less than 90ns. With a typical power dissipation of only 18mW at 5MHz and VCC = 3.3V, the AT27LV512A consumes less than one-fifth the power of a standard, 5V EPROM. Standby mode supply current is typically less than 1µA at 3.3V. The AT27LV512A is available in industry-standard, JEDEC-approved, one-time programmable (OTP) PLCC package. -

Lecture 27 Semiconductor Memory: DRAM and Non-Volatile Memory Administrivia

Lecture 27 Semiconductor Memory: DRAM and Non-Volatile Memory Digital Integrated Circuits Interconnect © Prentice Hall 2000 Administrivia l Today: Project phase 3 announcement. l Poster Session Tu 5/8 1-4pm » Location BWRC, 2108 Allston Way l Last lecture on Th 5/3 will cover issues in IC design Digital Integrated Circuits Interconnect © Prentice Hall 2000 1 Lectures Last l ROM and SRAM Today l Introducing the project phase III l DRAM and Non-volatile Digital Integrated Circuits Interconnect © Prentice Hall 2000 Project Phase III A proposed SRAM cell! w/ Control Circuit Digital Integrated Circuits Interconnect © Prentice Hall 2000 2 Tasks l Explain the behavior of the cell in its global contents. Provide transient simulations to illustrate. l Identify weakness of the cell in terms of signal integrity and power dissipation. Quantify your statements. l Propose an implementation that improves power dissipation. Digital Integrated Circuits Interconnect © Prentice Hall 2000 Report l Report » Comparison, Selection, Electrical Design » Cell Layout, Timing Waveforms in SRAM, Simulation » Power and Estimation and Proposal for SRAM power reduction l 3 slides on poster, each of which represents one of the tasks of the previous slide » Explanation of cell operation, comparison, design » Cell Operation in SRAM, Waveforms, Simulation » Proposal of improved SRAM implementation (from a power perspective) Digital Integrated Circuits Interconnect © Prentice Hall 2000 3 SEMICONDUCTOR MEMORIES Digital Integrated Circuits Interconnect © Prentice Hall 2000 3-Transistor DRAM Cell BL1 BL2 WWL WWL RWL RWL X X M3 VDD-VT M2 M1 VDD BL1 CS BL2 VDD-VT DV No constraints on device ratios Reads are non-destructive Value stored at node X when writing a “1” = VWWL-VTn Digital Integrated Circuits Interconnect © Prentice Hall 2000 4 3T-DRAM — Layout BL2 BL1 GND RWL M3 M2 WWL M1 Digital Integrated Circuits Interconnect © Prentice Hall 2000 1-Transistor DRAM Cell BL WL Write "1" Read "1" WL 1 M C X S GND VDD-VT V BL DD VDD/2 VDD/2 CBL sensing Write: CS is charged or discharged by asserting WL and BL. -

Nanotechnology Trends in Nonvolatile Memory Devices

IBM Research Nanotechnology Trends in Nonvolatile Memory Devices Gian-Luca Bona [email protected] IBM Research, Almaden Research Center © 2008 IBM Corporation IBM Research The Elusive Universal Memory © 2008 IBM Corporation IBM Research Incumbent Semiconductor Memories SRAM Cost NOR FLASH DRAM NAND FLASH Attributes for universal memories: –Highest performance –Lowest active and standby power –Unlimited Read/Write endurance –Non-Volatility –Compatible to existing technologies –Continuously scalable –Lowest cost per bit Performance © 2008 IBM Corporation IBM Research Incumbent Semiconductor Memories SRAM Cost NOR FLASH DRAM NAND FLASH m+1 SLm SLm-1 WLn-1 WLn WLn+1 A new class of universal storage device : – a fast solid-state, nonvolatile RAM – enables compact, robust storage systems with solid state reliability and significantly improved cost- performance Performance © 2008 IBM Corporation IBM Research Non-volatile, universal semiconductor memory SL m+1 SL m SL m-1 WL n-1 WL n WL n+1 Everyone is looking for a dense (cheap) crosspoint memory. It is relatively easy to identify materials that show bistable hysteretic behavior (easily distinguishable, stable on/off states). IBM © 2006 IBM Corporation IBM Research The Memory Landscape © 2008 IBM Corporation IBM Research IBM Research Histogram of Memory Papers Papers presented at Symposium on VLSI Technology and IEDM; Ref.: G. Burr et al., IBM Journal of R&D, Vol.52, No.4/5, July 2008 © 2008 IBM Corporation IBM Research IBM Research Emerging Memory Technologies Memory technology remains an -

Semiconductor Memories

Semiconductor Memories Prof. MacDonald Types of Memories! l" Volatile Memories –" require power supply to retain information –" dynamic memories l" use charge to store information and require refreshing –" static memories l" use feedback (latch) to store information – no refresh required l" Non-Volatile Memories –" ROM (Mask) –" EEPROM –" FLASH – NAND or NOR –" MRAM Memory Hierarchy! 100pS RF 100’s of bytes L1 1nS SRAM 10’s of Kbytes 10nS L2 100’s of Kbytes SRAM L3 100’s of 100nS DRAM Mbytes 1us Disks / Flash Gbytes Memory Hierarchy! l" Large memories are slow l" Fast memories are small l" Memory hierarchy gives us illusion of large memory space with speed of small memory. –" temporal locality –" spatial locality Register Files ! l" Fastest and most robust memory array l" Largest bit cell size l" Basically an array of large latches l" No sense amps – bits provide full rail data out l" Often multi-ported (i.e. 8 read ports, 2 write ports) l" Often used with ALUs in the CPU as source/destination l" Typically less than 10,000 bits –" 32 32-bit fixed point registers –" 32 60-bit floating point registers SRAM! l" Same process as logic so often combined on one die l" Smaller bit cell than register file – more dense but slower l" Uses sense amp to detect small bit cell output l" Fastest for reads and writes after register file l" Large per bit area costs –" six transistors (single port), eight transistors (dual port) l" L1 and L2 Cache on CPU is always SRAM l" On-chip Buffers – (Ethernet buffer, LCD buffer) l" Typical sizes 16k by 32 Static Memory -

Via-Programmable Read-Only Memory Design for Full Code Coverage Using a Dynamic Bit-Line Shielding Technique

Via-Programmable Read-Only Memory Design for Full Code Coverage Using A Dynamic Bit-Line Shielding Technique Meng-Fan Chang1, 2, Ding-Ming Kwai2, and Kuei-Ann Wen1 1 Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan 2 Intellectual Property Library Company, Hsinchu, Taiwan [email protected] Abstract 0-cell 1-cell 0-cell Crosstalk between bit lines leads to read-1 failure Metal-3 (BL) in a high-speed via-programmable read only memory (ROM) and limits the coverage of applicable code Via-2 (Code) patterns. Due to the fluctuations in bit-line intrinsic Metal-2 and coupling capacitances, the amount of noise coupled to a selected bit line may vary, resulting in the Via-1 reduction of sensing margin. In this paper, we propose a dynamic bit-line shielding (DBS) technique, suitable Metal-1 to be implemented in compliable ROM, to eliminate the Contact crosstalk-induced read failure and to achieve full code coverage. Experiments of the 256Kb instances with Diffusion Diffusion Diffusion and without the DBS circuit were undertaken using STI STI STI STI 0.25µm and 0.18µm standard CMOS processes. The test results demonstrate the read-1 failures and Fig. 1. Cross-sectional view of ROM array with via-2 confirm that the DBS technique can remove them codes and metal-3 bit lines. successfully, allowing the ROM to operate under a wide range of supply voltage. sectional view of the memory array with via-2 codes 1. Introduction and metal-3 bit lines. This leads to more severe bit-line crosstalk, since the contact and via at the lower levels Mask-programmable read-only memory (ROM) must be stacked and the metal islands for them to land macros are commonly embedded into system-on-chip upon contribute considerable side-wall capacitances to (SoC) designs today. -

Refresh Operation and Semi-Conductor Rom Memories

REFRESH OPERATION AND SEMI-CONDUCTOR ROM MEMORIES The Refresh control block periodically generates Refresh, requests, causing the access control block to start a memory cycle in the normal way. This block allows the refresh operation by activating the Refresh Grant line. The access control block arbitrates between Memory Access requests and Refresh requests, with priority to Refresh requests in the case of a tie to ensure the integrity of the stored data. As soon as the Refresh control block receives the Refresh Grant signal, it activates the Refresh line. This causes the address multiplexer to select the Refresh counter as the source and its contents are thus loaded into the row address latches of all memory chips when the RAS signal is activated. During this time the R/ W line may be low, causing an inadvertent write operation. One way to prevent this is to use the Refresh line to control the decoder block to deactivate all the chip select lines. The rest of the refresh cycle is the same as in a normal cycle. At the end, the Refresh control block increments the refresh counter in preparation for the next Refresh cycle. Even though the row address has 8 bits, the Refresh counter need only be 7 bits wide because of the cell organization inside the memory chips. In a 64k x 1 memory chip, the 256x256 cell array actually consists of two 128x256 arrays. The low order 7 bits of the row address select a row from both arrays and thus the row from both arrays is refreshed! Ideally, the refresh operation should be transparent to the CPU. -

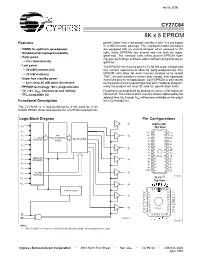

8K X 8 EPROM Features Powers Down Into a Low-Power Standby Mode

1CY 27C6 4 fax id: 3006 CY27C64 8K x 8 EPROM Features powers down into a low-power standby mode. It is packaged in a 600-mil-wide package. The reprogrammable packages • CMOS for optimum speed/power are equipped with an erasure window; when exposed to UV • Windowed for reprogrammability light, these EPROMs are erased and can then be repro- • High speed grammed. The memory cells utilize proven EPROM float- ing-gate technology and byte-wide intelligent programming al- — 0 ns (commercial) gorithms. • Low power The EPROM cell requires only 12.5V for the super voltage and — 40 mW (commercial) low–current requirements allow for gang programming. The — 30 mW (military) EPROM cells allow for each memory location to be tested 100%, as each location is written into, erased, and repeatedly • Super low standby power exercised prior to encapsulation. Each EPROM is also tested — Less than 85 mW when deselected for AC performance to guarantee that after customer program- • EPROM technology 100% programmable ming, the product will meet DC and AC specification limits. ± • 5V 10% VCC, commercial and military Reading is accomplished by placing an active LOW signal on • TTL-compatible I/O OE and CE. The contents of the memory location addressed by the address lines (A0 through A12) will become available on the output Functional Description lines (O0 through O7). The CY27C64 is a high-performance 8192 word by 8 bit CMOS PROM. When deselected, the CY27C64 automatically Logic Block Diagram Pin Configurations O7 DIP/CerDIP A0 Top View A1 VCC 1 28 VCC 2 27 A2 64K O6 A12 VCC ROW PROGRAMMABLE A7 3 26 NC A ADDRESS MULTIPLEXER 3 ARRAY A 4 6 25 A8 A5 5 24 A9 A4 A 6 4 23 A11 O5 A5 A3 7 22 OE A2 8 21 A10 A6 A1 9 27C64 20 CE ADDRESS A A7 O 0 10 19 O7 DECODER 4 O0 11 18 O6 A8 O1 12 17 O5 O 13 16 O A9 2 4 GND 14 15 O3 O A10 COLUMN 3 ADDRESS [1] 27C64-2 A11 PLCC Top View A 12 O2 4 POWER DOWN 32132 31 30 A A 6 5 29 8 A 5 6 28 A9 O1 A 4 7 27 A11 A 3 8 26 NC A 2 9 25 OE A A 1 10 24 10 A0 23 CE O0 11 27C64 NC 12 22 O7 O0 13 21 O6 14 15 16 17 18 19 20 CE OE 27C64-1 27C64-3 Notes: 1. -

Arduino Nano

Arduino Nano Arduino Nano Front Arduino Nano Rear Overview The Arduino Nano is a small, complete, and breadboard-friendly board based on the ATmega328 (Arduino Nano 3.0) or ATmega168 (Arduino Nano 2.x). It has more or less the same functionality of the Arduino Duemilanove, but in a different package. It lacks only a DC power jack, and works with a Mini-B USB cable instead of a standard one. The Nano was designed and is being produced by Gravitech. Schematic and Design Arduino Nano 3.0 (ATmega328): schematic, Eagle files. Arduino Nano 2.3 (ATmega168): manual (pdf), Eagle files. Note: since the free version of Eagle does not handle more than 2 layers, and this version of the Nano is 4 layers, it is published here unrouted, so users can open and use it in the free version of Eagle. Specifications: Microcontroller Atmel ATmega168 or ATmega328 Operating Voltage (logic 5 V level) Input Voltage 7-12 V (recommended) Input Voltage (limits) 6-20 V Digital I/O Pins 14 (of which 6 provide PWM output) Analog Input Pins 8 DC Current per I/O Pin 40 mA 16 KB (ATmega168) or 32 KB (ATmega328) of which 2 KB used by Flash Memory bootloader SRAM 1 KB (ATmega168) or 2 KB (ATmega328) EEPROM 512 bytes (ATmega168) or 1 KB (ATmega328) Clock Speed 16 MHz Dimensions 0.73" x 1.70" Power: The Arduino Nano can be powered via the Mini-B USB connection, 6-20V unregulated external power supply (pin 30), or 5V regulated external power supply (pin 27). -

Memory Basics

Memory Basics • RAM: Random Access Memory – historically defined as memory array with individual bit access – refers to memory with both Read and Write capabilities • ROM : Read Only Memory – no capabilities for “online” memory Write operations – Write typically requires high volt ages or erasing by UV light • Volatility of Memory – volatile memory loses data over time or when power is removed • RAM is volatile – non-volatile memory stores data even when power is removed • ROM is non-volatile • Static vs. Dynamic Memory – Static: holds data as long as power is applied (SRAM) – Dynamic: must be refreshed periodically (DRAM) ECE 410, Prof. A. Mason/Prof. F. Salem Lecture Notes 13.1 SRAM Basics • SRAM = Static Random Access Memory – Static: holds data as long as power is applied – Volatile: can not hold data if power is removed • Operation States – 3 states (modes) • hold • write WL • read • Basic 6T (transistor) SRAM Cell – bistable (cross-coupled) INVs for storage – access transistors MAL & MAR MAL MAR • access to stored data for read and write – word line, WL, controls access bit bit • WL = 0, hold operation • WL = 1, read or write operation ECE 410, Prof. A. Mason/Prof. F. Salem Lecture Notes 13.2 SRAM Operations • Hold – word line = 0, access transistors are OFF – data held in latch • Write WL – word line = 1, access tx are ON – new data (voltage) applied to bit and bit_bar – data in latch overwritten with new value MAL MAR • Read bit bit – word line = 1, access tx are ON – bit and bit_bar read by a sense amplifier • Sense Amplifier – basically a simple differential (transconductance) amplifier – comparing the difference between bit and bit_bar • if bit > bit_bar, output is 1 • if bit < bit_bar, output is 0 • allows output to be set quickly without fully charging/discharging bit line ECE 410, Prof. -

Memory We Have Already Mentioned That Digital Computer Works on Stored Programmed Concept Introduced by Von Neumann

www.getmyuni.com Memory We have already mentioned that digital computer works on stored programmed concept introduced by Von Neumann. We use memory to store the information, which includes both program and data. Due to several reasons, we have different kind of memories. We use different kind of memory at different level. The memory of computer is broadly categories into two categories: . Internal and . external Internal memory is used by CPU to perform task and external memory is used to store bulk information, which includes large software and data. Memory is used to store the information in digital form. The memory hierarchy is given by: . Register . Cache Memory . Main Memory . Magnetic Disk . Removable media (Magnetic tape) Register: This is a part of Central Processor Unit, so they reside inside the CPU. The information from main memory is brought to CPU and keep the information in register. Due to space and cost constraints, we have got a limited number of registers in a CPU. These are basically faster devices. Cache Memory: Cache memory is a storage device placed in between CPU and main memory. These are semiconductor memories. These are basically fast memory device, faster than main memory. We cannot have a big volume of cache memory due to its higher cost and some constraints of the CPU. Due to higher cost we cannot replace the whole main memory by faster memory. Generally, the most recently used information is kept in the cache memory. It is brought from the main memory and placed in the cache memory. Now days, we get CPU with internal cache.