Error Detection and Correction Methods for Memories Used in System-On-Chip Designs

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 3 Semiconductor Memories

Chapter 3 Semiconductor Memories Jin-Fu Li Department of Electrical Engineering National Central University Jungli, Taiwan Outline Introduction Random Access Memories Content Addressable Memories Read Only Memories Flash Memories Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 2 Overview of Memory Types Semiconductor Memories Read/Write Memory or Random Access Memory (RAM) Read Only Memory (ROM) Random Access Non-Random Access Memory (RAM) Memory (RAM) •Mask (Fuse) ROM •Programmable ROM (PROM) •Erasable PROM (EPROM) •Static RAM (SRAM) •FIFO/LIFO •Electrically EPROM (EEPROM) •Dynamic RAM (DRAM) •Shift Register •Flash Memory •Register File •Content Addressable •Ferroelectric RAM (FRAM) Memory (CAM) •Magnetic RAM (MRAM) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 3 Memory Elements – Memory Architecture Memory elements may be divided into the following categories Random access memory Serial access memory Content addressable memory Memory architecture 2m+k bits row decoder row decoder 2n-k words row decoder row decoder column decoder k column mux, n-bit address sense amp, 2m-bit data I/Os write buffers Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 4 1-D Memory Architecture S0 S0 Word0 Word0 S1 S1 Word1 Word1 S2 S2 Word2 Word2 A0 S3 S3 A1 Decoder Ak-1 Sn-2 Storage Sn-2 Wordn-2 element Wordn-2 Sn-1 Sn-1 Wordn-1 Wordn-1 m-bit m-bit Input/Output Input/Output n select signals are reduced n select signals: S0-Sn-1 to k address signals: A0-Ak-1 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 5 Memory Architecture S0 Word0 Wordi-1 S1 A0 A1 Ak-1 Row Decoder Sn-1 Wordni-1 A 0 Column Decoder Aj-1 Sense Amplifier Read/Write Circuit m-bit Input/Output Advanced Reliable Systems (ARES) Lab. -

Low Voltage, One-Time Programmable, Read-Only Memory

Features • Fast read access time – 90ns • Dual voltage range operation – Low voltage power supply range, 3.0V to 3.6V, or – Standard power supply range, 5V 10% • Compatible with JEDEC standard Atmel® AT27C512R • Low-power CMOS operation – 20µA max standby (less than 1µA, typical) for VCC = 3.6V – 29mW max active at 5MHz for VCC = 3.6V 512K (64K x 8) • JEDEC standard package – 32-lead PLCC Low Voltage, • High-reliability CMOS technology One-time – 2,000V ESD protection Programmable, – 200mA latchup immunity • Rapid programming algorithm – 100µs/byte (typical) Read-only Memory • CMOS- and TTL-compatible inputs and outputs – JEDEC standard for LVTTL • Integrated product identification code Atmel AT27LV512A • Industrial temperature range • Green (Pb/halide-free) packaging option 1. Description The Atmel AT27LV512A is a high-performance, low-power, low-voltage, 524,288-bit, one- time programmable, read-only memory (OTP EPROM) organized as 64K by 8 bits. It requires only one supply in the range of 3.0 to 3.6V in normal read mode operation, making it ideal for fast, portable systems using battery power. The Atmel innovative design techniques provide fast speeds that rival 5V parts, while keep- ing the low power consumption of a 3.3V supply. At VCC = 3.0V, any byte can be accessed in less than 90ns. With a typical power dissipation of only 18mW at 5MHz and VCC = 3.3V, the AT27LV512A consumes less than one-fifth the power of a standard, 5V EPROM. Standby mode supply current is typically less than 1µA at 3.3V. The AT27LV512A is available in industry-standard, JEDEC-approved, one-time programmable (OTP) PLCC package. -

Embedded DRAM

Embedded DRAM Raviprasad Kuloor Semiconductor Research and Development Centre, Bangalore IBM Systems and Technology Group DRAM Topics Introduction to memory DRAM basics and bitcell array eDRAM operational details (case study) Noise concerns Wordline driver (WLDRV) and level translators (LT) Challenges in eDRAM Understanding Timing diagram – An example References Slide 1 Acknowledgement • John Barth, IBM SRDC for most of the slides content • Madabusi Govindarajan • Subramanian S. Iyer • Many Others Slide 2 Topics Introduction to memory DRAM basics and bitcell array eDRAM operational details (case study) Noise concerns Wordline driver (WLDRV) and level translators (LT) Challenges in eDRAM Understanding Timing diagram – An example Slide 3 Memory Classification revisited Slide 4 Motivation for a memory hierarchy – infinite memory Memory store Processor Infinitely fast Infinitely large Cycles per Instruction Number of processor clock cycles (CPI) = required per instruction CPI[ ∞ cache] Finite memory speed Memory store Processor Finite speed Infinite size CPI = CPI[∞ cache] + FCP Finite cache penalty Locality of reference – spatial and temporal Temporal If you access something now you’ll need it again soon e.g: Loops Spatial If you accessed something you’ll also need its neighbor e.g: Arrays Exploit this to divide memory into hierarchy Hit L2 L1 (Slow) Processor Miss (Fast) Hit Register Cache size impacts cycles-per-instruction Access rate reduces Slower memory is sufficient Cache size impacts cycles-per-instruction For a 5GHz -

Semiconductor Memories

Semiconductor Memories Prof. MacDonald Types of Memories! l" Volatile Memories –" require power supply to retain information –" dynamic memories l" use charge to store information and require refreshing –" static memories l" use feedback (latch) to store information – no refresh required l" Non-Volatile Memories –" ROM (Mask) –" EEPROM –" FLASH – NAND or NOR –" MRAM Memory Hierarchy! 100pS RF 100’s of bytes L1 1nS SRAM 10’s of Kbytes 10nS L2 100’s of Kbytes SRAM L3 100’s of 100nS DRAM Mbytes 1us Disks / Flash Gbytes Memory Hierarchy! l" Large memories are slow l" Fast memories are small l" Memory hierarchy gives us illusion of large memory space with speed of small memory. –" temporal locality –" spatial locality Register Files ! l" Fastest and most robust memory array l" Largest bit cell size l" Basically an array of large latches l" No sense amps – bits provide full rail data out l" Often multi-ported (i.e. 8 read ports, 2 write ports) l" Often used with ALUs in the CPU as source/destination l" Typically less than 10,000 bits –" 32 32-bit fixed point registers –" 32 60-bit floating point registers SRAM! l" Same process as logic so often combined on one die l" Smaller bit cell than register file – more dense but slower l" Uses sense amp to detect small bit cell output l" Fastest for reads and writes after register file l" Large per bit area costs –" six transistors (single port), eight transistors (dual port) l" L1 and L2 Cache on CPU is always SRAM l" On-chip Buffers – (Ethernet buffer, LCD buffer) l" Typical sizes 16k by 32 Static Memory -

Via-Programmable Read-Only Memory Design for Full Code Coverage Using a Dynamic Bit-Line Shielding Technique

Via-Programmable Read-Only Memory Design for Full Code Coverage Using A Dynamic Bit-Line Shielding Technique Meng-Fan Chang1, 2, Ding-Ming Kwai2, and Kuei-Ann Wen1 1 Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan 2 Intellectual Property Library Company, Hsinchu, Taiwan [email protected] Abstract 0-cell 1-cell 0-cell Crosstalk between bit lines leads to read-1 failure Metal-3 (BL) in a high-speed via-programmable read only memory (ROM) and limits the coverage of applicable code Via-2 (Code) patterns. Due to the fluctuations in bit-line intrinsic Metal-2 and coupling capacitances, the amount of noise coupled to a selected bit line may vary, resulting in the Via-1 reduction of sensing margin. In this paper, we propose a dynamic bit-line shielding (DBS) technique, suitable Metal-1 to be implemented in compliable ROM, to eliminate the Contact crosstalk-induced read failure and to achieve full code coverage. Experiments of the 256Kb instances with Diffusion Diffusion Diffusion and without the DBS circuit were undertaken using STI STI STI STI 0.25µm and 0.18µm standard CMOS processes. The test results demonstrate the read-1 failures and Fig. 1. Cross-sectional view of ROM array with via-2 confirm that the DBS technique can remove them codes and metal-3 bit lines. successfully, allowing the ROM to operate under a wide range of supply voltage. sectional view of the memory array with via-2 codes 1. Introduction and metal-3 bit lines. This leads to more severe bit-line crosstalk, since the contact and via at the lower levels Mask-programmable read-only memory (ROM) must be stacked and the metal islands for them to land macros are commonly embedded into system-on-chip upon contribute considerable side-wall capacitances to (SoC) designs today. -

Refresh Operation and Semi-Conductor Rom Memories

REFRESH OPERATION AND SEMI-CONDUCTOR ROM MEMORIES The Refresh control block periodically generates Refresh, requests, causing the access control block to start a memory cycle in the normal way. This block allows the refresh operation by activating the Refresh Grant line. The access control block arbitrates between Memory Access requests and Refresh requests, with priority to Refresh requests in the case of a tie to ensure the integrity of the stored data. As soon as the Refresh control block receives the Refresh Grant signal, it activates the Refresh line. This causes the address multiplexer to select the Refresh counter as the source and its contents are thus loaded into the row address latches of all memory chips when the RAS signal is activated. During this time the R/ W line may be low, causing an inadvertent write operation. One way to prevent this is to use the Refresh line to control the decoder block to deactivate all the chip select lines. The rest of the refresh cycle is the same as in a normal cycle. At the end, the Refresh control block increments the refresh counter in preparation for the next Refresh cycle. Even though the row address has 8 bits, the Refresh counter need only be 7 bits wide because of the cell organization inside the memory chips. In a 64k x 1 memory chip, the 256x256 cell array actually consists of two 128x256 arrays. The low order 7 bits of the row address select a row from both arrays and thus the row from both arrays is refreshed! Ideally, the refresh operation should be transparent to the CPU. -

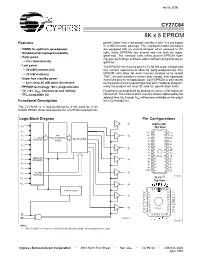

8K X 8 EPROM Features Powers Down Into a Low-Power Standby Mode

1CY 27C6 4 fax id: 3006 CY27C64 8K x 8 EPROM Features powers down into a low-power standby mode. It is packaged in a 600-mil-wide package. The reprogrammable packages • CMOS for optimum speed/power are equipped with an erasure window; when exposed to UV • Windowed for reprogrammability light, these EPROMs are erased and can then be repro- • High speed grammed. The memory cells utilize proven EPROM float- ing-gate technology and byte-wide intelligent programming al- — 0 ns (commercial) gorithms. • Low power The EPROM cell requires only 12.5V for the super voltage and — 40 mW (commercial) low–current requirements allow for gang programming. The — 30 mW (military) EPROM cells allow for each memory location to be tested 100%, as each location is written into, erased, and repeatedly • Super low standby power exercised prior to encapsulation. Each EPROM is also tested — Less than 85 mW when deselected for AC performance to guarantee that after customer program- • EPROM technology 100% programmable ming, the product will meet DC and AC specification limits. ± • 5V 10% VCC, commercial and military Reading is accomplished by placing an active LOW signal on • TTL-compatible I/O OE and CE. The contents of the memory location addressed by the address lines (A0 through A12) will become available on the output Functional Description lines (O0 through O7). The CY27C64 is a high-performance 8192 word by 8 bit CMOS PROM. When deselected, the CY27C64 automatically Logic Block Diagram Pin Configurations O7 DIP/CerDIP A0 Top View A1 VCC 1 28 VCC 2 27 A2 64K O6 A12 VCC ROW PROGRAMMABLE A7 3 26 NC A ADDRESS MULTIPLEXER 3 ARRAY A 4 6 25 A8 A5 5 24 A9 A4 A 6 4 23 A11 O5 A5 A3 7 22 OE A2 8 21 A10 A6 A1 9 27C64 20 CE ADDRESS A A7 O 0 10 19 O7 DECODER 4 O0 11 18 O6 A8 O1 12 17 O5 O 13 16 O A9 2 4 GND 14 15 O3 O A10 COLUMN 3 ADDRESS [1] 27C64-2 A11 PLCC Top View A 12 O2 4 POWER DOWN 32132 31 30 A A 6 5 29 8 A 5 6 28 A9 O1 A 4 7 27 A11 A 3 8 26 NC A 2 9 25 OE A A 1 10 24 10 A0 23 CE O0 11 27C64 NC 12 22 O7 O0 13 21 O6 14 15 16 17 18 19 20 CE OE 27C64-1 27C64-3 Notes: 1. -

SRAM Edram DRAM

Technology Challenges and Directions of SRAM, DRAM, and eDRAM Cell Scaling in Sub- 20nm Generations Jai-hoon Sim SK hynix, Icheon, Korea Outline 1. Nobody is perfect: Main memory & cache memory in the dilemma in sub-20nm era. 2. SRAM Scaling: Diet or Die. 6T SRAM cell scaling crisis & RDF problem. 3. DRAM Scaling: Divide and Rule. Unfinished 1T1C DRAM cell scaling and its technical direction. 4. eDRAM Story: Float like a DRAM & sting like a SRAM. Does logic based DRAM process work? 5. All for one. Reshaping DRAM with logic technology elements. 6. Conclusion. 2 Memory Hierarchy L1$ L2$ SRAM Higher Speed (< few nS) Working L3$ Better Endurance eDRAM Memory (>1x1016 cycles) Access Speed Access Stt-RAM Main Memory DRAM PcRAM ReRAM Lower Speed Bigger Size Storage Class Memory NAND Density 3 Technologies for Cache & Main Memories SRAM • 6T cell. • Non-destructive read. • Performance driven process Speed technology. eDRAM • Always very fast. • 1T-1C cell. • Destructive read and Write-back needed. • Leakage-Performance compromised process technology. Standby • Smaller than SRAM and faster than Density Power DRAM. DRAM • 1T-1C cell. • Destructive read and Write-back needed. • Leakage control driven process technology. • Not always fast. • Smallest cell and lowest cost per bit. 4 eDRAM Concept: Performance Gap Filler SRAM 20-30X Cell Size Cell eDRAM DRAM 50-100X Random Access Speed • Is there any high density & high speed memory solution that could be 100% integrated into logic SoC? 5 6T-SRAM Cell Operation VDD WL WL DVBL PU Read PG SN SN WL Icell PD BL VSS BL V SN BL BL DD SN PD Read Margin: Write PG PG V Write Margin: SS PU Time 6 DRAM’s Charge Sharing DVBL VS VBL Charge Sharing Write-back VPP WL CS CBL V BL DD 1 SN C V C V C C V S DD B 2 DD S B BL 1/2VDD Initial Charge After Charge Sharing DVBL T d 1 1 V BL SS DVBL VBL VBL VDD 1 CB / CS 2 VBBW Time 1 1 I t L RET if cell leakage included Cell select DVBL VDD 1 CB / CS 2 CS 7 DRAM Scalability Metrics BL Cell WL CS • Cell CS. -

Memory Basics

Memory Basics • RAM: Random Access Memory – historically defined as memory array with individual bit access – refers to memory with both Read and Write capabilities • ROM : Read Only Memory – no capabilities for “online” memory Write operations – Write typically requires high volt ages or erasing by UV light • Volatility of Memory – volatile memory loses data over time or when power is removed • RAM is volatile – non-volatile memory stores data even when power is removed • ROM is non-volatile • Static vs. Dynamic Memory – Static: holds data as long as power is applied (SRAM) – Dynamic: must be refreshed periodically (DRAM) ECE 410, Prof. A. Mason/Prof. F. Salem Lecture Notes 13.1 SRAM Basics • SRAM = Static Random Access Memory – Static: holds data as long as power is applied – Volatile: can not hold data if power is removed • Operation States – 3 states (modes) • hold • write WL • read • Basic 6T (transistor) SRAM Cell – bistable (cross-coupled) INVs for storage – access transistors MAL & MAR MAL MAR • access to stored data for read and write – word line, WL, controls access bit bit • WL = 0, hold operation • WL = 1, read or write operation ECE 410, Prof. A. Mason/Prof. F. Salem Lecture Notes 13.2 SRAM Operations • Hold – word line = 0, access transistors are OFF – data held in latch • Write WL – word line = 1, access tx are ON – new data (voltage) applied to bit and bit_bar – data in latch overwritten with new value MAL MAR • Read bit bit – word line = 1, access tx are ON – bit and bit_bar read by a sense amplifier • Sense Amplifier – basically a simple differential (transconductance) amplifier – comparing the difference between bit and bit_bar • if bit > bit_bar, output is 1 • if bit < bit_bar, output is 0 • allows output to be set quickly without fully charging/discharging bit line ECE 410, Prof. -

Application Note 170 Adding Nonvolatile SRAM Into Embedded Systems

Application Note 170 Adding Nonvolatile SRAM into Embedded Systems www.maxim-ic.com INTRODUCTION Dallas Semiconductor’s nonvolatile (NV) SRAMs are plastic encapsulated modules that combine an SRAM, a power control IC, and a battery to provide high performance NV memory. NV SRAMs are the only NV solution on the market that does not specify a maximum number of write cycles. Additionally, the interface remains the same as a standard SRAM, and the read and write access times remain similar to the SRAM used within the module. NV SRAMs are particularly well suited to microprocessor circuits because of their fast access times and the SRAM interface. External memory buses available on many microprocessors are intended for use with SRAM for data memory. Thus, due to the equivalent interfaces, NV SRAMs can simply replace an SRAM to provide NV storage in many applications. Often in the past, EPROM, EEPROM, and flash have been used for program memory space; however, NV SRAMs may also be used for program memory as well. This application note will show how to interface an NV SRAM to a microprocessor based system as either program or data memory, and list the advantages that using a NV SRAM will bring to the system compared to other NV memories currently available. DIFFERENCE BETWEEN EPROM, EEPROM, FLASH AND NV SRAM Although EPROM, EEPROM, Flash and NV SRAM are compatible NV storage solutions to some extent, accidentally choosing one that is a poor choice for a particular application can be crippling to a design. The main challenges that a microcontroller -

Digital Recorded Announcement Machine DRAM and EDRAM Guide

297-1001-527 DMS-100 Family Digital Recorded Announcement Machine DRAM and EDRAM Guide BASE09 and up Standard 13.06 August 1999 DMS-100 Family Digital Recorded Announcement Machine DRAM and EDRAM Guide Publication number: 297-1001-527 Product release: BASE09 and up Document release: Standard 13.06 Date: August 1999 1982, 1984, 1985, 1986, 1987, 1988, 1990, 1991, 1993, 1994, 1995, 1996, 1997, 1999 Northern Telecom All rights reserved Printed in the United States of America NORTHERN TELECOM CONFIDENTIAL: The information contained in this document is the property of Northern Telecom. Except as specifically authorized in writing by Northern Telecom, the holder of this document shall keep the information contained herein confidential and shall protect same in whole or in part from disclosure and dissemination to third parties and use same for evaluation, operation, and maintenance purposes only. Information is subject to change without notice. Northern Telecom reserves the right to make changes in design or components as progress in engineering and manufacturing may warrant. This equipment has been tested and found to comply with the limits for a Class A digital device pursuant to Part 15 of the FCC Rules, and the radio interference regulations of the Canadian Department of Communications. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at the user’s own expense. -

17. Semiconductor Memories

17. Semiconductor Memories Institute of Microelectronic Systems Overview •Introduction • Read Only Memory (ROM) • Nonvolatile Read/Write Memory (RWM) • Static Random Access Memory (SRAM) • Dynamic Random Access Memory (DRAM) •Summary Institute of Microelectronic 17: Semiconductor Memories Systems 2 Semiconductor Memory Classification Non-Volatile Memory Volatile Memory Read Only Memory Read/Write Memory Read/Write Memory (ROM) (RWM) Random Non-Random Mask-Programmable EPROM Access Access ROM E2PROM SRAM FIFO Programmable ROM FLASH DRAM LIFO Shift Register EPROM - Erasable Programmable ROM SRAM - Static Random Access Memory E2PROM - Electrically Erasable DRAM - Dynamic Random Access Memory Programmable ROM FIFO - First-In First-Out LIFO - Last-In First-Out Institute of Microelectronic 17: Semiconductor Memories Systems 3 Random Access Memory Array Organization Memory array • Memory storage cells • Address decoders Each memory cell • stores one bit of binary information (”0“ or ”1“ logic) • shares common connections with other cells: rows, columns Institute of Microelectronic 17: Semiconductor Memories Systems 4 Read Only Memory - ROM • Simple combinatorial Boolean network which produces a specific output for each input combination (address) • ”1“ bit stored - absence of an active transistor • ”0“ bit stored - presence of an active transistor • Organized in arrays of 2N words • Typical applications: • store the microcoded instructions set of a microprocessor • store a portion of the operation system for PCs • store the fixed programs for