Chapter 4 Gates and Circuits(With

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Transistor Circuit Guidebook Byron Wels TAB BOOKSBLUE RIDGE SUMMIT, PA

TAB BOOKS No. 470 34.95 By Byron Wels TransistorCircuit GuidebookByronWels TABBLUE RIDGE BOOKS SUMMIT,PA. 17214 Preface beforemeIa supposepioneer (along the my withintransistor firstthe many field.experiencewith wasother Weknown. World were using WarUnlike solid-stateIIsolid-state GIs) today's asdevices somewhat experimen- receivers marks of FIRST EDITION devicester,ownFirst, withsemiconductors! youwith a choice swipedwhichor tank. ofto a sealed,Here'sexperiment, pairThen ofhow encapsulated, you earphones we carefullywe did had it: from totookand construct the veryonenearest exoticof our the THIRDSECONDFIRST PRINTING-SEPTEMBER PRINTING-AUGUST PRINTING-JANUARY 1972 1970 1968 plane,wasyouAnphonesantenna. emptywound strung jeep,apart After toiletfull outand ofclippingas paper wire,unwoundhigh closelyrollandthe servedascatchthe far spaced.wire offas as itfrom a thewouldsafetyThe thecoil remaining-pin,magnetreach-for form, you inside.which stuckwire the Copyright © 1968by TAB BOOKS coatedNext,it into youneeded,a hunkribbons of -ofwooda razor -steel, soblade.the but point Oh,aItblued was noneprojected placedblade of the -quenchat so fancy right the pointplastic-bluedangles.of -, Reproduction or publicationPrinted inof the ofAmerica the United content States in any manner, with- themindfoundphoneground pin you,the was couldserved right not wired contact lacquerspotas toa onground blade, it. theblued.blade'sAconnector, pin,bayonet bluing,and stuck antennaand you hilt thecould coil.-deep other actuallyIfin ear- youthe isoutherein. assumed express -

Digital IC Listing

BELS Digital IC Report Package BELS Unit PartName Type Location ID # Price Type CMOS 74HC00, Quad 2-Input NAND Gate DIP-14 3 - A 500 0.24 74HCT00, Quad 2-Input NAND Gate DIP-14 3 - A 501 0.36 74HC02, Quad 2 Input NOR DIP-14 3 - A 417 0.24 74HC04, Hex Inverter, buffered DIP-14 3 - A 418 0.24 74HC04, Hex Inverter (buffered) DIP-14 3 - A 511 0.24 74HCT04, Hex Inverter (Open Collector) DIP-14 3 - A 512 0.36 74HC08, Quad 2 Input AND Gate DIP-14 3 - A 408 0.24 74HC10, Triple 3-Input NAND DIP-14 3 - A 419 0.31 74HC32, Quad OR DIP-14 3 - B 409 0.24 74HC32, Quad 2-Input OR Gates DIP-14 3 - B 543 0.24 74HC138, 3-line to 8-line decoder / demultiplexer DIP-16 3 - C 603 1.05 74HCT139, Dual 2-line to 4-line decoders / demultiplexers DIP-16 3 - C 605 0.86 74HC154, 4-16 line decoder/demulitplexer, 0.3 wide DIP - Small none 445 1.49 74HC154W, 4-16 line decoder/demultiplexer, 0.6wide DIP none 446 1.86 74HC190, Synchronous 4-Bit Up/Down Decade and Binary Counters DIP-16 3 - D 637 74HCT240, Octal Buffers and Line Drivers w/ 3-State outputs DIP-20 3 - D 643 1.04 74HC244, Octal Buffers And Line Drivers w/ 3-State outputs DIP-20 3 - D 647 1.43 74HCT245, Octal Bus Transceivers w/ 3-State outputs DIP-20 3 - D 649 1.13 74HCT273, Octal D-Type Flip-Flops w/ Clear DIP-20 3 - D 658 1.35 74HCT373, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 666 1.35 74HCT377, Octal D-Type Flip-Flops w/ Clock Enable DIP-20 3 - E 669 1.50 74HCT573, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 674 0.88 Type CMOS CD4000 Series CD4001, Quad 2-input -

50 Simple L.E.D. Circuits

50 Simple L.E.D. Circuits R.N. SOAR r de Historie v/d Radi OTH'IEK 50 SIMPLE L.E.D. CIRCUITS by R. N. SOAR BABANI PRESS The Publishing Division of Babani Trading and Finance Co. Ltd. The Grampians Shepherds Bush Road London W6 7NI- England Although every care is taken with the preparation of this book, the publishers or author will not be responsible in any way for any errors that might occur. © 1977 BA BAN I PRESS I.S.B.N. 0 85934 043 4 First Published December 1977 Printed and Manufactured in Great Britain by C. Nicholls & Co. Ltd. f t* -i. • v /“ ..... tr> CONTENTS U.V.H.R* Circuit Page No. 1 LED Pilot Light......................................... 7 2 LED Stereo Beacon.................................... 8 3 Stereo Decoder Mono/Sterco Indicator . 9 4 Subminiature LED Torch........................... 10 5 Low Voltage Low Current Supply............ 11 6 Microlight Indicator .................................. 12 7 Ultra Low Current LED Switching Indicator 13 8 LED Stroboscope....................................... 14 9 12 Volt Car Circuit Tester........................... 15 10 Two Colour LED......................................... 16 11 12 Volt Car “Fuse Blown” Indicator.......... 17 12 LED Continuity Tester............................... 17 13 LED Current Overload Indicator.............. 18 14 LED Current Range Indicator................... 20 15 1.5 Volt LED “Zener”................. '............ 22 16 Extending Zener Voltage........................... 22 17 Four Voltage Regulated Supply................. 23 18 PsychaLEDic Display.................................. 24 .19 Dual Colour Display.................................... 25 20 Dual Signal Device....................................... 26 21 LED Triple Signalling.................................. 27 22 Sub-Miniature Light Source for Model Railways . 28 23 Portable Television Protection Circuit . 29 24 Improved Portable TV Protection Circuit 30 25 LED Battery Tester.............................. -

621 212 Electronics and Communication Engineering Ec6304/Linear Integrated Circuits

DSEC/ECE/EC6304-LIC/QB 1 DHANALAKSHMI SRINIVASAN ENGINEERING COLLEGE -621 212 ELECTRONICS AND COMMUNICATION ENGINEERING EC6304/LINEAR INTEGRATED CIRCUITS QUESTION BANK UNIT 1(2 MARKS) 1. What is an integrated circuit? APRIL/MAY 2010 An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and Passive components fabricated together on a single crystal of silicon. The active components are Transistors and diodes and passive components are resistors and capacitors. 2. What is current mirror? APRIL/MAY 2010 A constant current source (current mirror) makes use of the fact that for a transistor in the active mode of operation, the collector current is relatively independent of the collector voltage 3. What are two requirements to be met for a good current source? MAY/JUNE 2012 a. Superior insensitivity of circuit performance to power supply variations and temperature. b. More economical than resistors in terms of die area required providing bias currents of small value. c. When used as load element, the high incremental resistance of current source results in high voltage gains at low supply voltages. 4. What are all the important characteristics of ideal op-amp? APRIL/MAY 2015 Ideal characteristics of OPAMP 1. Open loop gain infinite 2. Input impedance infinite 3. Output impedance low 4. Bandwidth infinite 5. Zero offset, ie, Vo=0 when V1=V2=0 5. Define CMRR of OP-AMP APRIL/MAY 2011 The relative sensitivity of an op-amp to a difference signal as compared to a common - mode signal is called the common -mode rejection ratio. It is expressed in decibels. -

Hardware Abstract the Logic Gates References Results Transistors Through the Years Acknowledgements

The Practical Applications of Logic Gates in Computer Science Courses Presenters: Arash Mahmoudian, Ashley Moser Sponsored by Prof. Heda Samimi ABSTRACT THE LOGIC GATES Logic gates are binary operators used to simulate electronic gates for design of circuits virtually before building them with-real components. These gates are used as an instrumental foundation for digital computers; They help the user control a computer or similar device by controlling the decision making for the hardware. A gate takes in OR GATE AND GATE NOT GATE an input, then it produces an algorithm as to how The OR gate is a logic gate with at least two An AND gate is a consists of at least two A NOT gate, also known as an inverter, has to handle the output. This process prevents the inputs and only one output that performs what inputs and one output that performs what is just a single input with rather simple behavior. user from having to include a microprocessor for is known as logical disjunction, meaning that known as logical conjunction, meaning that A NOT gate performs what is known as logical negation, which means that if its input is true, decision this making. Six of the logic gates used the output of this gate is true when any of its the output of this gate is false if one or more of inputs are true. If all the inputs are false, the an AND gate's inputs are false. Otherwise, if then the output will be false. Likewise, are: the OR gate, AND gate, NOT gate, XOR gate, output of the gate will also be false. -

Solving Logic Problems with a Twist

Transformations Volume 6 Issue 1 Winter 2020 Article 6 11-30-2020 Solving Logic Problems with a Twist Angie Su Nova Southeastern University, [email protected] Bhagi Phuel Chloe Johnson Dylan Mandolini Shawlyn Fleming Follow this and additional works at: https://nsuworks.nova.edu/transformations Part of the Science and Mathematics Education Commons, and the Teacher Education and Professional Development Commons Recommended Citation Su, Angie; Bhagi Phuel; Chloe Johnson; Dylan Mandolini; and Shawlyn Fleming (2020) "Solving Logic Problems with a Twist," Transformations: Vol. 6 : Iss. 1 , Article 6. Available at: https://nsuworks.nova.edu/transformations/vol6/iss1/6 This Article is brought to you for free and open access by the Abraham S. Fischler College of Education at NSUWorks. It has been accepted for inclusion in Transformations by an authorized editor of NSUWorks. For more information, please contact [email protected]. Solving Logic Problems with a Twist Cover Page Footnote This article was originally published in the Dimensions Journal, A publication of the Florida Council of Teachers of Mathematics Journal. This article is available in Transformations: https://nsuworks.nova.edu/transformations/vol6/iss1/6 Su, Hui Fang Huang, Bhagi Phuel, Chloe Johnson, Dylan Mandolini, and Shawlyn Fleming Solving Logic Problems with a Twist Solving Logic Problems with a Twist Hui Fang Huang Su, Bhagi Phuel, Chloe Johnson, Dylan Mandolini, and Shawlyn Fleming Review of Symbolic Logic Aristotle, Greek philosopher and scientist, was a pupil of Plato and asserted that any logical argument is reducible to two premises and a conclusion (Gullberg, 1997). According to classical (Aristotelian) logic, arguments are governed by three fundamental laws: the principle of identity, the principle of the excluded middle, and the principle of contradiction. -

1. Draw the Circuit Diagram of Basic CMOS Gate and Explain the Operation

1. Draw the circuit diagram of basic CMOS gate and explain the operation. The basic CMOS inverter circuit is shown in below figure. It consists of two MOS transistors connected in series (1-PMOS and 1-NMOS). The P-channel device source is connected to +VDD and the N-channel device source is connected to ground. The gates of the two devices are connected together as the common input VIN and the drains are connected together as the common output VOUT. Case 1: When Input is LOW If input VIN is low then the n-channel transistor Q1 is off, and it acts as a open switch since its Vgs is 0, but the top, p-channel transistor Q2 is on, and acts as a closed switch since its Vgs is a large negative value. This produces ouput voltage approximately +VDD as shown in fig 6(a). VOUT=VDD Case 2: When Input is HIGH If input VIN is high then the n-channel transistor Q1 is on, and it acts as a closed switch , but the top, p-channel transistor Q2 is off, and acts as a open switch. This produces ouput voltage approximately 0V as shown in fig 6(b). FUNCTION TABLE: VOUT=0V INPU Q1 Q2 OUTP T UT (VIN) (VOUT) 0 ON OFF 1 1 OFF ON 0 LOGIC SYMBOL: 2. Draw the resistive model of a CMOS inverter circuit and explain its behavior for LOW and HIGH outputs. CIRCUIT BEHAVIOR WITH RESISTIVE LOADS: CMOS gate inputs have very high impedance and consume very little current from the circuits that drive them. -

Circuit Diagram

CIRCUIT DIAGRAM Common schematic diagram symbols (US symbols) A circuit diagram (also known as an electrical diagram, elementary diagram, or electronic schematic) is a simplified conventional graphical representation of an electrical circuit. A pictorial circuit diagram uses simple images of components, while a schematic diagram shows the components of the circuit as simplified standard symbols; both types show the connections between the devices, including power and signal connections. Arrangement of the components interconnections on the diagram does not correspond to their physical locations in the finished device. Unlike a block diagram or layout diagram, a circuit diagram shows the actual wire connections being used. The diagram does not show the physical arrangement of components. A drawing meant to depict what the physical arrangement of the wires and the components they connect is called "artwork" or "layout" or the "physical design." Circuit diagrams are used for the design (circuit design), construction (such as PCB layout), and maintenance of electrical and electronic equipment. Symbols Circuit diagram symbols have differed from country to country and have changed over time, but are now to a large extent internationally standardized. Simple components often had symbols intended to represent some feature of the physical construction of the device. For example, the symbol for a resistor shown here dates back to the days when that component was made from a long piece of wire wrapped in such a manner as to not produce inductance, which would have made it a coil. These wirewound resistors are now used only in high-power applications, smaller resistors being cast from carbon composition (a mixture of carbon and filler) or fabricated as an insulating tube or chip coated with a metal film. -

Designing Combinational Logic Gates in Cmos

CHAPTER 6 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS In-depth discussion of logic families in CMOS—static and dynamic, pass-transistor, nonra- tioed and ratioed logic n Optimizing a logic gate for area, speed, energy, or robustness n Low-power and high-performance circuit-design techniques 6.1 Introduction 6.3.2 Speed and Power Dissipation of Dynamic Logic 6.2 Static CMOS Design 6.3.3 Issues in Dynamic Design 6.2.1 Complementary CMOS 6.3.4 Cascading Dynamic Gates 6.5 Leakage in Low Voltage Systems 6.2.2 Ratioed Logic 6.4 Perspective: How to Choose a Logic Style 6.2.3 Pass-Transistor Logic 6.6 Summary 6.3 Dynamic CMOS Design 6.7 To Probe Further 6.3.1 Dynamic Logic: Basic Principles 6.8 Exercises and Design Problems 197 198 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS Chapter 6 6.1Introduction The design considerations for a simple inverter circuit were presented in the previous chapter. In this chapter, the design of the inverter will be extended to address the synthesis of arbitrary digital gates such as NOR, NAND and XOR. The focus will be on combina- tional logic (or non-regenerative) circuits that have the property that at any point in time, the output of the circuit is related to its current input signals by some Boolean expression (assuming that the transients through the logic gates have settled). No intentional connec- tion between outputs and inputs is present. In another class of circuits, known as sequential or regenerative circuits —to be dis- cussed in a later chapter—, the output is not only a function of the current input data, but also of previous values of the input signals (Figure 6.1). -

LTSPICE SOFTWARE Beginner's Guide

L2EEA Electronique 2ème semestre v2017 LTSPICE SOFTWARE Beginner’s guide Preliminary calculations must be done before the practical session Aims: • Perform a harmonic study with LTSPICE software • Know how to plot a Bode plot with LTSPICE The time for this initiation must not exceed 45 minutes. LTSPICE is a freeware generally used for the modelling or analog electronic circuits. It is distributed by LinearTechnology © and can be freely downloaded for windows OS (link: http://www.linear.com/designtools/software). Two kinds of studies can be done with LTSPICE. Two kinds of studies can be performed for an electronic circuit by using LTSPICE: - Harmonic study , in the frequency space - Transient analysis, in the time space The software can also be used for parametric study by varying the numerical value of a component of the circuit (resistance, DC supply, capacitor etc..). For all the cases the modelling of an electronic circuit should be done following these three steps: 1st step: Circuit diagram realization 2nd step: definition of simulation parameters (harmonic or transient study) and use (or not) of a parametric study. 3rd step: Run the simulation and visualization and analysis of the results. 1. Frequency behavior of a passive RC circuit Becoming familiar with the software by studying the frequency behavior of an RC circuit. The very first step is to create a new project with the software and to save it. For this, you have to click on the LTSPICE icon (on the desktop). Then, click on “File Menu” and on “New schematic”. Save your project in a folder named “your name” on the desktop by using the “save as” command. -

Designing Digital Circuits a Modern Approach

Designing Digital Circuits a modern approach Jonathan Turner 2 Contents I First Half 5 1 Introduction to Designing Digital Circuits 7 1.1 Getting Started . .7 1.2 Gates and Flip Flops . .9 1.3 How are Digital Circuits Designed? . 10 1.4 Programmable Processors . 12 1.5 Prototyping Digital Circuits . 15 2 First Steps 17 2.1 A Simple Binary Calculator . 17 2.2 Representing Numbers in Digital Circuits . 21 2.3 Logic Equations and Circuits . 24 3 Designing Combinational Circuits With VHDL 33 3.1 The entity and architecture . 34 3.2 Signal Assignments . 39 3.3 Processes and if-then-else . 43 4 Computer-Aided Design 51 4.1 Overview of CAD Design Flow . 51 4.2 Starting a New Project . 54 4.3 Simulating a Circuit Module . 61 4.4 Preparing to Test on a Prototype Board . 66 4.5 Simulating the Prototype Circuit . 69 3 4 CONTENTS 4.6 Testing the Prototype Circuit . 70 5 More VHDL Language Features 77 5.1 Symbolic constants . 78 5.2 For and case statements . 81 5.3 Synchronous and Asynchronous Assignments . 86 5.4 Structural VHDL . 89 6 Building Blocks of Digital Circuits 93 6.1 Logic Gates as Electronic Components . 93 6.2 Storage Elements . 98 6.3 Larger Building Blocks . 100 6.4 Lookup Tables and FPGAs . 105 7 Sequential Circuits 109 7.1 A Fair Arbiter Circuit . 110 7.2 Garage Door Opener . 118 8 State Machines with Data 127 8.1 Pulse Counter . 127 8.2 Debouncer . 134 8.3 Knob Interface . 137 8.4 Two Speed Garage Door Opener . -

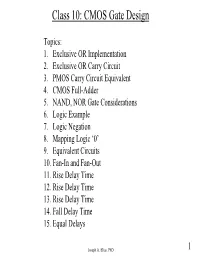

Class 10: CMOS Gate Design

Class 10: CMOS Gate Design Topics: 1. Exclusive OR Implementation 2. Exclusive OR Carry Circuit 3. PMOS Carry Circuit Equivalent 4. CMOS Full-Adder 5. NAND, NOR Gate Considerations 6. Logic Example 7. Logic Negation 8. Mapping Logic ‘0’ 9. Equivalent Circuits 10. Fan-In and Fan-Out 11. Rise Delay Time 12. Rise Delay Time 13. Rise Delay Time 14. Fall Delay Time 15. Equal Delays Joseph A. Elias, PhD 1 Class 10: CMOS Gate Design Exclusive OR Design (Martin c4.5) 3-input XOR Truth Table Similar to how one derives a 2-input XOR (Martin, p.183) using (a’+b’)=(ab)’ (a’b’)=(a+b)’ a XOR b = a’b + ab’ = a’a + a’b + ab’ + bb’ = a’(a+b) + b’(a+b) = (a’+b’)(a+b) = (ab)’(a+b) = (ab + (a’b’) )’ = (ab + (a + b)’ )’ Joseph A. Elias, PhD 2 Class 10: CMOS Gate Design Exclusive OR Carry Circuit (Martin c4.5) NMOS realization PMOS equivalent •A in parallel with B •A in series with B •A||B in series with C •AB in parallel with C •AB in parallel with (A||B)C •A||B in series with (AB)||C Vout = Joseph A. Elias, PhD 3 Class 10: CMOS Gate Design PMOS Carry Circuit Equivalent (Martin c4.5) •Martin indicates equivalency between these circuits •Is this true? (AB+C)(A+B) = (A+B)C + (AB) ABA + ABB + AC + BC = AC +BC +AB AB + AB + AC + BC = AC + BC + AB AB + AC + BC = AB + AC + BC equivalent Joseph A. Elias, PhD 4 Class 10: CMOS Gate Design CMOS Full-Adder (Martin c4.5) Sum: (A+B+C) Carry + ABC Carry: (A+B)C + AB Joseph A.