Combinational Logic Circuits

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 3: Combinational Logic Design

Chapter 3: Combinational Logic Design 1 Introduction • We have learned all the prerequisite material: – Truth tables and Boolean expressions describe functions – Expressions can be converted into hardware circuits – Boolean algebra and K-maps help simplify expressions and circuits • Now, let us put all of these foundations to good use, to analyze and design some larger circuits 2 Introduction • Logic circuits for digital systems may be – Combinational – Sequential • A combinational circuit consists of logic gates whose outputs at any time are determined by the current input values, i.e., it has no memory elements • A sequential circuit consists of logic gates whose outputs at any time are determined by the current input values as well as the past input values, i.e., it has memory elements 3 Introduction • Each input and output variable is a binary variable • 2^n possible binary input combinations • One possible binary value at the output for each input combination • A truth table or m Boolean functions can be used to specify input-output relation 4 Design Hierarchy • A single very large-scale integrated (VLSI) processos circuit contains several tens of millions of gates! • Imagine interconnecting these gates to form the processor • No complex circuit can be designed simply by interconnecting gates one at a time • Divide and Conquer approach is used to deal with the complexity – Break up the circuit into pieces (blocks) – Define the functions and the interfaces of each block such that the circuit formed by interconnecting the blocks obeys the original circuit specification – If a block is still too large and complex to be designed as a single entity, it can be broken into smaller blocks 5 Divide and Conquer 6 Hierarchical Design due to Divide and Conquer 7 Hierarchical Design • A hierarchy reduce the complexity required to represent the schematic diagram of a circuit • In any hierarchy, the leaves consist of predefined blocks, some of which may be primitives. -

Logisim Operon Circuits

International Journal of Scientific & Engineering Research, Volume 4, Issue 8, August-2013 1312 ISSN 2229-5518 Logisim Operon Circuits Aman Chandra Kaushik Aman Chandra Kaushik (M.Sc. Bioinformatics) Department of Bioinformatics, University Institute of Engineering & Technology Chhatrapati Shahu Ji Maharaj University, Kanpur-208024, Uttar Pradesh, India Email: [email protected] Phone: +91-8924003818 Abstract: Creation of Logism Operon circuits for bacterial cells that not only perform logic functions, but also remember the results, which are encoded in the cell’s DNA and passed on for dozens of generations. This circuits is coded in JAVA Language. “Almost all of the previous work in synthetic biology that we’re aware of has either focused on logic components and logical circuits or on memory modules that just encode memory. We think complex computation will involve combining both logic and memory, and that’s why we built this particular framework for designing circuits Life Science. In one circuit described in the paper, one DNA sequences have three genes called Repressor, Operator (terminators) are interposed between the promoter (DNA Polymerase) and the output Proteins (Beta glactosidase, permease, Transacetylase in this case). Each of these terminators inhibits the transcription and Translation of the output gene and can be flipped by a different Promoter enzyme (DNA Polymerase), making the terminator inactive. Key words: Logical IJSERGate, JAVA, Circuits, Operon, AND, OR, NOT, NOR, NAND, XOR, XNOR, Operon Logisim Circuits. IJSER © 2013 http://www.ijser.org International Journal of Scientific & Engineering Research, Volume 4, Issue 8, August-2013 1313 ISSN 2229-5518 1. Introduction The AND gate is obtained from the E6 core module by extending both ends with hairpin M olecular Logic Gates Coding in Java modules, one complementary to input Language and circuits are designed in oligonucleotide x and the other Logisim complementary to input oligonucleotide y. -

Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free Systems

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Doctoral Dissertations Graduate School 12-2012 Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems Sukanya Iyer University of Tennessee, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_graddiss Part of the Biotechnology Commons Recommended Citation Iyer, Sukanya, "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems. " PhD diss., University of Tennessee, 2012. https://trace.tennessee.edu/utk_graddiss/1586 This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a dissertation written by Sukanya Iyer entitled "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Doctor of Philosophy, with a major in Life Sciences. Mitchel J. Doktycz, Major Professor We have read this dissertation and recommend its acceptance: Michael L. Simpson, Albrecht G. von Arnim, Barry D. Bruce, Jennifer L. Morrell-Falvey Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville Sukanya Iyer December 2012 Copyright © 2012 by Sukanya Iyer. -

CSE Yet, Please Do Well! Logical Connectives

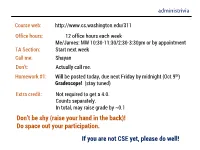

administrivia Course web: http://www.cs.washington.edu/311 Office hours: 12 office hours each week Me/James: MW 10:30-11:30/2:30-3:30pm or by appointment TA Section: Start next week Call me: Shayan Don’t: Actually call me. Homework #1: Will be posted today, due next Friday by midnight (Oct 9th) Gradescope! (stay tuned) Extra credit: Not required to get a 4.0. Counts separately. In total, may raise grade by ~0.1 Don’t be shy (raise your hand in the back)! Do space out your participation. If you are not CSE yet, please do well! logical connectives p q p q p p T T T T F T F F F T F T F NOT F F F AND p q p q p q p q T T T T T F T F T T F T F T T F T T F F F F F F OR XOR 푝 → 푞 • “If p, then q” is a promise: p q p q F F T • Whenever p is true, then q is true F T T • Ask “has the promise been broken” T F F T T T If it’s raining, then I have my umbrella. related implications • Implication: p q • Converse: q p • Contrapositive: q p • Inverse: p q How do these relate to each other? How to see this? 푝 ↔ 푞 • p iff q • p is equivalent to q • p implies q and q implies p p q p q Let’s think about fruits A fruit is an apple only if it is either red or green and a fruit is not red and green. -

Automated Unbounded Verification of Stateful Cryptographic Protocols

Automated Unbounded Verification of Stateful Cryptographic Protocols with Exclusive OR Jannik Dreier Lucca Hirschi Sasaˇ Radomirovic´ Ralf Sasse Universite´ de Lorraine Department of School of Department of CNRS, Inria, LORIA Computer Science Science and Engineering Computer Science F-54000 Nancy ETH Zurich University of Dundee ETH Zurich France Switzerland UK Switzerland [email protected] [email protected] [email protected] [email protected] Abstract—Exclusive-or (XOR) operations are common in cryp- on widening the scope of automated protocol verification tographic protocols, in particular in RFID protocols and elec- by extending the class of properties that can be verified to tronic payment protocols. Although there are numerous appli- include, e.g., equivalence properties [19], [24], [27], [51], cations, due to the inherent complexity of faithful models of XOR, there is only limited tool support for the verification of [14], extending the adversary model with complex forms of cryptographic protocols using XOR. compromise [13], or extending the expressiveness of protocols, The TAMARIN prover is a state-of-the-art verification tool e.g., by allowing different sessions to update a global, mutable for cryptographic protocols in the symbolic model. In this state [6], [43]. paper, we improve the underlying theory and the tool to deal with an equational theory modeling XOR operations. The XOR Perhaps most significant is the support for user-specified theory can be freely combined with all equational theories equational theories allowing for the modeling of particular previously supported, including user-defined equational theories. cryptographic primitives [21], [37], [48], [24], [35]. -

Combinational Logic; Hierarchical Design and Analysis

Combinational Logic; Hierarchical Design and Analysis Tom Kelliher, CS 240 Feb. 10, 2012 1 Administrivia Announcements Collect assignment. Assignment Read 3.3. From Last Time IC technology. Outline 1. Combinational logic. 2. Hierarchical design 3. Design analysis. 1 Coming Up Design example. 2 Combinational Logic 1. Definition: Logic circuits in which the output(s) depend solely upon current inputs. 2. No feedback or memory. 3. Sequential circuits: outputs depend upon current inputs and previous inputs. Memory or registers. 4. Example — BCD to 7-segment decoder: S0 D0 S1 D1 BCD - 7 Seg S2 D2 S3 D3 Decoder S4 S5 S6 3 Hierarchical Design 1. Transistor counts: 2 Processor Year Transistor Count TI SN7400 1966 16 Intel 4004 1971 2,300 Intel 8085 1976 6,500 Intel 8088 1979 29,000 Intel 80386 1985 275,000 Intel Pentium 1993 3,100,000 Intel Pentium 4 2000 42,000,000 AMD Athlon 64 2003 105,900,000 Intel Core 2 Duo 2006 291,000,000 Intel Core 2 Quad 2006 582,000,000 NVIDIA G80 2006 681,000,000 Intel Dual Core Itanium 2 2006 1,700,000,000 Intel Atom 2008 42,000,000 Six Core Xeon 7400 2008 1,900,000,000 AMD RV770 2008 956,000,000 NVIDIA GT200 2008 1,400,000,000 Eight Core Xeon Nehalem-EX 2010 2,300,000,000 10 Core Xeon Westmere-EX 2011 2,600,000,000 AMD Cayman 2010 2,640,000,000 NVIDIA GF100 2010 3,000,000,000 Altera Stratix V 2011 3,800,000,000 2. Design and conquer: CPU ⇒ Integer Unit ⇒ Adder ⇒ binary full adder ⇒ NAND gates 3. -

Realization of Morphing Logic Gates in a Repressilator with Quorum Sensing Feedback

Realization of Morphing Logic Gates in a Repressilator with Quorum Sensing Feedback Vidit Agarwal, Shivpal Singh Kang and Sudeshna Sinha Indian Institute of Science Education and Research (IISER) Mohali, Knowledge City, SAS Nagar, Sector 81, Manauli PO 140 306, Punjab, India Abstract We demonstrate how a genetic ring oscillator network with quorum sensing feedback can operate as a robust logic gate. Specifically we show how a range of logic functions, namely AND/NAND, OR/NOR and XOR/XNOR, can be realized by the system, thus yielding a versatile unit that can morph between different logic operations. We further demonstrate the capacity of this system to yield complementary logic operations in parallel. Our results then indicate the computing potential of this biological system, and may lead to bio-inspired computing devices. arXiv:1310.8267v1 [physics.bio-ph] 30 Oct 2013 1 I. INTRODUCTION The operation of any computing device is necessarily a physical process, and this funda- mentally determines the possibilities and limitations of the computing machine. A common thread in the history of computers is the exploitation and manipulation of different natural phenomena to obtain newer forms of computing paradigms [1]. For instance, chaos comput- ing [2], neurobiologically inspired computing, quantum computing[3], and DNA computing[4] all aim to utilize, at the basic level, some of the computational capabilities inherent in natural systems. In particular, larger understanding of biological systems has triggered the interest- ing question: what new directions do bio-systems offer for understanding and implementing computations? The broad idea then, is to create machines that benefit from natural phenomena and utilize patterns inherent in systems to encode inputs and subsequently obtain a desired output. -

A Combinatorial Analysis of Finite Boolean Algebras

A Combinatorial Analysis of Finite Boolean Algebras Kevin Halasz [email protected] May 1, 2013 Copyright c Kevin Halasz. Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.3 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license can be found at http://www.gnu.org/copyleft/fdl.html. 1 Contents 1 Introduction 3 2 Basic Concepts 3 2.1 Chains . .3 2.2 Antichains . .6 3 Dilworth's Chain Decomposition Theorem 6 4 Boolean Algebras 8 5 Sperner's Theorem 9 5.1 The Sperner Property . .9 5.2 Sperner's Theorem . 10 6 Extensions 12 6.1 Maximally Sized Antichains . 12 6.2 The Erdos-Ko-Rado Theorem . 13 7 Conclusion 14 2 1 Introduction Boolean algebras serve an important purpose in the study of algebraic systems, providing algebraic structure to the notions of order, inequality, and inclusion. The algebraist is always trying to understand some structured set using symbol manipulation. Boolean algebras are then used to study the relationships that hold between such algebraic structures while still using basic techniques of symbol manipulation. In this paper we will take a step back from the standard algebraic practices, and analyze these fascinating algebraic structures from a different point of view. Using combinatorial tools, we will provide an in-depth analysis of the structure of finite Boolean algebras. We will start by introducing several ways of analyzing poset substructure from a com- binatorial point of view. -

A Boolean Algebra and K-Map Approach

Proceedings of the International Conference on Industrial Engineering and Operations Management Washington DC, USA, September 27-29, 2018 Reliability Assessment of Bufferless Production System: A Boolean Algebra and K-Map Approach Firas Sallumi ([email protected]) and Walid Abdul-Kader ([email protected]) Industrial and Manufacturing Systems Engineering University of Windsor, Windsor (ON) Canada Abstract In this paper, system reliability is determined based on a K-map (Karnaugh map) and the Boolean algebra theory. The proposed methodology incorporates the K-map technique for system level reliability, and Boolean analysis for interactions. It considers not only the configuration of the production line, but also effectively incorporates the interactions between the machines composing the line. Through the K-map, a binary argument is used for considering the interactions between the machines and a probability expression is found to assess the reliability of a bufferless production system. The paper covers three main system design configurations: series, parallel and hybrid (mix of series and parallel). In the parallel production system section, three strategies or methods are presented to find the system reliability. These are the Split, the Overlap, and the Zeros methods. A real-world case study from the automotive industry is presented to demonstrate the applicability of the approach used in this research work. Keywords: Series, Series-Parallel, Hybrid, Bufferless, Production Line, Reliability, K-Map, Boolean algebra 1. Introduction Presently, the global economy is forcing companies to have their production systems maintain low inventory and provide short delivery times. Therefore, production systems are required to be reliable and productive to make products at rates which are changing with the demand. -

CS 50010 Module 1

CS 50010 Module 1 Ben Harsha Apr 12, 2017 Course details ● Course is split into 2 modules ○ Module 1 (this one): Covers basic data structures and algorithms, along with math review. ○ Module 2: Probability, Statistics, Crypto ● Goal for module 1: Review basics needed for CS and specifically Information Security ○ Review topics you may not have seen in awhile ○ Cover relevant topics you may not have seen before IMPORTANT This course cannot be used on a plan of study except for the IS Professional Masters program Administrative details ● Office: HAAS G60 ● Office Hours: 1:00-2:00pm in my office ○ Can also email for an appointment, I’ll be in there often ● Course website ○ cs.purdue.edu/homes/bharsha/cs50010.html ○ Contains syllabus, homeworks, and projects Grading ● Module 1 and module are each 50% of the grade for CS 50010 ● Module 1 ○ 55% final ○ 20% projects ○ 20% assignments ○ 5% participation Boolean Logic ● Variables/Symbols: Can only be used to represent 1 or 0 ● Operations: ○ Negation ○ Conjunction (AND) ○ Disjunction (OR) ○ Exclusive or (XOR) ○ Implication ○ Double Implication ● Truth Tables: Can be defined for all of these functions Operations ● Negation (¬p, p, pC, not p) - inverts the symbol. 1 becomes 0, 0 becomes 1 ● Conjunction (p ∧ q, p && q, p and q) - true when both p and q are true. False otherwise ● Disjunction (p v q, p || q, p or q) - True if at least one of p or q is true ● Exclusive Or (p xor q, p ⊻ q, p ⊕ q) - True if exactly one of p or q is true ● Implication (p → q) - True if p is false or q is true (q v ¬p) ● -

Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic

Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic Universal Gate – NOR This presentation will demonstrate… • The basic function of the NOR gate. • How an NOR gate can be using to replace an AND gate, an OR gate or an INVERTER gate. • How a logic circuit implemented with AOI logic gates Universal Gate – NOR could be re-implemented using only NOR gates • That using a single gate type, in this case NOR, will reduce the number of integrated circuits (IC) required to implement a logic circuit. Digital Electronics AOI Logic NOR Logic 2 More ICs = More $$ Less ICs = Less $$ NOR Gate NOR Gate as an Inverter Gate X X X (Before Bubble) X Z X Y X Y X Z X Y X Y Z X Z 0 0 1 0 1 Equivalent to Inverter 0 1 0 1 0 1 0 0 1 1 0 3 4 Project Lead The Way, Inc. Copyright 2009 1 Universal Gate - NOR Digital Electronics 2.2 Intro to NAND & NOR Logic NOR Gate as an OR Gate NOR Gate as an AND Gate X X Y Y X X Z X Y X Y Y Z X Y X Y X Y Y NOR Gate “Inverter” “Inverters” NOR Gate X Y Z X Y Z 0 0 0 0 0 0 0 1 1 0 1 0 Equivalent to OR Gate Equivalent to AND Gate 1 0 1 1 0 0 1 1 1 1 1 1 5 6 NOR Gate Equivalent of AOI Gates Process for NOR Implementation 1. -

Boolean Algebra

Boolean Algebra Definition: A Boolean Algebra is a math construct (B,+, . , ‘, 0,1) where B is a non-empty set, + and . are binary operations in B, ‘ is a unary operation in B, 0 and 1 are special elements of B, such that: a) + and . are communative: for all x and y in B, x+y=y+x, and x.y=y.x b) + and . are associative: for all x, y and z in B, x+(y+z)=(x+y)+z, and x.(y.z)=(x.y).z c) + and . are distributive over one another: x.(y+z)=xy+xz, and x+(y.z)=(x+y).(x+z) d) Identity laws: 1.x=x.1=x and 0+x=x+0=x for all x in B e) Complementation laws: x+x’=1 and x.x’=0 for all x in B Examples: • (B=set of all propositions, or, and, not, T, F) • (B=2A, U, ∩, c, Φ,A) Theorem 1: Let (B,+, . , ‘, 0,1) be a Boolean Algebra. Then the following hold: a) x+x=x and x.x=x for all x in B b) x+1=1 and 0.x=0 for all x in B c) x+(xy)=x and x.(x+y)=x for all x and y in B Proof: a) x = x+0 Identity laws = x+xx’ Complementation laws = (x+x).(x+x’) because + is distributive over . = (x+x).1 Complementation laws = x+x Identity laws x = x.1 Identity laws = x.(x+x’) Complementation laws = x.x +x.x’ because + is distributive over .