Logic Families

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Allgemeines Abkürzungsverzeichnis

Allgemeines Abkürzungsverzeichnis L. -

Transistors and Logic Gates

Introduction to Computer Engineering CS/ECE 252, Spring 2013 Prof. Mark D. Hill Computer Sciences Department University of Wisconsin – Madison Chapter 3 Digital Logic Structures Slides based on set prepared by Gregory T. Byrd, North Carolina State University Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. Transistor: Building Block of Computers Microprocessors contain millions of transistors • Intel Pentium II: 7 million • Compaq Alpha 21264: 15 million • Intel Pentium III: 28 million Logically, each transistor acts as a switch Combined to implement logic functions • AND, OR, NOT Combined to build higher-level structures • Adder, multiplexer, decoder, register, … Combined to build processor • LC-3 3-3 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. Simple Switch Circuit Switch open: • No current through circuit • Light is off • Vout is +2.9V Switch closed: • Short circuit across switch • Current flows • Light is on • Vout is 0V Switch-based circuits can easily represent two states: on/off, open/closed, voltage/no voltage. 3-4 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. N-type MOS Transistor MOS = Metal Oxide Semiconductor • two types: N-type and P-type N-type • when Gate has positive voltage, short circuit between #1 and #2 (switch closed) • when Gate has zero voltage, open circuit between #1 and #2 Gate = 1 (switch open) Gate = 0 Terminal #2 must be connected to GND (0V). 3-5 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. P-type MOS Transistor P-type is complementary to N-type • when Gate has positive voltage, open circuit between #1 and #2 (switch open) • when Gate has zero voltage, short circuit between #1 and #2 (switch closed) Gate = 1 Gate = 0 Terminal #1 must be connected to +2.9V. -

System Design for a Computational-RAM Logic-In-Memory Parailel-Processing Machine

System Design for a Computational-RAM Logic-In-Memory ParaIlel-Processing Machine Peter M. Nyasulu, B .Sc., M.Eng. A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy Ottaw a-Carleton Ins titute for Eleceical and Computer Engineering, Department of Electronics, Faculty of Engineering, Carleton University, Ottawa, Ontario, Canada May, 1999 O Peter M. Nyasulu, 1999 National Library Biôiiothkque nationale du Canada Acquisitions and Acquisitions et Bibliographie Services services bibliographiques 39S Weiiington Street 395. nie WeUingtm OnawaON KlAW Ottawa ON K1A ON4 Canada Canada The author has granted a non- L'auteur a accordé une licence non exclusive licence allowing the exclusive permettant à la National Library of Canada to Bibliothèque nationale du Canada de reproduce, ban, distribute or seU reproduire, prêter, distribuer ou copies of this thesis in microform, vendre des copies de cette thèse sous paper or electronic formats. la forme de microficbe/nlm, de reproduction sur papier ou sur format électronique. The author retains ownership of the L'auteur conserve la propriété du copyright in this thesis. Neither the droit d'auteur qui protège cette thèse. thesis nor substantial extracts fkom it Ni la thèse ni des extraits substantiels may be printed or otherwise de celle-ci ne doivent être imprimés reproduced without the author's ou autrement reproduits sans son permission. autorisation. Abstract Integrating several 1-bit processing elements at the sense amplifiers of a standard RAM improves the performance of massively-paralle1 applications because of the inherent parallelism and high data bandwidth inside the memory chip. -

Lecture17 08 04 2010

EE40 Lecture 17 Josh Hug 8/04/2010 EE40 Summer 2010 Hug 1 Logistics • HW8 will be due Friday • Mini-midterm 3 next Wednesday – 80/160 points will be a take-home set of design problems which will utilize techniques we’ve covered in class • Handed out Friday • Due next Wednesday – Other 80/160 will be an in class midterm covering HW7 and HW8 • Final will include Friday and Monday lecture, Midterm won’t – Design problems will provide practice EE40 Summer 2010 Hug 2 Project 2 • Booster lab actually due next week – For Booster lab, ignore circuit simulation, though it may be instructive to try the Falstad simulator • Project 2 due next Wednesday – Presentation details to come [won’t be mandatory, but we will ask everyone about their circuits at some point] EE40 Summer 2010 Hug 3 Project 2 • For those of you who want to demo Project 2, we’ll be doing demos in lab on Wednesday at some point – Will schedule via online survey EE40 Summer 2010 Hug 4 CMOS/NMOS Design Correction • (Sent by email) • My on-the-fly explanation was correct, but not the most efficient way – If your FET circuit is implementing a logic function with a bar over it, i.e. • 푍 = 퐴 + 퐵퐶 + 퐷 + 퐸퐹 퐺 + 퐻 – Then don’t put an inverter at the output, it just makes things harder and less efficient • Sorry, on-the-fly-explanations can be dicey EE40 Summer 2010 Hug 5 CMOS • CMOS Summary: – No need for a pull-up or pull-down resistor • Though you can avoid this even with purely NMOS logic (see HW7) – Greatly reduced static power dissipation vs. -

Efficient Design of 2'S Complement Adder/Subtractor Using QCA

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 2 Issue 11, November - 2013 Efficient Design of 2'S complement Adder/Subtractor Using QCA. D.Ajitha 1 Dr.K.Venkata Ramanaiah 3 , Assistant Professor, Dept of ECE, Associate Professor, ECE Dept , S.I.T.A.M..S., Chittoor, Y S R Engineering college of Yogi Vemana A.P. India. University, Proddatur. 2 4 P.Yugesh Kumar, Dr.V.Sumalatha , SITAMS,Chittoor, Associate Professor, Dept of ECE, J.N.T.U.C.E.A Ananthapur, A.P. Abstract: The alternate digital design of In this paper efficient 1-bit full adder [10] has CMOS Technology fulfilled with the Quantum taken to implement the above circuit by comparing with previous 1-bit full adder designs [7-9]. A full adder with Dot Cellular Automata. In this paper, the 2’s reduced one inverter is used and implemented with less complement adder design with overflow was number of cells. Latency and power consumption is also implemented as first time in QCA & have the reduced with the help of optimization process [5]. smallest area with the least number of cells, Therefore efficient two‟s complement adder is also reduced latency and low cost achieved with designed using the efficient 1-bit full adder [10] and reduced all the parameters like area delay and cost one inverter reduced full adder using majority compared with CMOS [14]. logic. The circuit was simulated with QCADesigner and results were included in The paper is organized as follows: In Section 2, this paper. QCA basics and design methods to implement gates functionalities is presented. -

Understanding and Interpreting Standard-Logic Data Sheets

Application Report SZZA036B - May 2003 Understanding and Interpreting Standard-Logic Data Sheets Stephen M. Nolan and Jose M. Soltero Standard Linear & Logic ABSTRACT Texas Instruments (TI) standard-logic products data sheets include descriptions of functionality and electrical specifications for the devices. Each specification includes acronyms, numerical limits, and test conditions that may be foreign to the user. The proper understanding and interpretation of the direct, and sometimes implied, meanings of these specifications is essential to correct product selection and associated circuit design. This application report explains each data-sheet parameter in detail, how it affects the device, and, more important, how it impacts the application. This will enable component and system-design engineers to derive the maximum benefit from TI logic devices. Contents Introduction . 6 Top-Level Look at the TI Logic Data Sheet. 6 Summary Device Description. 7 Absolute Maximum Ratings. 9 Recommended Operating Conditions. 9 Electrical Characteristics. 10 Live-Insertion Specifications. 11 Timing Requirements . 12 Switching Characteristics. 12 Noise Characteristics . 13 Operating Characteristics. 14 Parameter Measurement Information. 14 Dissecting the TI Logic Data Sheet. 16 Summary Device Description. 16 Title, Literature Number, and Dates of Origination and Revision. 16 Features Bullets . 22 Package Options and Pinouts. 23 Description . 23 BGA Packaging Top-View Illustrations and Pin-Assignments Table. 23 Ordering Information. 23 Function Table . 24 Logic Diagram . 26 Product Development Stage Note. 27 Absolute Maximum Ratings. 27 Supply Voltage, VCC . 27 Trademarks are the property of their respective owners. 1 SZZA036B Input Voltage, VI . 27 Output Voltage, VO . 28 Voltage Range Applied to Any Output in the High-Impedance or Power-Off State, VO . -

Introduction to ASIC Design

’14EC770 : ASIC DESIGN’ An Introduction Application - Specific Integrated Circuit Dr.K.Kalyani AP, ECE, TCE. 1 VLSI COMPANIES IN INDIA • Motorola India – IC design center • Texas Instruments – IC design center in Bangalore • VLSI India – ASIC design and FPGA services • VLSI Software – Design of electronic design automation tools • Microchip Technology – Offers VLSI CMOS semiconductor components for embedded systems • Delsoft – Electronic design automation, digital video technology and VLSI design services • Horizon Semiconductors – ASIC, VLSI and IC design training • Bit Mapper – Design, development & training • Calorex Institute of Technology – Courses in VLSI chip design, DSP and Verilog HDL • ControlNet India – VLSI design, network monitoring products and services • E Infochips – ASIC chip design, embedded systems and software development • EDAIndia – Resource on VLSI design centres and tutorials • Cypress Semiconductor – US semiconductor major Cypress has set up a VLSI development center in Bangalore • VDAT 2000 – Info on VLSI design and test workshops 2 VLSI COMPANIES IN INDIA • Sandeepani – VLSI design training courses • Sanyo LSI Technology – Semiconductor design centre of Sanyo Electronics • Semiconductor Complex – Manufacturer of microelectronics equipment like VLSIs & VLSI based systems & sub systems • Sequence Design – Provider of electronic design automation tools • Trident Techlabs – Power systems analysis software and electrical machine design services • VEDA IIT – Offers courses & training in VLSI design & development • Zensonet Technologies – VLSI IC design firm eg3.com – Useful links for the design engineer • Analog Devices India Product Development Center – Designs DSPs in Bangalore • CG-CoreEl Programmable Solutions – Design services in telecommunications, networking and DSP 3 Physical Design, CAD Tools. • SiCore Systems Pvt. Ltd. 161, Greams Road, ... • Silicon Automation Systems (India) Pvt. Ltd. ( SASI) ... • Tata Elxsi Ltd. -

Negation-Limited Complexity of Parity and Inverters

数理解析研究所講究録 第 1554 巻 2007 年 131-138 131 Negation-Limited Complexity of Parity and Inverters 森住大樹 1 垂井淳 2 岩間一雄 1 1 京都大学大学院情報学研究科, {morizumi, iwama}@kuis.kyoto-u.ac.jp 2 電気通信大学情報通信工学科, [email protected] Abstract 1 Introduction and Summary In negation-limited complexity, one considers circuits Although exponential lower bounds are known for the with a limited number of NOT gates, being mo- monotone circuit size [4], [6], at present we cannot tivated by the gap in our understanding of mono- prove a superlinear lower bound for the size of circuits tone versus general circuit complexity, and hop- computing an explicit Boolean function: the largest ing to better understand the power of NOT gates. known lower bound is $5n-o(n)[\eta, |10],$ $[8]$ . It is We give improved lower bounds for the size (the natural to ask: What happens if we allow a limited number of $AND/OR/NOT$) of negation-limited cir- number of NOT gatae? The hope is that by the study cuits computing Parity and for the size of negation- of negation-limited complexity of Boolean functions limited inverters. An inverter is a circuit with inputs under various scenarios [3], [17], [15]. [2], $|1$ ], $[13]$ , we $x_{1},$ $\ldots,x_{\mathfrak{n}}$ $\neg x_{1},$ $po\mathfrak{n}^{r}er$ and outputs $\ldots,$ $\neg x_{n}$ . We show that understand the of NOT gates better. (a) For $n=2^{f}-1$ , circuits computing Parity with $r-1$ We consider circuits consisting of $AND/OR/NOT$ NOT gates have size at least $6n-\log_{2}(n+1)-O(1)$, gates. -

A Vertical Resonant Tunneling Transistor for Application in Digital Logic Circuits

1028 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 48, NO. 6, JUNE 2001 A Vertical Resonant Tunneling Transistor for Application in Digital Logic Circuits Jürgen Stock, Jörg Malindretos, Klaus Michael Indlekofer, Michael Pöttgens, Arno Förster, and Hans Lüth Abstract—A vertical resonant tunneling transistor (VRTT) has In this paper, we report on the fabrication of a vertical res- been developed, its properties and its application in digital logic onant tunneling transistor (VRTT) with low peak voltage and circuits based on the monostable-bistable transition logic element good peak current control by means of a Schottky gate. The (MOBILE) principle are described. The device consists of a small mesa resonant tunneling diode (RTD) in the GaAs/AlAs material asymmetric behavior of the current-voltage ( ) character- system surrounded by a Schottky gate. We obtain low peak voltages istics is analyzed and the transistors are characterized with re- using InGaAs in the quantum well and the devices show an excel- spect to their peak voltage, peak-to-valley ratio (PVR), peak cur- lent peak current control by means of an applied gate voltage. A rent density, and gate function. We demonstrate the switching self latching inverter circuit has been fabricated using two VRTTs functionality of a self latching inverter circuit consisting of two and the switching functionality was demonstrated at low frequen- cies. VRTTs. Index Terms—Monostable-bistable transition logic element (MOBILE), monostable-to-bistable transition, resonant tunneling II. DEVICE FABRICATION diode (RTD), resonant tunneling transistor. A. Layer Structure The epitaxial structure used to fabricate the VRTT device was I. INTRODUCTION grown by molecular beam epitaxy (MBE) on semi-insulating N recent years, several new memory and logic circuits based (100)-orientated GaAs substrate. -

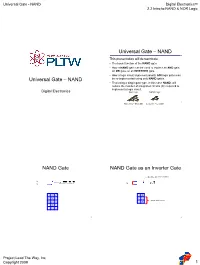

Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic

Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic Universal Gate – NAND This presentation will demonstrate • The basic function of the NAND gate. • How a NAND gate can be used to replace an AND gate, an OR gate, or an INVERTER gate. • How a logic circuit implemented with AOI logic gates can Universal Gate – NAND be re-implemented using only NAND gates. • That using a single gate type, in this case NAND, will reduce the number of integrated circuits (IC) required to implement a logic circuit. Digital Electronics AOI Logic NAND Logic 2 More ICs = More $$ Less ICs = Less $$ NAND Gate NAND Gate as an Inverter Gate X X X (Before Bubble) X Z X Y X Y X Z X Y X Y Z X Z 0 0 1 0 1 Equivalent to Inverter 0 1 1 1 0 1 0 1 1 1 0 3 4 Project Lead The Way, Inc Copyright 2009 1 Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic NAND Gate as an AND Gate NAND Gate as an OR Gate X X Y Y X X Z X Y X Y Y Z X Y X Y X Y Y NAND Gate Inverter Inverters NAND Gate X Y Z X Y Z 0 0 0 0 0 0 0 1 0 0 1 1 Equivalent to AND Gate Equivalent to OR Gate 1 0 0 1 0 1 1 1 1 1 1 1 5 6 NAND Gate Equivalent to AOI Gates Process for NAND Implementation 1. -

Reduced Swing Domino Techniques for Low Power and High Performance Arithmetic Circuits

Reduced Swing Domino Techniques for Low Power and High Performance Arithmetic Circuits by Shahrzad Naraghi A thesis presented to the University of Waterloo in ful¯llment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering Waterloo, Ontario, Canada 2004 °c Shahrzad Naraghi, 2004 I hereby declare that I am the sole author of this thesis. I authorize the University of Waterloo to lend this thesis to other institutions or individuals for the purpose of scholarly research. Shahrzad Naraghi I authorize the University of Waterloo to reproduce this thesis by photocopying or other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. Shahrzad Naraghi ii The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date. iii Acknowledgements First, I would like to thank my supervisor Professor Manoj Sachdev for his great guidance, support and patience. His advice and support were always greatly appreciated. I also want to thank Dr. Opal and Dr. Anis, my thesis readers. I'd like to thank Bhaskar Chatterjee for his great help on my research; Phil Regier for his great help on computer problems; and my good friends for bringing me joy and laughter during these years that I was away from my family. Most importantly, I'd like to thank my family for their supporting and encouraging com- ments, their love and faith in me. iv Abstract The increasing frequency of operation and the larger number of transistors on the chip, along with slower decrease in supply voltage have led to more power dissipation and high chip power density which cause problems in chip thermal management and heat removal process. -

EE 434 Lecture 2

EE 330 Lecture 6 • PU and PD Networks • Complex Logic Gates • Pass Transistor Logic • Improved Switch-Level Model • Propagation Delay Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation Source Gate Drain Drain Bulk Gate n-channel MOSFET Source Equivalent Circuit for n-channel MOSFET D D • Source assumed connected to (or close to) ground • VGS=0 denoted as Boolean gate voltage G=0 G = 0 G = 1 • VGS=VDD denoted as Boolean gate voltage G=1 • Boolean G is relative to ground potential S S This is the first model we have for the n-channel MOSFET ! Ideal switch-level model Review from Last Time MOS Transistor Qualitative Discussion of p-channel Operation Source Gate Drain Drain Bulk Gate Source p-channel MOSFET Equivalent Circuit for p-channel MOSFET D D • Source assumed connected to (or close to) positive G = 0 G = 1 VDD • VGS=0 denoted as Boolean gate voltage G=1 • VGS= -VDD denoted as Boolean gate voltage G=0 S S • Boolean G is relative to ground potential This is the first model we have for the p-channel MOSFET ! Review from Last Time Logic Circuits VDD Truth Table A B A B 0 1 1 0 Inverter Review from Last Time Logic Circuits VDD Truth Table A B C 0 0 1 0 1 0 A C 1 0 0 B 1 1 0 NOR Gate Review from Last Time Logic Circuits VDD Truth Table A B C A C 0 0 1 B 0 1 1 1 0 1 1 1 0 NAND Gate Logic Circuits Approach can be extended to arbitrary number of inputs n-input NOR n-input NAND gate gate VDD VDD A1 A1 A2 An A2 F A1 An F A2 A1 A2 An An A1 A 1 A2 F A2 F An An Complete Logic Family Family of n-input NOR gates forms