Negation-Limited Complexity of Parity and Inverters

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Efficient Design of 2'S Complement Adder/Subtractor Using QCA

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 2 Issue 11, November - 2013 Efficient Design of 2'S complement Adder/Subtractor Using QCA. D.Ajitha 1 Dr.K.Venkata Ramanaiah 3 , Assistant Professor, Dept of ECE, Associate Professor, ECE Dept , S.I.T.A.M..S., Chittoor, Y S R Engineering college of Yogi Vemana A.P. India. University, Proddatur. 2 4 P.Yugesh Kumar, Dr.V.Sumalatha , SITAMS,Chittoor, Associate Professor, Dept of ECE, J.N.T.U.C.E.A Ananthapur, A.P. Abstract: The alternate digital design of In this paper efficient 1-bit full adder [10] has CMOS Technology fulfilled with the Quantum taken to implement the above circuit by comparing with previous 1-bit full adder designs [7-9]. A full adder with Dot Cellular Automata. In this paper, the 2’s reduced one inverter is used and implemented with less complement adder design with overflow was number of cells. Latency and power consumption is also implemented as first time in QCA & have the reduced with the help of optimization process [5]. smallest area with the least number of cells, Therefore efficient two‟s complement adder is also reduced latency and low cost achieved with designed using the efficient 1-bit full adder [10] and reduced all the parameters like area delay and cost one inverter reduced full adder using majority compared with CMOS [14]. logic. The circuit was simulated with QCADesigner and results were included in The paper is organized as follows: In Section 2, this paper. QCA basics and design methods to implement gates functionalities is presented. -

Digital IC Listing

BELS Digital IC Report Package BELS Unit PartName Type Location ID # Price Type CMOS 74HC00, Quad 2-Input NAND Gate DIP-14 3 - A 500 0.24 74HCT00, Quad 2-Input NAND Gate DIP-14 3 - A 501 0.36 74HC02, Quad 2 Input NOR DIP-14 3 - A 417 0.24 74HC04, Hex Inverter, buffered DIP-14 3 - A 418 0.24 74HC04, Hex Inverter (buffered) DIP-14 3 - A 511 0.24 74HCT04, Hex Inverter (Open Collector) DIP-14 3 - A 512 0.36 74HC08, Quad 2 Input AND Gate DIP-14 3 - A 408 0.24 74HC10, Triple 3-Input NAND DIP-14 3 - A 419 0.31 74HC32, Quad OR DIP-14 3 - B 409 0.24 74HC32, Quad 2-Input OR Gates DIP-14 3 - B 543 0.24 74HC138, 3-line to 8-line decoder / demultiplexer DIP-16 3 - C 603 1.05 74HCT139, Dual 2-line to 4-line decoders / demultiplexers DIP-16 3 - C 605 0.86 74HC154, 4-16 line decoder/demulitplexer, 0.3 wide DIP - Small none 445 1.49 74HC154W, 4-16 line decoder/demultiplexer, 0.6wide DIP none 446 1.86 74HC190, Synchronous 4-Bit Up/Down Decade and Binary Counters DIP-16 3 - D 637 74HCT240, Octal Buffers and Line Drivers w/ 3-State outputs DIP-20 3 - D 643 1.04 74HC244, Octal Buffers And Line Drivers w/ 3-State outputs DIP-20 3 - D 647 1.43 74HCT245, Octal Bus Transceivers w/ 3-State outputs DIP-20 3 - D 649 1.13 74HCT273, Octal D-Type Flip-Flops w/ Clear DIP-20 3 - D 658 1.35 74HCT373, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 666 1.35 74HCT377, Octal D-Type Flip-Flops w/ Clock Enable DIP-20 3 - E 669 1.50 74HCT573, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 674 0.88 Type CMOS CD4000 Series CD4001, Quad 2-input -

Basics of CMOS Logic Ics Application Note

Basics of CMOS Logic ICs Application Note Basics of CMOS Logic ICs Outline: This document describes applications, functions, operations, and structure of CMOS logic ICs. Each functions (inverter, buffer, flip-flop, etc.) are explained using system diagrams, truth tables, timing charts, internal circuits, image diagrams, etc. ©2020- 2021 1 2021-01-31 Toshiba Electronic Devices & Storage Corporation Basics of CMOS Logic ICs Application Note Table of Contents Outline: ................................................................................................................................................. 1 Table of Contents ................................................................................................................................. 2 1. Standard logic IC ............................................................................................................................. 3 1.1. Devices that use standard logic ICs ................................................................................................. 3 1.2. Where are standard logic ICs used? ................................................................................................ 3 1.3. What is a standard logic IC? .............................................................................................................. 4 1.4. Classification of standard logic ICs ................................................................................................... 5 1.5. List of basic circuits of CMOS logic ICs (combinational logic circuits) -

Designing Combinational Logic Gates in Cmos

CHAPTER 6 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS In-depth discussion of logic families in CMOS—static and dynamic, pass-transistor, nonra- tioed and ratioed logic n Optimizing a logic gate for area, speed, energy, or robustness n Low-power and high-performance circuit-design techniques 6.1 Introduction 6.3.2 Speed and Power Dissipation of Dynamic Logic 6.2 Static CMOS Design 6.3.3 Issues in Dynamic Design 6.2.1 Complementary CMOS 6.3.4 Cascading Dynamic Gates 6.5 Leakage in Low Voltage Systems 6.2.2 Ratioed Logic 6.4 Perspective: How to Choose a Logic Style 6.2.3 Pass-Transistor Logic 6.6 Summary 6.3 Dynamic CMOS Design 6.7 To Probe Further 6.3.1 Dynamic Logic: Basic Principles 6.8 Exercises and Design Problems 197 198 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS Chapter 6 6.1Introduction The design considerations for a simple inverter circuit were presented in the previous chapter. In this chapter, the design of the inverter will be extended to address the synthesis of arbitrary digital gates such as NOR, NAND and XOR. The focus will be on combina- tional logic (or non-regenerative) circuits that have the property that at any point in time, the output of the circuit is related to its current input signals by some Boolean expression (assuming that the transients through the logic gates have settled). No intentional connec- tion between outputs and inputs is present. In another class of circuits, known as sequential or regenerative circuits —to be dis- cussed in a later chapter—, the output is not only a function of the current input data, but also of previous values of the input signals (Figure 6.1). -

On Negation Complexity of Injections, Surjections and Collision-Resistance in Cryptography

On Negation Complexity of Injections, Surjections and Collision-Resistance in Cryptography Douglas Miller Adam Scrivener Jesse Stern Muthuramakrishnan Venkitasubramaniam∗ Abstract Goldreich and Izsak (Theory of Computing, 2012) initiated the research on understanding the role of negations in circuits implementing cryptographic primitives, notably, considering one-way functions and pseudo-random generators. More recently, Guo, Malkin, Oliveira and Rosen (TCC, 2014) determined tight bounds on the minimum number of negations gates (i.e., negation complexity) of a wide variety of cryptographic primitives including pseudo-random functions, error-correcting codes, hardcore-predicates and randomness extractors. We continue this line of work to establish the following results: 1. First, we determine tight lower bounds on the negation complexity of collision-resistant and target collision-resistant hash-function families. 2. Next, we examine the role of injectivity and surjectivity on the negation complexity of one-way functions. Here we show that, (a) Assuming the existence of one-way injections, there exists a monotone one-way injection. Furthermore, we complement our result by showing that, even in the worst-case, there cannot exist a monotone one-way injection with constant stretch. (b) Assuming the existence of one-way permutations, there exists a monotone one-way surjection. 3. Finally, we show that there exists list-decodable codes with monotone decoders. In addition, we observe some interesting corollaries to our results. ∗University of Rochester 1 Introduction A boolean circuit C is monotone if it comprises only of fanin-2 AND and OR gates. Monotone circuits have been extensively studied in complexity theory, where one of the fundamental goals is to establish lower bounds on circuit size, and learning theory [17, 10, 5, 1, 6]. -

Novel Design of N-Bit Controllable Inverter by Quantum-Dot Cellular Automata

Int. J. Nanosci. Nanotechnol., Vol. 10, No. 2, June 2014, pp. 117-126 Novel Design of n-bit Controllable Inverter by Quantum-dot Cellular Automata M. Kianpour1, R. Sabbaghi-Nadooshan2 1- Electrical Engineering Department, Islamic Azad University, Science and Research Branch, Tehran, I. R. Iran 2- Electrical Engineering Department, Islamic Azad University, Central Tehran Branch, Tehran, I. R. Iran (*) Corresponding author: [email protected] (Received: 22 Jan. 2014 and accepted: 09 Feb. 2014) Abstract: Application of quantum-dot is a promising technology for implementing digital systems at nano-scale. Quantum-dot Cellular Automata (QCA) is a system with low power consumption and a potentially high density and regularity. Also, QCA supports the new devices with nanotechnology architecture. This technique works based on electron interactions inside quantum-dots leading to emergence of quantum features and decreasing the problem of future integrated circuits in terms of size. In this paper, we will successfully design, implement and simulate a new 2-input and 3-input XOR gate (exclusive OR gate) based on QCA with the minimum delay, area and complexities. Then, we will use XOR gates presented in this paper, in 2-bit, 4-bit and 8-bit controllable inverter in QCA. Being potentially pipeline, the QCA technology calculates with the maximum operating speed. We can use this controllable inverter in the n-bit adder/subtractor and reversible gate. Keywords: Exclusive OR(XOR) gate, Inverter, Majority gate, Quantum-dot Cellular Automata(QCA). 1. INTRODUCTION was developed in 1997 [2]. It is expected that QCA plays an important role in nanotechnology research. Quantum-dot Cellular Automata (QCA) is a Due to significant features of QCA, high density, low promising model emerging in nanotechnology. -

Five-Input Complex Gate with an Inverter Using QCA

ISSN (Print) : 2320 – 3765 ISSN (Online): 2278 – 8875 International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering (An ISO 3297: 2007 Certified Organization) Vol. 3, Issue 7, July 2014 Five-Input Complex Gate with an Inverter Using QCA Tina Suratkar1 Assistant Professor, Department of Electronics & Telecommunication Engineering, St.Vincent Pallotti College Of Engineering and Technology, Nagpur, Maharashtra, India1 ABSTRACT:This paper presents the basics of quantum dot cellular automata along with the QCA logic devices such as the QCA wire, inverter and the majority gate. The four phases of the clocking have been discussed and also the implementations of the complex gate have been done using the QCADesigner tool. The logical structures such as NAND and NOR gates using a quantum dot cellular automata complex gate composed of 3 input majority gate and an inverter have been implemented. KEYWORDS: QCA, majority gate, inverter, complex gates, QCA Designer. I.INTRODUCTION Current silicon transistor technology faces challenging problems, such as high power consumption and difficulties in feature size reduction. Nanotechnology is an alternative to these problems. The Quantum dot cellular automata (QCA) is one of the attractive alternatives [1]. Since QCAs were introduced in 1993 by lent et al, and experimentally verified in 1997. QCA is expected to achieve high device density, extremely low power consumption and very high switching speed.QCA structures are constructed as an array of quantum cells with in which every cell has an electrostatic interaction with its neighboring cells [2]. QCA applies a new form of computation, where polarization rather than the traditional current, contains the digital information. -

SN74LVC1G04 Single Inverter Gate Datasheet (Rev

Product Sample & Technical Tools & Support & Folder Buy Documents Software Community SN74LVC1G04 SCES214AD–APRIL1999–REVISED OCTOBER 2014 SN74LVC1G04 Single Inverter Gate 1 Features 3 Description 2 1• Available in the Ultra-Small 0.64-mm This single inverter gate is designed for Package (DPW) with 0.5-mm Pitch 1.65-V to 5.5-V VCC operation. • Supports 5-V VCC Operation The SN74LVC1G04 device performs the Boolean • Inputs Accept Voltages up to 5.5 V Allowing Down function Y = A. Translation to VCC The CMOS device has high output drive while maintaining low static power dissipation over a broad • Max tpd of 3.3 ns at 3.3-V VCC operating range. • Low Power Consumption, 10-μA Max ICC • ±24-mA Output Drive at 3.3-V The SN74LVC1G04 device is available in a variety of packages, including the ultra-small DPW package •Ioff Supports Live-Insertion, Partial-Power-Down with a body size of 0.8 mm × 0.8 mm. Mode, and Back-Drive Protection • Latch-Up Performance Exceeds 100 mA Device Information(1) Per JESD 78, Class II DEVICE NAME PACKAGE BODY SIZE • ESD Protection Exceeds JESD 22 SOT-23 (5) 2.9mm × 1.6mm – 2000-V Human-Body Model (A114-A) SC70 (5) 2.0mm × 1.25mm – 200-V Machine Model (A115-A) SN74LVC1G04 SON (6) 1.45mm × 1.0mm – 1000-V Charged-Device Model (C101) SON (6) 1.0mm × 1.0mm X2SON (4) 0.8mm × 0.8mm 2 Applications (1) For all available packages, see the orderable addendum at the end of the datasheet. • AV Receiver • Audio Dock: Portable • Blu-ray Player and Home Theater • Embedded PC • MP3 Player/Recorder (Portable Audio) • Personal Digital Assistant (PDA) • Power: Telecom/Server AC/DC Supply: Single Controller: Analog and Digital • Solid State Drive (SSD): Client and Enterprise • TV: LCD/Digital and High-Definition (HDTV) • Tablet: Enterprise • Video Analytics: Server • Wireless Headset, Keyboard, and Mouse 4 Simplified Schematic A Y 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. -

Logic Families

Logic Families PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Mon, 11 Aug 2014 22:42:35 UTC Contents Articles Logic family 1 Resistor–transistor logic 7 Diode–transistor logic 10 Emitter-coupled logic 11 Gunning transceiver logic 16 Transistor–transistor logic 16 PMOS logic 23 NMOS logic 24 CMOS 25 BiCMOS 33 Integrated injection logic 34 7400 series 35 List of 7400 series integrated circuits 41 4000 series 62 List of 4000 series integrated circuits 69 References Article Sources and Contributors 75 Image Sources, Licenses and Contributors 76 Article Licenses License 77 Logic family 1 Logic family In computer engineering, a logic family may refer to one of two related concepts. A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family. Many logic families were produced as individual components, each containing one or a few related basic logical functions, which could be used as "building-blocks" to create systems or as so-called "glue" to interconnect more complex integrated circuits. A "logic family" may also refer to a set of techniques used to implement logic within VLSI integrated circuits such as central processors, memories, or other complex functions. Some such logic families use static techniques to minimize design complexity. Other such logic families, such as domino logic, use clocked dynamic techniques to minimize size, power consumption, and delay. Before the widespread use of integrated circuits, various solid-state and vacuum-tube logic systems were used but these were never as standardized and interoperable as the integrated-circuit devices. -

Logic Synthesis for Quantum Computing Mathias Soeken, Martin Roetteler, Nathan Wiebe, and Giovanni De Micheli

1 Logic Synthesis for Quantum Computing Mathias Soeken, Martin Roetteler, Nathan Wiebe, and Giovanni De Micheli Abstract—Today’s rapid advances in the physical implementa- 1) Quantum computers process qubits instead of classical tion of quantum computers call for scalable synthesis methods to bits. A qubit can be in superposition and several qubits map practical logic designs to quantum architectures. We present can be entangled. We target purely Boolean functions as a synthesis framework to map logic networks into quantum cir- cuits for quantum computing. The synthesis framework is based input to our synthesis algorithms. At design state, it is on LUT networks (lookup-table networks), which play a key sufficient to assume that all input values are Boolean, role in state-of-the-art conventional logic synthesis. Establishing even though entangled qubits in superposition are even- a connection between LUTs in a LUT network and reversible tually acted upon by the quantum hardware. single-target gates in a reversible network allows us to bridge 2) All operations on qubits besides measurement, called conventional logic synthesis with logic synthesis for quantum computing—despite several fundamental differences. As a result, quantum gates, must be reversible. Gates with multiple our proposed synthesis framework directly benefits from the fanout known from classical circuits are therefore not scientific achievements that were made in logic synthesis during possible. Temporarily computed values must be stored the past decades. on additional helper qubits, called ancillae. An intensive We call our synthesis framework LUT-based Hierarchical use of intermediate results therefore increases the qubit Reversible Logic Synthesis (LHRS). -

Multiplexer-Based Design of Adders/Subtractors and Logic

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 5, Issue 6, Ver. II (Nov -Dec. 2015), PP 59-66 e-ISSN: 2319 – 4200, p-ISSN No. : 2319 – 4197 www.iosrjournals.org Multiplexer-Based Design of Adders/Subtractors and Logic Gates for Low Power VLSI Applications 1Ramesh Boda*, 2M.Charitha, 3B.Yakub, 4R.Sayanna 1, 4(Department of physics, Osmania University, Hyderabad, Telangana, India) 2(ECE, NRI College of engineering, JNTU Hyderabad, Telangana, India) 3(ECE, HITAM engineering college, JNTU Hyderabad, Telangana, India) Abstract: The emphasis in VLSI design has shifted from high speed to low power due to the rapid increase in number of portable electronic systems. Power consumption is very critical for portable video applications such as portable videophone and digital camcorder Motion estimation (ME) in the video encoder requires a huge amount of computation, and hence consumes the largest portion of power. Many of the techniques have already been used in low power design with additional techniques emerging continuously at all levels. The aim of this work is to provide a comprehensive study of low-power circuit and design techniques using CMOS (complementary metal-oxide-semiconductor) technology. This consist of circuit design; transistor size, number of transistors used in design, layout technique, cell topology, and circuit design for low power operation while paying particularly attention on the methodology of logic style. This paper presents, high-speed and high- performance multiplexer based 1 bit adders/subtractors for low-power applications such as ASIC (Application Specific Integrated Circuits), ALU (Arithmetic logic Unit). Simulations were performed by EWB (Electronic Work Bench, unisim, Xilinx) for analysis of various feature sizes. -

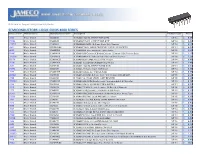

SEMICONDUCTORS: LOGIC CMOS 4000 SERIES Jameco Part# Manufacturer Manufacturer Part # Description Package Type Price 1

Click Here to Request a Large Quantity Quote SEMICONDUCTORS: LOGIC CMOS 4000 SERIES Jameco Part# Manufacturer Manufacturer Part # Description Package Type Price 1 12562 Major Brands CD4001B IC CD4001 QUAD 2-INPUT NOR GATE DIP 14 $ 0.49 675964 Major Brands CD4002B IC CD4002B DUAL 4-INPUT NOR GATE DIP 14 $ 0.49 2228711 Major Brands CD4006B IC CD4006B CMOS 18-Stage Static Shift Register DIP 14 $ 4.95 12597 Major Brands CD4007UBE IC CD4007 DUAL COMPLEMENTARY PAIR PLUS INVERTER DIP 14 $ 0.49 54623 Major Brands CD40098B IC CD40098B Hex Inverting 3-State Buffer DIP 16 $ 2.95 676481 Major Brands CD40103B IC CD40103B Counter IC Binary Counter 1 Element 8 Bit Positive Edge DIP 16 $ 1.29 2178996 Major Brands CD40104B IC CD40104B 4-Bit Bidirectional Universal Shift Register DIP 16 $ 1.95 893179 Major Brands CD40106BE IC CD40106BE CMOS Hex Schmitt Trigger DIP 14 $ 0.49 676502 Major Brands CD40110B IC CD40110 DECADE UP/DOWN COUNTER DIP 16 $ 1.49 12634 Major Brands CD4011B IC CD4011 QUAD 2-INPUT NAND GATE DIP 14 $ 0.49 675972 Major Brands CD4012B IC CD4012B Dual 4-Input NAND Gate DIP 14 $ 0.49 12677 Major Brands CD4013BE IC CD4013 DUAL D-TYPE FLIP-FLOp DIP 14 $ 0.49 2288823 Major Brands CD4014B IC CD4014B CMOS 8-Stage Static Shift Register(HD14014BP) DIP 16 $ 0.55 12706 Major Brands CD4015B IC CD4015 4-STAGE STATIC SHIFT REGISTER DIP 16 $ 0.55 2178988 Major Brands CD40163B IC CD40163B CMOS Synchronous Programmable 4-Bit Counter DIP 16 $ 0.39 12722 Major Brands CD4016B IC CD4016 DUAL QUAD BILATERAL SWITCH DIP 14 $ 0.49 12749 Major Brands CD4017B IC CD4017