Outline Circuit Logic Gate

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Dialetheists' Lies About the Liar

PRINCIPIA 22(1): 59–85 (2018) doi: 10.5007/1808-1711.2018v22n1p59 Published by NEL — Epistemology and Logic Research Group, Federal University of Santa Catarina (UFSC), Brazil. DIALETHEISTS’LIES ABOUT THE LIAR JONAS R. BECKER ARENHART Departamento de Filosofia, Universidade Federal de Santa Catarina, BRAZIL [email protected] EDERSON SAFRA MELO Departamento de Filosofia, Universidade Federal do Maranhão, BRAZIL [email protected] Abstract. Liar-like paradoxes are typically arguments that, by using very intuitive resources of natural language, end up in contradiction. Consistent solutions to those paradoxes usually have difficulties either because they restrict the expressive power of the language, orelse because they fall prey to extended versions of the paradox. Dialetheists, like Graham Priest, propose that we should take the Liar at face value and accept the contradictory conclusion as true. A logical treatment of such contradictions is also put forward, with the Logic of Para- dox (LP), which should account for the manifestations of the Liar. In this paper we shall argue that such a formal approach, as advanced by Priest, is unsatisfactory. In order to make contradictions acceptable, Priest has to distinguish between two kinds of contradictions, in- ternal and external, corresponding, respectively, to the conclusions of the simple and of the extended Liar. Given that, we argue that while the natural interpretation of LP was intended to account for true and false sentences, dealing with internal contradictions, it lacks the re- sources to tame external contradictions. Also, the negation sign of LP is unable to represent internal contradictions adequately, precisely because of its allowance of sentences that may be true and false. -

Episode 5.02 – NAND Logic

Episode 5.02 – NAND Logic Welcome to the Geek Author series on Computer Organization and Design Fundamentals. I’m David Tarnoff, and in this series, we are working our way through the topics of Computer Organization, Computer Architecture, Digital Design, and Embedded System Design. If you’re interested in the inner workings of a computer, then you’re in the right place. The only background you’ll need for this series is an understanding of integer math, and if possible, a little experience with a programming language such as Java. And one more thing. Our topics involve a bit of figuring, so it might help to keep a pencil and paper handy. In our last episode, we covered three attributes of the sum-of-product expression including its general format and the benefits derived from it, a method to generate a truth table from a given sum-of- products expression, and lastly, a simple procedure we can use to create the proper sum-of-products expression from a given truth table. In this episode, we’re going to look at a fourth attribute. While this last trait may appear to be no more than an interesting exercise in Boolean algebra, it turns out that it offers several benefits when we implement our SOP expressions with digital circuitry. In Episode 4.08 – DeMorgan’s Theorem, we showed how an inverter can be distributed across the inputs of an AND or an OR gate by flipping the operation. In other words, we can distribute an inverter from the output of an AND gate across all the gate’s inputs as long as we change the gate operation to an OR. -

Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free Systems

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Doctoral Dissertations Graduate School 12-2012 Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems Sukanya Iyer University of Tennessee, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_graddiss Part of the Biotechnology Commons Recommended Citation Iyer, Sukanya, "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems. " PhD diss., University of Tennessee, 2012. https://trace.tennessee.edu/utk_graddiss/1586 This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a dissertation written by Sukanya Iyer entitled "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Doctor of Philosophy, with a major in Life Sciences. Mitchel J. Doktycz, Major Professor We have read this dissertation and recommend its acceptance: Michael L. Simpson, Albrecht G. von Arnim, Barry D. Bruce, Jennifer L. Morrell-Falvey Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville Sukanya Iyer December 2012 Copyright © 2012 by Sukanya Iyer. -

CSE Yet, Please Do Well! Logical Connectives

administrivia Course web: http://www.cs.washington.edu/311 Office hours: 12 office hours each week Me/James: MW 10:30-11:30/2:30-3:30pm or by appointment TA Section: Start next week Call me: Shayan Don’t: Actually call me. Homework #1: Will be posted today, due next Friday by midnight (Oct 9th) Gradescope! (stay tuned) Extra credit: Not required to get a 4.0. Counts separately. In total, may raise grade by ~0.1 Don’t be shy (raise your hand in the back)! Do space out your participation. If you are not CSE yet, please do well! logical connectives p q p q p p T T T T F T F F F T F T F NOT F F F AND p q p q p q p q T T T T T F T F T T F T F T T F T T F F F F F F OR XOR 푝 → 푞 • “If p, then q” is a promise: p q p q F F T • Whenever p is true, then q is true F T T • Ask “has the promise been broken” T F F T T T If it’s raining, then I have my umbrella. related implications • Implication: p q • Converse: q p • Contrapositive: q p • Inverse: p q How do these relate to each other? How to see this? 푝 ↔ 푞 • p iff q • p is equivalent to q • p implies q and q implies p p q p q Let’s think about fruits A fruit is an apple only if it is either red or green and a fruit is not red and green. -

Transistors and Logic Gates

Introduction to Computer Engineering CS/ECE 252, Spring 2013 Prof. Mark D. Hill Computer Sciences Department University of Wisconsin – Madison Chapter 3 Digital Logic Structures Slides based on set prepared by Gregory T. Byrd, North Carolina State University Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. Transistor: Building Block of Computers Microprocessors contain millions of transistors • Intel Pentium II: 7 million • Compaq Alpha 21264: 15 million • Intel Pentium III: 28 million Logically, each transistor acts as a switch Combined to implement logic functions • AND, OR, NOT Combined to build higher-level structures • Adder, multiplexer, decoder, register, … Combined to build processor • LC-3 3-3 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. Simple Switch Circuit Switch open: • No current through circuit • Light is off • Vout is +2.9V Switch closed: • Short circuit across switch • Current flows • Light is on • Vout is 0V Switch-based circuits can easily represent two states: on/off, open/closed, voltage/no voltage. 3-4 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. N-type MOS Transistor MOS = Metal Oxide Semiconductor • two types: N-type and P-type N-type • when Gate has positive voltage, short circuit between #1 and #2 (switch closed) • when Gate has zero voltage, open circuit between #1 and #2 Gate = 1 (switch open) Gate = 0 Terminal #2 must be connected to GND (0V). 3-5 Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. P-type MOS Transistor P-type is complementary to N-type • when Gate has positive voltage, open circuit between #1 and #2 (switch open) • when Gate has zero voltage, short circuit between #1 and #2 (switch closed) Gate = 1 Gate = 0 Terminal #1 must be connected to +2.9V. -

Automated Unbounded Verification of Stateful Cryptographic Protocols

Automated Unbounded Verification of Stateful Cryptographic Protocols with Exclusive OR Jannik Dreier Lucca Hirschi Sasaˇ Radomirovic´ Ralf Sasse Universite´ de Lorraine Department of School of Department of CNRS, Inria, LORIA Computer Science Science and Engineering Computer Science F-54000 Nancy ETH Zurich University of Dundee ETH Zurich France Switzerland UK Switzerland [email protected] [email protected] [email protected] [email protected] Abstract—Exclusive-or (XOR) operations are common in cryp- on widening the scope of automated protocol verification tographic protocols, in particular in RFID protocols and elec- by extending the class of properties that can be verified to tronic payment protocols. Although there are numerous appli- include, e.g., equivalence properties [19], [24], [27], [51], cations, due to the inherent complexity of faithful models of XOR, there is only limited tool support for the verification of [14], extending the adversary model with complex forms of cryptographic protocols using XOR. compromise [13], or extending the expressiveness of protocols, The TAMARIN prover is a state-of-the-art verification tool e.g., by allowing different sessions to update a global, mutable for cryptographic protocols in the symbolic model. In this state [6], [43]. paper, we improve the underlying theory and the tool to deal with an equational theory modeling XOR operations. The XOR Perhaps most significant is the support for user-specified theory can be freely combined with all equational theories equational theories allowing for the modeling of particular previously supported, including user-defined equational theories. cryptographic primitives [21], [37], [48], [24], [35]. -

Efficient Design of 2'S Complement Adder/Subtractor Using QCA

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 2 Issue 11, November - 2013 Efficient Design of 2'S complement Adder/Subtractor Using QCA. D.Ajitha 1 Dr.K.Venkata Ramanaiah 3 , Assistant Professor, Dept of ECE, Associate Professor, ECE Dept , S.I.T.A.M..S., Chittoor, Y S R Engineering college of Yogi Vemana A.P. India. University, Proddatur. 2 4 P.Yugesh Kumar, Dr.V.Sumalatha , SITAMS,Chittoor, Associate Professor, Dept of ECE, J.N.T.U.C.E.A Ananthapur, A.P. Abstract: The alternate digital design of In this paper efficient 1-bit full adder [10] has CMOS Technology fulfilled with the Quantum taken to implement the above circuit by comparing with previous 1-bit full adder designs [7-9]. A full adder with Dot Cellular Automata. In this paper, the 2’s reduced one inverter is used and implemented with less complement adder design with overflow was number of cells. Latency and power consumption is also implemented as first time in QCA & have the reduced with the help of optimization process [5]. smallest area with the least number of cells, Therefore efficient two‟s complement adder is also reduced latency and low cost achieved with designed using the efficient 1-bit full adder [10] and reduced all the parameters like area delay and cost one inverter reduced full adder using majority compared with CMOS [14]. logic. The circuit was simulated with QCADesigner and results were included in The paper is organized as follows: In Section 2, this paper. QCA basics and design methods to implement gates functionalities is presented. -

ECSE-4760 Real-Time Applications in Control & Communications

Rensselaer Polytechnic Institute ECSE-4760 Real-Time Applications in Control & Communications EXPERIMENTS IN DIGITAL LOGIC DESIGN Number of Sessions – 4 INTRODUCTION Over the past few decades the digital world has come into its own. Even though engineering has gone into specialization, it is necessary to understand digital circuits to be able to communicate with others. This experiment attempts to teach a simple method of designing digital circuits. Due to the quick pace of the lab, it is highly recommended that you read one of the references. This will enable you to proceed quickly through the preliminary problems so you will have more time for the design problems. The following is an outline of the experiment. Following each section will be a set of questions that should be answered to show an understanding of the material presented. Any difficulties should be referred to a reference or your instructor. You should use the DesignWorks (LogicWorks or any other you may have) logic circuit simulator on the Macintosh after most sections to cement together all the preceding sections. BACKGROUND THEORY Boolean Algebra Switching Algebra Combinational Logic Minimization Flip-Flops and Registers Counters Synthesis of Synchronous Circuits EXPERIMENTAL PROCEDURE Questions and Problems Simulator Operation & FPGA Implementation REFERENCES It is required that you show all circuits, as built, in your write-up. Please include equations too. The first part of the procedure section contains all the questions and problems to be answered and the second part describes the use of DesignWorks. Note: all references to DesignWorks (on Macintosh computers) throughout this procedure may be replaced with LogicWorks on the lab Windows PCs. -

CS 50010 Module 1

CS 50010 Module 1 Ben Harsha Apr 12, 2017 Course details ● Course is split into 2 modules ○ Module 1 (this one): Covers basic data structures and algorithms, along with math review. ○ Module 2: Probability, Statistics, Crypto ● Goal for module 1: Review basics needed for CS and specifically Information Security ○ Review topics you may not have seen in awhile ○ Cover relevant topics you may not have seen before IMPORTANT This course cannot be used on a plan of study except for the IS Professional Masters program Administrative details ● Office: HAAS G60 ● Office Hours: 1:00-2:00pm in my office ○ Can also email for an appointment, I’ll be in there often ● Course website ○ cs.purdue.edu/homes/bharsha/cs50010.html ○ Contains syllabus, homeworks, and projects Grading ● Module 1 and module are each 50% of the grade for CS 50010 ● Module 1 ○ 55% final ○ 20% projects ○ 20% assignments ○ 5% participation Boolean Logic ● Variables/Symbols: Can only be used to represent 1 or 0 ● Operations: ○ Negation ○ Conjunction (AND) ○ Disjunction (OR) ○ Exclusive or (XOR) ○ Implication ○ Double Implication ● Truth Tables: Can be defined for all of these functions Operations ● Negation (¬p, p, pC, not p) - inverts the symbol. 1 becomes 0, 0 becomes 1 ● Conjunction (p ∧ q, p && q, p and q) - true when both p and q are true. False otherwise ● Disjunction (p v q, p || q, p or q) - True if at least one of p or q is true ● Exclusive Or (p xor q, p ⊻ q, p ⊕ q) - True if exactly one of p or q is true ● Implication (p → q) - True if p is false or q is true (q v ¬p) ● -

Negation-Limited Complexity of Parity and Inverters

数理解析研究所講究録 第 1554 巻 2007 年 131-138 131 Negation-Limited Complexity of Parity and Inverters 森住大樹 1 垂井淳 2 岩間一雄 1 1 京都大学大学院情報学研究科, {morizumi, iwama}@kuis.kyoto-u.ac.jp 2 電気通信大学情報通信工学科, [email protected] Abstract 1 Introduction and Summary In negation-limited complexity, one considers circuits Although exponential lower bounds are known for the with a limited number of NOT gates, being mo- monotone circuit size [4], [6], at present we cannot tivated by the gap in our understanding of mono- prove a superlinear lower bound for the size of circuits tone versus general circuit complexity, and hop- computing an explicit Boolean function: the largest ing to better understand the power of NOT gates. known lower bound is $5n-o(n)[\eta, |10],$ $[8]$ . It is We give improved lower bounds for the size (the natural to ask: What happens if we allow a limited number of $AND/OR/NOT$) of negation-limited cir- number of NOT gatae? The hope is that by the study cuits computing Parity and for the size of negation- of negation-limited complexity of Boolean functions limited inverters. An inverter is a circuit with inputs under various scenarios [3], [17], [15]. [2], $|1$ ], $[13]$ , we $x_{1},$ $\ldots,x_{\mathfrak{n}}$ $\neg x_{1},$ $po\mathfrak{n}^{r}er$ and outputs $\ldots,$ $\neg x_{n}$ . We show that understand the of NOT gates better. (a) For $n=2^{f}-1$ , circuits computing Parity with $r-1$ We consider circuits consisting of $AND/OR/NOT$ NOT gates have size at least $6n-\log_{2}(n+1)-O(1)$, gates. -

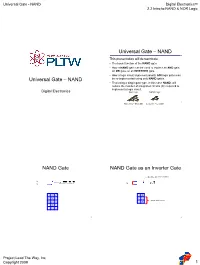

Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic

Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic Universal Gate – NAND This presentation will demonstrate • The basic function of the NAND gate. • How a NAND gate can be used to replace an AND gate, an OR gate, or an INVERTER gate. • How a logic circuit implemented with AOI logic gates can Universal Gate – NAND be re-implemented using only NAND gates. • That using a single gate type, in this case NAND, will reduce the number of integrated circuits (IC) required to implement a logic circuit. Digital Electronics AOI Logic NAND Logic 2 More ICs = More $$ Less ICs = Less $$ NAND Gate NAND Gate as an Inverter Gate X X X (Before Bubble) X Z X Y X Y X Z X Y X Y Z X Z 0 0 1 0 1 Equivalent to Inverter 0 1 1 1 0 1 0 1 1 1 0 3 4 Project Lead The Way, Inc Copyright 2009 1 Universal Gate - NAND Digital Electronics 2.2 Intro to NAND & NOR Logic NAND Gate as an AND Gate NAND Gate as an OR Gate X X Y Y X X Z X Y X Y Y Z X Y X Y X Y Y NAND Gate Inverter Inverters NAND Gate X Y Z X Y Z 0 0 0 0 0 0 0 1 0 0 1 1 Equivalent to AND Gate Equivalent to OR Gate 1 0 0 1 0 1 1 1 1 1 1 1 5 6 NAND Gate Equivalent to AOI Gates Process for NAND Implementation 1. -

EE 434 Lecture 2

EE 330 Lecture 6 • PU and PD Networks • Complex Logic Gates • Pass Transistor Logic • Improved Switch-Level Model • Propagation Delay Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation Source Gate Drain Drain Bulk Gate n-channel MOSFET Source Equivalent Circuit for n-channel MOSFET D D • Source assumed connected to (or close to) ground • VGS=0 denoted as Boolean gate voltage G=0 G = 0 G = 1 • VGS=VDD denoted as Boolean gate voltage G=1 • Boolean G is relative to ground potential S S This is the first model we have for the n-channel MOSFET ! Ideal switch-level model Review from Last Time MOS Transistor Qualitative Discussion of p-channel Operation Source Gate Drain Drain Bulk Gate Source p-channel MOSFET Equivalent Circuit for p-channel MOSFET D D • Source assumed connected to (or close to) positive G = 0 G = 1 VDD • VGS=0 denoted as Boolean gate voltage G=1 • VGS= -VDD denoted as Boolean gate voltage G=0 S S • Boolean G is relative to ground potential This is the first model we have for the p-channel MOSFET ! Review from Last Time Logic Circuits VDD Truth Table A B A B 0 1 1 0 Inverter Review from Last Time Logic Circuits VDD Truth Table A B C 0 0 1 0 1 0 A C 1 0 0 B 1 1 0 NOR Gate Review from Last Time Logic Circuits VDD Truth Table A B C A C 0 0 1 B 0 1 1 1 0 1 1 1 0 NAND Gate Logic Circuits Approach can be extended to arbitrary number of inputs n-input NOR n-input NAND gate gate VDD VDD A1 A1 A2 An A2 F A1 An F A2 A1 A2 An An A1 A 1 A2 F A2 F An An Complete Logic Family Family of n-input NOR gates forms