Diode Logic). • Explain the Need for Introducing Transistors in the Output (DTL and TTL

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Lecture17 08 04 2010

EE40 Lecture 17 Josh Hug 8/04/2010 EE40 Summer 2010 Hug 1 Logistics • HW8 will be due Friday • Mini-midterm 3 next Wednesday – 80/160 points will be a take-home set of design problems which will utilize techniques we’ve covered in class • Handed out Friday • Due next Wednesday – Other 80/160 will be an in class midterm covering HW7 and HW8 • Final will include Friday and Monday lecture, Midterm won’t – Design problems will provide practice EE40 Summer 2010 Hug 2 Project 2 • Booster lab actually due next week – For Booster lab, ignore circuit simulation, though it may be instructive to try the Falstad simulator • Project 2 due next Wednesday – Presentation details to come [won’t be mandatory, but we will ask everyone about their circuits at some point] EE40 Summer 2010 Hug 3 Project 2 • For those of you who want to demo Project 2, we’ll be doing demos in lab on Wednesday at some point – Will schedule via online survey EE40 Summer 2010 Hug 4 CMOS/NMOS Design Correction • (Sent by email) • My on-the-fly explanation was correct, but not the most efficient way – If your FET circuit is implementing a logic function with a bar over it, i.e. • 푍 = 퐴 + 퐵퐶 + 퐷 + 퐸퐹 퐺 + 퐻 – Then don’t put an inverter at the output, it just makes things harder and less efficient • Sorry, on-the-fly-explanations can be dicey EE40 Summer 2010 Hug 5 CMOS • CMOS Summary: – No need for a pull-up or pull-down resistor • Though you can avoid this even with purely NMOS logic (see HW7) – Greatly reduced static power dissipation vs. -

A Vertical Resonant Tunneling Transistor for Application in Digital Logic Circuits

1028 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 48, NO. 6, JUNE 2001 A Vertical Resonant Tunneling Transistor for Application in Digital Logic Circuits Jürgen Stock, Jörg Malindretos, Klaus Michael Indlekofer, Michael Pöttgens, Arno Förster, and Hans Lüth Abstract—A vertical resonant tunneling transistor (VRTT) has In this paper, we report on the fabrication of a vertical res- been developed, its properties and its application in digital logic onant tunneling transistor (VRTT) with low peak voltage and circuits based on the monostable-bistable transition logic element good peak current control by means of a Schottky gate. The (MOBILE) principle are described. The device consists of a small mesa resonant tunneling diode (RTD) in the GaAs/AlAs material asymmetric behavior of the current-voltage ( ) character- system surrounded by a Schottky gate. We obtain low peak voltages istics is analyzed and the transistors are characterized with re- using InGaAs in the quantum well and the devices show an excel- spect to their peak voltage, peak-to-valley ratio (PVR), peak cur- lent peak current control by means of an applied gate voltage. A rent density, and gate function. We demonstrate the switching self latching inverter circuit has been fabricated using two VRTTs functionality of a self latching inverter circuit consisting of two and the switching functionality was demonstrated at low frequen- cies. VRTTs. Index Terms—Monostable-bistable transition logic element (MOBILE), monostable-to-bistable transition, resonant tunneling II. DEVICE FABRICATION diode (RTD), resonant tunneling transistor. A. Layer Structure The epitaxial structure used to fabricate the VRTT device was I. INTRODUCTION grown by molecular beam epitaxy (MBE) on semi-insulating N recent years, several new memory and logic circuits based (100)-orientated GaAs substrate. -

Digital Logic and Design (Course Code: EE222) Ltlecture 6: Lliogic Famili Es

Indian Institute of Technology Jodhpur, Year 2018‐2019 Digital Logic and Design (Course Code: EE222) LtLecture 6: LiLogic Fam ilies Course Instructor: Shree Prakash Tiwari EilEmail: sptiwari@iitj .ac.i n Webpage: http://home.iitj.ac.in/~sptiwari/ Course related documents will be uploaded on http://home.iitj.ac.in/~sptiwari/DLD/ Note: The information provided in the slides are taken form text books Digital Electronics (including Mano & Ciletti), and various other resources from internet, for teaching/academic use only 1 Overview •Early families (DL, RTL) • TTL •Evolution of TTL family • CMOS family and its evolution 2 Logic families Diode Logic (DL) •simpp;lest; does not scale •NOT not possible (need = an active element) Resistor-Transistor Logic (RTL) • replace diode switch with a tittransistor switc h •can be cascaded = • large power draw 3 Logic families Diode-Transistor Logic (DTL) • essentially diode logic with transistor amplification • reduced power consumption •faster than RTL = DL AND gate Saturating inverter 4 Logic Families • The bipolar transistor as a logical switch TTL Bipolar Transistor-Transistor Logic (TTL) •First introduced by in 1964 (Texas Instruments) •TTL has shaped digital technology in many ways • Standard TTL family (e.g. 7400) is obsolete •Newer TTL families used (e.g. 74ALS00) 6 TTL Bipolar Transistor-Transistor Logic (TTL) Distinct features •Multi‐emitter transistors 7 TTL A Standard TTL NAND gate 8 TTL A standard TTL NAND gate with open collector output 9 TTL evolution Schottky series (74LS00) TTL •A major -

Logic Families – Characteristics and Types Table of Content

1 Module-1: Logic Families – Characteristics and Types Table of Content 1.1 Introduction 1.2 Logic families 1.3 Positive and Negative logic 1.4 Types of logic families 1.5 Characteristics of logic families 1.6 Evolution of logic families 1.7 Classification of logic families 1.8 Summary Learning Outcome: After completing this module, you will be able to 1. Understand need of logic digital ICs 2. Understand significance of logic families 3. Understand characteristics of logic families 4. Identify different types of logic families 5. Know about evolution of different logic families Digital Electronics Electronic Science 1. Logic families 2 1.1 Introduction The first logic circuit was developed using discrete circuit components. Using advance techniques, these complex circuits can be miniaturized and produced on a small piece of semiconductor material like silicon. Such a circuit is called integrated circuit (IC). Now-a-days, all the digital circuits are available in IC form. While producing digital ICs, different circuit configurations and manufacturing technologies are used. This results into a specific logic family. Each logic family designed in this way has identical electrical characteristics such as supply voltage range, speed of operation, power dissipation, noise margin etc. In this module, we discuss significance and types of logic families. The positive and negative logic and its significance are also discussed. In addition to this, different characteristics which are the key parameters in deciding the logic family for any circuit design are discussed in detail. The module is concluded with explanation of the brief history of the logic family in terms of discrete logic circuits. -

Digital Devices Based on Lambda Diodes.Pdf

ALEXEI KRASNOPOLSKI 135, Ocee View Ct. Alpharetta, GA, 30022-6601 DIGITAL DEVICES BASED ON COMPLEMENTARY JUNCTION FIELD EFFECT TRANSISTORS PREAMBLE Now CMOS transistors are widespread component basis for digital integrated circuits. But its have a disadvantage that is high sensitiveness to environment effects such as temperature and radiation. The disadvantage restrains using CMOS IC in electronics equipment worked in extremal conditions. There is a alternative component basis that is junction field effect transistors (JFET) which possesses more high resistance to environment effects. The cause of the stability is physical nature of JFET, namely electric charges are carried by majority carriers and in a depth of semiconductor as opposed to CMOS transistor, which has a current, carried by minority carriers and on surface of semiconductor. JFET is appropriate to base element of radiation hardened Integrated Circuits. Complexity and inefficiency schematic methods of JFET logic gate design do not allow widely using JFET in area of digital IC. There is a fact that JFET gate's control voltage has a polarity that is reversal of polarity of drain voltage. That fact results in necessity to have two voltage supply sources and complex schemes of a matching of a logic level voltage between JFET gate's inputs and outputs. Given review introduces schematic methods of developing of a logic gates based on complementary JFET (CJFET) that are free against above disadvantages. Namely, it works with only one voltage supply source, without shift of logical level of voltage between gate's input and output. And the CJFET gates have micro-power ability, the same as CMOS gates: its work without power drain in static states. -

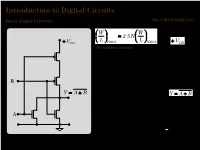

Introduction to Digital Circuits

Introduction to Digital Circuits Basic Logic Circuits The CMOS NOR Gate W W ≈ 2.5N L L + VDD PMOS NMOS + VDD N= number of inputs B B Y = A + B Y = A + B A A 1 ©Loberg INTRODUCTION TO DIGITAL CIRCUITS Basic Logic Circuits The CMOS NAND Gate W 2.5 W ≈ L PMOS N L NMOS + VDD N= number of inputs Y = A ⋅ B B A 2 ©Loberg INTRODUCTION TO DIGITAL CIRCUITS Basic Logic Circuits Complex CMOS Gates The pull-up and pull-down networks must have complementary Boolean functions. +VDD Example function : A Pull-up network For the pull-up B PMOS devices Y Y = A ⋅ (B + C ⋅ D) Y and its complement Pull-down For the pull-down A B network Y Y = A ⋅ (B + C ⋅ D) = A + B ⋅ (C + D) NMOS devices A general CMOS logic gate. Both the pull-up and pull-down networks have the same inputs. 3 ©Loberg INTRODUCTION TO DIGITAL CIRCUITS Basic Logic Circuits Complex CMOS Gates It can be shown that the pull-up and pull-down networks + of a complementary CMOS structure are dual networks. VDD (De Morgan) A = ⋅ + ⋅ Y A (B C D) A parallel connection of transistors in the pull-up B Pull-up network network corresponds to a series connection of the C corresponding devices in pull-down network, and vice versa. D Pull-up network : Subnet CD has series connection − Y (C D) Subnet B has parallel connection with CD B (C − D) B Y = A + B ⋅ (C + D) Subnet A has series connection with A − (B (C − D)) Pull-down network previous parallel net A C D Pull-down network : Subnet CD has parallel connection (C D) Subnet B has series connection with CD (B − (C D)) Subnet A has parallel -

Logic Families

Logic Families PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Mon, 11 Aug 2014 22:42:35 UTC Contents Articles Logic family 1 Resistor–transistor logic 7 Diode–transistor logic 10 Emitter-coupled logic 11 Gunning transceiver logic 16 Transistor–transistor logic 16 PMOS logic 23 NMOS logic 24 CMOS 25 BiCMOS 33 Integrated injection logic 34 7400 series 35 List of 7400 series integrated circuits 41 4000 series 62 List of 4000 series integrated circuits 69 References Article Sources and Contributors 75 Image Sources, Licenses and Contributors 76 Article Licenses License 77 Logic family 1 Logic family In computer engineering, a logic family may refer to one of two related concepts. A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family. Many logic families were produced as individual components, each containing one or a few related basic logical functions, which could be used as "building-blocks" to create systems or as so-called "glue" to interconnect more complex integrated circuits. A "logic family" may also refer to a set of techniques used to implement logic within VLSI integrated circuits such as central processors, memories, or other complex functions. Some such logic families use static techniques to minimize design complexity. Other such logic families, such as domino logic, use clocked dynamic techniques to minimize size, power consumption, and delay. Before the widespread use of integrated circuits, various solid-state and vacuum-tube logic systems were used but these were never as standardized and interoperable as the integrated-circuit devices. -

Digital Logic Circuits • Digital Describes Any System Based on Discontinuous Data Or Events

Digital Logic Circuits • Digital describes any system based on discontinuous data or events. Typically digital is computer data or electronic sampling of an analog signal. Computers are digital machines because at their most basic level they may distinguish between just two values, 0 and 1, or off and on. All data that a computer processes must be encoded digitally, as a series of zeroes and ones. • The opposite of digital is analog. A typical analog device is a clock in which the hands move continuously around the face. Such a clock is capable of indicating every possible time of day. In contrast, a digital clock is capable of representing only a finite number of times (every tenth of a second, for example). 1 Binary Signals Figure 13.3 Logic gate circuits are designed to input and output only two types of signals: “high” (1) and “low” (0), as represented by a variable voltage: full power supply voltage for a “high” state and zero voltage for a “low” state 2 Digital Logic Circuits Logic is defined as the science of reasoning. It is the development of a reasonable or logical conclusion based on known information. Voltage Analog of Internal Combustion Engine in-Cylinder Pressure Figure 13.1 3 Logic Gates • A gate is an electronic circuit that performs a logical operation. Logic gates are the basic building blocks for digital electronic circuits. A switching circuit or circuit is a composition of gates. Operations on the binaries 0, 1 may be viewed as truth functional operations, and binary arithmetic as an application of propositional logic. -

Diode Transistor Logic

Chapter 5 DIODE TRANSISTOR LOGIC Resistor-Transistor Logic was an early form of logic used in the 1950's and early 1960's. RTL was made from discrete transistors and resistors and manufactured on printed circuit boards with several gates per board. These boards were plugged into board sockets with wiring on the socket pins determining the system function. RTL was a big improvement over vacuum tube technology previously used, requiring less than one quarter the space and one tenth the power dissipation. RTL was superceded in the 1960's by Diode- Transistor Logic and then Transistor-Transistor Logic, DTL and TTL respectively. DTL was initially made with discrete transistors and resistors before being integrated onto silicon. One early form of DTL, used by IBM Corp in the 360 family of computers, was really a hybrid technology. Transistor and diode chips were glued to a ceramic substrate and aluminum resistor paste was deposited on the substrate to make resistors. Finally the ceramic base and components were hermetically sealed in an aluminum can. This family was used extensively in IBM products in the middle to late 1960's. While this family was not a true integrated circuit, it was very successful and was less expensive than true integrated circuits for several years. By the early 1970's integrated circuits became quite common and DTL gave way to TTL which was more appropriate to integrated circuit technology. While DTL is no longer commercially used, we will discuss it because it is similar to and easier to understand than TTL, and because designers still find the configuration of value. -

Logic Family

LOGIC FAMILY LOGIC FAMILY In computer engineering, a logic family may refer to one of two related concepts. A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family. Many logic families were produced as individual components, each containing one or a few related basic logical functions, which could be used as "building-blocks" to create systems or as so-called "glue" to interconnect more complex integrated circuits. A "logic family" may also refer to a set of techniques used to implement logic within VLSI integrated circuits such as central processors, memories, or other complex functions. Some such logic families use static techniques to minimize design complexity. Other such logic families, such as domino logic, use clocked dynamic techniques to minimize size, power consumption and delay. Before the widespread use of integrated circuits, various solid-state and vacuum-tube logic systems were used but these were never as standardized and interoperable as the integrated-circuit devices. Technologies The list of packaged building-block logic families can be divided into categories, listed here in roughly chronological order of introduction, along with their usual abbreviations: Resistor–transistor logic(RTL) o Direct-coupled transistor logic(DCTL) o Resistor–capacitor–transistor logic (RCTL) Diode–transistor logic(DTL) o Complemented transistor diode logic -

Chapter -1 Logic Families

CHAPTER -1 LOGIC FAMILIES 1.) Logic families classification a.) TTL…Transistor-transistor logic (TTL) is a digital logic design in which bipolar transistor s act on direct-current pulses. Many TTL logic gate s are typically fabricated onto a singleintegrated circuit (IC). TTL ICs usually have four-digit numbers beginning with 74 or 54. A TTL device employs transistor s with multiple emitters in gates having more than one input. TTL is characterized by high switching speed (in some cases upwards of 125 MHz ), and relative immunity to noise . Its principle drawback is the fact that circuits using TTL draw more current than equivalent circuits using metal oxide semiconductor ( MOS ) logic. Low-current TTL devices are available, but the reduced current demand comes at the expense of some operating speed. b.) ECL…In electronics, emitter-coupled logic (ECL) is a high-speed integrated circuit bipolar transistor logic family.ECL uses an overdriven BJT differential amplifier with single-ended input and limited emitter current to avoid the saturated (fully on) region of operation and its slow turn-off behavior c.) CMOS…The term CMOS stands for “Complementary Metal Oxide Semiconductor”. CMOS technology is one of the most popular technology in the computer chip design industry and broadly used today to form integrated circuits in numerous and varied applications. Today’s computer memories, CPUs and cell phones make use of this technology due to several key advantages. This technology makes use of both P channel and N channel semiconductor devices. The main advantage of CMOS over NMOS and BIPOLAR technology is the much smaller power dissipation. -

Chapter 3 Fabrication and Characterization of Nanowire Logic

48 Chapter 3 Fabrication and characterization of nanowire logic circuits 3.1 Introduction Complementary symmetry logic gates involve both p- and n-type transistors. Such logic gates outperform structures based upon pure p- or n-type technology with a key characteristic of low static power consumption, implying significant advantages for ever-denser circuit integration.1 In fact, beginning in the early 1980s, there was a forced move from NMOS to complementary technology despite the increased fabrication complications. Today, a similar trend is occurring in the field of semiconducting nanowires (NWs). These promising building blocks for electronics are not dependent upon existing lithographic limitations.2, 3 Si NWs, in particular, are appealing because 4, 5 they are relatively straightforward to prepare, the Si/SiO2 interface is attractive, and Si NWs exhibit some compatibility with more traditional Si-based technologies.6, 7 Si NW logic gates have been largely based upon p-FETs because they have been historically 49 more reliable to fabricate.6, 8, 9 A few complementary NW devices have been reported, including p-type Si/n-type Si or GaN heterojunctions for diode logic,10, 11 or carbon nanotube (CNT) based inverters.12, 13 These systems are limited by both the stochastic chemical nature of the NW formation and doping and by the very challenging issues involving the assembly of devices into even the most basic circuits.6, 10, 12, 14 For NW electronics to have practical applications, both p- and n-type devices must be integrated onto the same substrate using a technique that is controllable, scalable, and that permits increasingly complex functionalities to be implemented.