621 212 Electronics and Communication Engineering Ec6304/Linear Integrated Circuits

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Transistor Circuit Guidebook Byron Wels TAB BOOKSBLUE RIDGE SUMMIT, PA

TAB BOOKS No. 470 34.95 By Byron Wels TransistorCircuit GuidebookByronWels TABBLUE RIDGE BOOKS SUMMIT,PA. 17214 Preface beforemeIa supposepioneer (along the my withintransistor firstthe many field.experiencewith wasother Weknown. World were using WarUnlike solid-stateIIsolid-state GIs) today's asdevices somewhat experimen- receivers marks of FIRST EDITION devicester,ownFirst, withsemiconductors! youwith a choice swipedwhichor tank. ofto a sealed,Here'sexperiment, pairThen ofhow encapsulated, you earphones we carefullywe did had it: from totookand construct the veryonenearest exoticof our the THIRDSECONDFIRST PRINTING-SEPTEMBER PRINTING-AUGUST PRINTING-JANUARY 1972 1970 1968 plane,wasyouAnphonesantenna. emptywound strung jeep,apart After toiletfull outand ofclippingas paper wire,unwoundhigh closelyrollandthe servedascatchthe far spaced.wire offas as itfrom a thewouldsafetyThe thecoil remaining-pin,magnetreach-for form, you inside.which stuckwire the Copyright © 1968by TAB BOOKS coatedNext,it into youneeded,a hunkribbons of -ofwooda razor -steel, soblade.the but point Oh,aItblued was noneprojected placedblade of the -quenchat so fancy right the pointplastic-bluedangles.of -, Reproduction or publicationPrinted inof the ofAmerica the United content States in any manner, with- themindfoundphoneground pin you,the was couldserved right not wired contact lacquerspotas toa onground blade, it. theblued.blade'sAconnector, pin,bayonet bluing,and stuck antennaand you hilt thecould coil.-deep other actuallyIfin ear- youthe isoutherein. assumed express -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

Differential Amplifiers

www.getmyuni.com Operational Amplifiers: The operational amplifier is a direct-coupled high gain amplifier usable from 0 to over 1MH Z to which feedback is added to control its overall response characteristic i.e. gain and bandwidth. The op-amp exhibits the gain down to zero frequency. Such direct coupled (dc) amplifiers do not use blocking (coupling and by pass) capacitors since these would reduce the amplification to zero at zero frequency. Large by pass capacitors may be used but it is not possible to fabricate large capacitors on a IC chip. The capacitors fabricated are usually less than 20 pf. Transistor, diodes and resistors are also fabricated on the same chip. Differential Amplifiers: Differential amplifier is a basic building block of an op-amp. The function of a differential amplifier is to amplify the difference between two input signals. How the differential amplifier is developed? Let us consider two emitter-biased circuits as shown in fig. 1. Fig. 1 The two transistors Q1 and Q2 have identical characteristics. The resistances of the circuits are equal, i.e. RE1 = R E2, RC1 = R C2 and the magnitude of +VCC is equal to the magnitude of �VEE. These voltages are measured with respect to ground. To make a differential amplifier, the two circuits are connected as shown in fig. 1. The two +VCC and �VEE supply terminals are made common because they are same. The two emitters are also connected and the parallel combination of RE1 and RE2 is replaced by a resistance RE. The two input signals v1 & v2 are applied at the base of Q1 and at the base of Q2. -

50 Simple L.E.D. Circuits

50 Simple L.E.D. Circuits R.N. SOAR r de Historie v/d Radi OTH'IEK 50 SIMPLE L.E.D. CIRCUITS by R. N. SOAR BABANI PRESS The Publishing Division of Babani Trading and Finance Co. Ltd. The Grampians Shepherds Bush Road London W6 7NI- England Although every care is taken with the preparation of this book, the publishers or author will not be responsible in any way for any errors that might occur. © 1977 BA BAN I PRESS I.S.B.N. 0 85934 043 4 First Published December 1977 Printed and Manufactured in Great Britain by C. Nicholls & Co. Ltd. f t* -i. • v /“ ..... tr> CONTENTS U.V.H.R* Circuit Page No. 1 LED Pilot Light......................................... 7 2 LED Stereo Beacon.................................... 8 3 Stereo Decoder Mono/Sterco Indicator . 9 4 Subminiature LED Torch........................... 10 5 Low Voltage Low Current Supply............ 11 6 Microlight Indicator .................................. 12 7 Ultra Low Current LED Switching Indicator 13 8 LED Stroboscope....................................... 14 9 12 Volt Car Circuit Tester........................... 15 10 Two Colour LED......................................... 16 11 12 Volt Car “Fuse Blown” Indicator.......... 17 12 LED Continuity Tester............................... 17 13 LED Current Overload Indicator.............. 18 14 LED Current Range Indicator................... 20 15 1.5 Volt LED “Zener”................. '............ 22 16 Extending Zener Voltage........................... 22 17 Four Voltage Regulated Supply................. 23 18 PsychaLEDic Display.................................. 24 .19 Dual Colour Display.................................... 25 20 Dual Signal Device....................................... 26 21 LED Triple Signalling.................................. 27 22 Sub-Miniature Light Source for Model Railways . 28 23 Portable Television Protection Circuit . 29 24 Improved Portable TV Protection Circuit 30 25 LED Battery Tester.............................. -

Fully-Differential Amplifiers

Application Report S Fully-Differential Amplifiers James Karki AAP Precision Analog ABSTRACT Differential signaling has been commonly used in audio, data transmission, and telephone systems for many years because of its inherent resistance to external noise sources. Today, differential signaling is becoming popular in high-speed data acquisition, where the ADC’s inputs are differential and a differential amplifier is needed to properly drive them. Two other advantages of differential signaling are reduced even-order harmonics and increased dynamic range. This report focuses on integrated, fully-differential amplifiers, their inherent advantages, and their proper use. It is presented in three parts: 1) Fully-differential amplifier architecture and the similarities and differences from standard operational amplifiers, their voltage definitions, and basic signal conditioning circuits; 2) Circuit analysis (including noise analysis), provides a deeper understanding of circuit operation, enabling the designer to go beyond the basics; 3) Various application circuits for interfacing to differential ADC inputs, antialias filtering, and driving transmission lines. Contents 1 Introduction . 3 2 What Is an Integrated, Fully-Differential Amplifier? . 3 3 Voltage Definitions . 5 4 Increased Noise Immunity . 5 5 Increased Output Voltage Swing . 6 6 Reduced Even-Order Harmonic Distortion . 6 7 Basic Circuits . 6 8 Circuit Analysis and Block Diagram . 8 9 Noise Analysis . 13 10 Application Circuits . 15 11 Terminating the Input Source . 15 12 Active Antialias Filtering . 20 13 VOCM and ADC Reference and Input Common-Mode Voltages . 23 14 Power Supply Bypass . 25 15 Layout Considerations . 25 16 Using Positive Feedback to Provide Active Termination . 25 17 Conclusion . 27 1 SLOA054E List of Figures 1 Integrated Fully-Differential Amplifier vs Standard Operational Amplifier. -

1. Draw the Circuit Diagram of Basic CMOS Gate and Explain the Operation

1. Draw the circuit diagram of basic CMOS gate and explain the operation. The basic CMOS inverter circuit is shown in below figure. It consists of two MOS transistors connected in series (1-PMOS and 1-NMOS). The P-channel device source is connected to +VDD and the N-channel device source is connected to ground. The gates of the two devices are connected together as the common input VIN and the drains are connected together as the common output VOUT. Case 1: When Input is LOW If input VIN is low then the n-channel transistor Q1 is off, and it acts as a open switch since its Vgs is 0, but the top, p-channel transistor Q2 is on, and acts as a closed switch since its Vgs is a large negative value. This produces ouput voltage approximately +VDD as shown in fig 6(a). VOUT=VDD Case 2: When Input is HIGH If input VIN is high then the n-channel transistor Q1 is on, and it acts as a closed switch , but the top, p-channel transistor Q2 is off, and acts as a open switch. This produces ouput voltage approximately 0V as shown in fig 6(b). FUNCTION TABLE: VOUT=0V INPU Q1 Q2 OUTP T UT (VIN) (VOUT) 0 ON OFF 1 1 OFF ON 0 LOGIC SYMBOL: 2. Draw the resistive model of a CMOS inverter circuit and explain its behavior for LOW and HIGH outputs. CIRCUIT BEHAVIOR WITH RESISTIVE LOADS: CMOS gate inputs have very high impedance and consume very little current from the circuits that drive them. -

Circuit Diagram

CIRCUIT DIAGRAM Common schematic diagram symbols (US symbols) A circuit diagram (also known as an electrical diagram, elementary diagram, or electronic schematic) is a simplified conventional graphical representation of an electrical circuit. A pictorial circuit diagram uses simple images of components, while a schematic diagram shows the components of the circuit as simplified standard symbols; both types show the connections between the devices, including power and signal connections. Arrangement of the components interconnections on the diagram does not correspond to their physical locations in the finished device. Unlike a block diagram or layout diagram, a circuit diagram shows the actual wire connections being used. The diagram does not show the physical arrangement of components. A drawing meant to depict what the physical arrangement of the wires and the components they connect is called "artwork" or "layout" or the "physical design." Circuit diagrams are used for the design (circuit design), construction (such as PCB layout), and maintenance of electrical and electronic equipment. Symbols Circuit diagram symbols have differed from country to country and have changed over time, but are now to a large extent internationally standardized. Simple components often had symbols intended to represent some feature of the physical construction of the device. For example, the symbol for a resistor shown here dates back to the days when that component was made from a long piece of wire wrapped in such a manner as to not produce inductance, which would have made it a coil. These wirewound resistors are now used only in high-power applications, smaller resistors being cast from carbon composition (a mixture of carbon and filler) or fabricated as an insulating tube or chip coated with a metal film. -

Mosfet Differential Amplifier (Two-Week Lab)

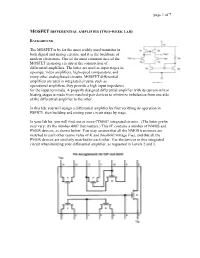

page 1 of 7 MOSFET DIFFERENTIAL AMPLIFIER (TWO-WEEK LAB) BACKGROUND The MOSFET is by far the most widely used transistor in both digital and analog circuits, and it is the backbone of modern electronics. One of the most common uses of the MOSFET in analog circuits is the construction of differential amplifiers. The latter are used as input stages in op-amps, video amplifiers, high-speed comparators, and many other analog-based circuits. MOSFET differential amplifiers are used in integrated circuits, such as operational amplifiers, they provide a high input impedance for the input terminals. A properly designed differential amplifier with its current-mirror biasing stages is made from matched-pair devices to minimize imbalances from one side of the differential amplifier to the other. In this lab, you will design a differential amplifier by first verifying its operation in PSPICE, then building and testing your circuit stage by stage. In your lab kit, you will find one or more CD4007 integrated circuits. (The letter prefix may vary; it's the number 4007 that matters.) This IC contains a number of NMOS and PMOS devices, as shown below. You may assume that all the NMOS transistors are matched to each other (same value of K and threshold voltage VTR), and that all the PMOS devices are similarly matched to each other. Use the devices in this integrated circuit when building your differential amplifier, as requested in Levels 2 and 3. page 2 of 7 BACKGROUND The general topology of a differential amplifier is shown below. Two active devices are connected to a positive voltage supply via passive series elements. -

LTSPICE SOFTWARE Beginner's Guide

L2EEA Electronique 2ème semestre v2017 LTSPICE SOFTWARE Beginner’s guide Preliminary calculations must be done before the practical session Aims: • Perform a harmonic study with LTSPICE software • Know how to plot a Bode plot with LTSPICE The time for this initiation must not exceed 45 minutes. LTSPICE is a freeware generally used for the modelling or analog electronic circuits. It is distributed by LinearTechnology © and can be freely downloaded for windows OS (link: http://www.linear.com/designtools/software). Two kinds of studies can be done with LTSPICE. Two kinds of studies can be performed for an electronic circuit by using LTSPICE: - Harmonic study , in the frequency space - Transient analysis, in the time space The software can also be used for parametric study by varying the numerical value of a component of the circuit (resistance, DC supply, capacitor etc..). For all the cases the modelling of an electronic circuit should be done following these three steps: 1st step: Circuit diagram realization 2nd step: definition of simulation parameters (harmonic or transient study) and use (or not) of a parametric study. 3rd step: Run the simulation and visualization and analysis of the results. 1. Frequency behavior of a passive RC circuit Becoming familiar with the software by studying the frequency behavior of an RC circuit. The very first step is to create a new project with the software and to save it. For this, you have to click on the LTSPICE icon (on the desktop). Then, click on “File Menu” and on “New schematic”. Save your project in a folder named “your name” on the desktop by using the “save as” command. -

Designing Digital Circuits a Modern Approach

Designing Digital Circuits a modern approach Jonathan Turner 2 Contents I First Half 5 1 Introduction to Designing Digital Circuits 7 1.1 Getting Started . .7 1.2 Gates and Flip Flops . .9 1.3 How are Digital Circuits Designed? . 10 1.4 Programmable Processors . 12 1.5 Prototyping Digital Circuits . 15 2 First Steps 17 2.1 A Simple Binary Calculator . 17 2.2 Representing Numbers in Digital Circuits . 21 2.3 Logic Equations and Circuits . 24 3 Designing Combinational Circuits With VHDL 33 3.1 The entity and architecture . 34 3.2 Signal Assignments . 39 3.3 Processes and if-then-else . 43 4 Computer-Aided Design 51 4.1 Overview of CAD Design Flow . 51 4.2 Starting a New Project . 54 4.3 Simulating a Circuit Module . 61 4.4 Preparing to Test on a Prototype Board . 66 4.5 Simulating the Prototype Circuit . 69 3 4 CONTENTS 4.6 Testing the Prototype Circuit . 70 5 More VHDL Language Features 77 5.1 Symbolic constants . 78 5.2 For and case statements . 81 5.3 Synchronous and Asynchronous Assignments . 86 5.4 Structural VHDL . 89 6 Building Blocks of Digital Circuits 93 6.1 Logic Gates as Electronic Components . 93 6.2 Storage Elements . 98 6.3 Larger Building Blocks . 100 6.4 Lookup Tables and FPGAs . 105 7 Sequential Circuits 109 7.1 A Fair Arbiter Circuit . 110 7.2 Garage Door Opener . 118 8 State Machines with Data 127 8.1 Pulse Counter . 127 8.2 Debouncer . 134 8.3 Knob Interface . 137 8.4 Two Speed Garage Door Opener . -

Lsk389 Application Note Dual Monolithic Jfet for Ultra-Low Noise Applications

Over 30 Years of Quality Through Innovation LSK389 APPLICATION NOTE DUAL MONOLITHIC JFET FOR ULTRA-LOW NOISE APPLICATIONS By: Bob Cordell 01/21/2020 REV. A3 Linear Integrated Systems • 4042 Clipper Court • Fremont, CA 94538 • Tel: 510 490-9160 • Fax: 510 353-0261 • Email: [email protected] LINEAR SYSTEMS LSK389 DUAL MONOLITHIC JFET FOR ULTRA-LOW NOISE APPLICATIONS Features Applications ▪ Low Wideband Noise ▪ Low Noise Amplifiers ▪ Low 1/f Noise ▪ Differential Amplifiers ▪ High Transconductance ▪ High Input Impedance Amplifiers ▪ Well-Matched Threshold Voltages ▪ Phono and Other Audio Preamps ▪ High gm/Capacitance Ratio ▪ Condenser Microphone Preamps ▪ Industry's First 100% Noise-Tested JFET ▪ Electrometers ▪ Piezoelectric Sensor Preamps ▪ Front-end for Low-Noise Op Amps Introduction The LSK389 is the industry’s lowest noise Dual N-Channel JFET, 100% tested, guaranteed to meet 1/f and broadband noise specifications, while eliminating burst (RTN or popcorn) noise entirely. The product displays high transconductance and very good matching. It is the JFET of choice for low noise applications, especially those requiring a differential amplifier input stage. LSK389 Key Specifications ▪ 1.3 nV/√Hz input noise at 1 kHz, ID = 2 mA ▪ 1.5 nV/√Hz at 10 Hz, ID = 2 mA ▪ 14 mS transconductance at ID = 2 mA ▪ Improved DC offset ±15 mV max. ▪ CISS = 25 pF typ. ▪ CRSS = 5.5 pF typ. ▪ Breakdown voltage = 40 V min. ▪ 4 grades of IDSS available (A, B, C, D) N-Channel JFET Basics The simplified equation below describes the DC operation of a JFET [1]. The term Vt is the threshold voltage. The term is the transconductance coefficient of the JFET (not to be confused with BJT current gain). -

Fully Differential Op Amps Made Easy

Application Report SLOA099 - May 2002 Fully Differential Op Amps Made Easy Bruce Carter High Performance Linear ABSTRACT Fully differential op amps may be unfamiliar to some designers. This application report gives designers the essential information to get a fully differential design up and running. Contents 1 Introduction . 2 2 What Does Fully Differential Mean?. 2 3 How Is the Second Output Used?. 3 3.1 Differential Gain Stages. 3 3.2 Single-Ended to Differential Conversion. 4 3.3 Working With Terminated Inputs. 5 4 A New Function . 7 5 Conclusions . 8 6 References . 9 List of Figures 1 Single-Ended Op Amp Schematic Symbol. 2 2 Fully Differential Op Amp Schematic Symbol. 2 3 Closing the Loop on a Single-Ended Op Amp. 3 4 Closing the Loop on a Fully Differential Op Amp. 3 5 Single Ended to Differential Conversion. 4 6 Relationship Between Vin, Vout+, and Vout– . 5 7 Fully Differential Amplifier Component Calculator. 6 8 Using a Fully Differential Op Amp to Drive an ADC. 7 9 Effect of Vocm on Vout+ and Vout– . 8 1 SLOA099 1 Introduction Fully differential op amps may be intimidating to some designers, But op amps began as fully differential components over 50 years ago. Techniques about how to use the fully differential versions have been almost lost over the decades. However, today’s fully differential op amps offer performance advantages unheard of in those first units. This report does not attempt a detailed analysis of op amp theory; reference 1 covers theory well. Instead, this report presents just the facts a designer needs to get started, and some resources for further design assistance.