Lecture 12: MOS Transistor Models

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

What Is a Neutral Earthing Resistor?

Fact Sheet What is a Neutral Earthing Resistor? The earthing system plays a very important role in an electrical network. For network operators and end users, avoiding damage to equipment, providing a safe operating environment for personnel and continuity of supply are major drivers behind implementing reliable fault mitigation schemes. What is a Neutral Earthing Resistor? A widely utilised approach to managing fault currents is the installation of neutral earthing resistors (NERs). NERs, sometimes called Neutral Grounding Resistors, are used in an AC distribution networks to limit transient overvoltages that flow through the neutral point of a transformer or generator to a safe value during a fault event. Generally connected between ground and neutral of transformers, NERs reduce the fault currents to a maximum pre-determined value that avoids a network shutdown and damage to equipment, yet allows sufficient flow of fault current to activate protection devices to locate and clear the fault. NERs must absorb and dissipate a huge amount of energy for the duration of the fault event without exceeding temperature limitations as defined in IEEE32 standards. Therefore the design and selection of an NER is highly important to ensure equipment and personnel safety as well as continuity of supply. Power Transformer Motor Supply NER Fault Current Neutral Earthin Resistor Nov 2015 Page 1 Fact Sheet The importance of neutral grounding Fault current and transient over-voltage events can be costly in terms of network availability, equipment costs and compromised safety. Interruption of electricity supply, considerable damage to equipment at the fault point, premature ageing of equipment at other points on the system and a heightened safety risk to personnel are all possible consequences of fault situations. -

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

Basic DC Motor Circuits

Basic DC Motor Circuits Living with the Lab Gerald Recktenwald Portland State University [email protected] DC Motor Learning Objectives • Explain the role of a snubber diode • Describe how PWM controls DC motor speed • Implement a transistor circuit and Arduino program for PWM control of the DC motor • Use a potentiometer as input to a program that controls fan speed LWTL: DC Motor 2 What is a snubber diode and why should I care? Simplest DC Motor Circuit Connect the motor to a DC power supply Switch open Switch closed +5V +5V I LWTL: DC Motor 4 Current continues after switch is opened Opening the switch does not immediately stop current in the motor windings. +5V – Inductive behavior of the I motor causes current to + continue to flow when the switch is opened suddenly. Charge builds up on what was the negative terminal of the motor. LWTL: DC Motor 5 Reverse current Charge build-up can cause damage +5V Reverse current surge – through the voltage supply I + Arc across the switch and discharge to ground LWTL: DC Motor 6 Motor Model Simple model of a DC motor: ❖ Windings have inductance and resistance ❖ Inductor stores electrical energy in the windings ❖ We need to provide a way to safely dissipate electrical energy when the switch is opened +5V +5V I LWTL: DC Motor 7 Flyback diode or snubber diode Adding a diode in parallel with the motor provides a path for dissipation of stored energy when the switch is opened +5V – The flyback diode allows charge to dissipate + without arcing across the switch, or without flowing back to ground through the +5V voltage supply. -

Resistors, Diodes, Transistors, and the Semiconductor Value of a Resistor

Resistors, Diodes, Transistors, and the Semiconductor Value of a Resistor Most resistors look like the following: A Four-Band Resistor As you can see, there are four color-coded bands on the resistor. The value of the resistor is encoded into them. We will follow the procedure below to decode this value. • When determining the value of a resistor, orient it so the gold or silver band is on the right, as shown above. • You can now decode what resistance value the above resistor has by using the table on the following page. • We start on the left with the first band, which is BLUE in this case. So the first digit of the resistor value is 6 as indicated in the table. • Then we move to the next band to the right, which is GREEN in this case. So the second digit of the resistor value is 5 as indicated in the table. • The next band to the right, the third one, is RED. This is the multiplier of the resistor value, which is 100 as indicated in the table. • Finally, the last band on the right is the GOLD band. This is the tolerance of the resistor value, which is 5%. The fourth band always indicates the tolerance of the resistor. • We now put the first digit and the second digit next to each other to create a value. In this case, it’s 65. 6 next to 5 is 65. • Then we multiply that by the multiplier, which is 100. 65 x 100 = 6,500. • And the last band tells us that there is a 5% tolerance on the total of 6500. -

Pentodes Connected As Triodes

Pentodes connected as Triodes by Tom Schlangen Pentodes connected as Triodes About the author Tom Schlangen Born 1962 in Cologne / Germany Studied mechanical engineering at RWTH Aachen / Germany Employments as „safety engineering“ specialist and CIO / IT-head in middle-sized companies, now owning and running an IT- consultant business aimed at middle-sized companies Hobby: Electron valve technology in audio Private homepage: www.tubes.mynetcologne.de Private email address: [email protected] Tom Schlangen – ETF 06 2 Pentodes connected as Triodes Reasons for connecting and using pentodes as triodes Why using pentodes as triodes at all? many pentodes, especially small signal radio/TV ones, are still available from huge stock cheap as dirt, because nobody cares about them (especially “TV”-valves), some of them, connected as triodes, can rival even the best real triodes for linearity, some of them, connected as triodes, show interesting characteristics regarding µ, gm and anode resistance, that have no expression among readily available “real” triodes, because it is fun to try and find out. Tom Schlangen – ETF 06 3 Pentodes connected as Triodes How to make a triode out of a tetrode or pentode again? Or, what to do with the “superfluous” grids? All additional grids serve a certain purpose and function – they were added to a basic triode system to improve the system behaviour in certain ways, for example efficiency. We must “disable” the functions of those additional grids in a defined and controlled manner to regain triode characteristics. Just letting them “dangle in vacuum unconnected” will not work – they would charge up uncontrolled in the electron stream, leading to unpredictable behaviour. -

Eimac Care and Feeding of Tubes Part 3

SECTION 3 ELECTRICAL DESIGN CONSIDERATIONS 3.1 CLASS OF OPERATION Most power grid tubes used in AF or RF amplifiers can be operated over a wide range of grid bias voltage (or in the case of grounded grid configuration, cathode bias voltage) as determined by specific performance requirements such as gain, linearity and efficiency. Changes in the bias voltage will vary the conduction angle (that being the portion of the 360° cycle of varying anode voltage during which anode current flows.) A useful system has been developed that identifies several common conditions of bias voltage (and resulting anode current conduction angle). The classifications thus assigned allow one to easily differentiate between the various operating conditions. Class A is generally considered to define a conduction angle of 360°, class B is a conduction angle of 180°, with class C less than 180° conduction angle. Class AB defines operation in the range between 180° and 360° of conduction. This class is further defined by using subscripts 1 and 2. Class AB1 has no grid current flow and class AB2 has some grid current flow during the anode conduction angle. Example Class AB2 operation - denotes an anode current conduction angle of 180° to 360° degrees and that grid current is flowing. The class of operation has nothing to do with whether a tube is grid- driven or cathode-driven. The magnitude of the grid bias voltage establishes the class of operation; the amount of drive voltage applied to the tube determines the actual conduction angle. The anode current conduction angle will determine to a great extent the overall anode efficiency. -

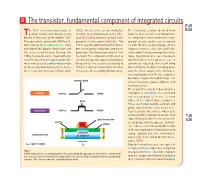

The Transistor, Fundamental Component of Integrated Circuits

D The transistor, fundamental component of integrated circuits he first transistor was made in (SiO2), which serves as an insulator. The transistor, a name derived from Tgermanium by John Bardeen and In 1958, Jack Kilby invented the inte- transfer and resistor, is a fundamen- Walter H. Brattain, in December 1947. grated circuit by manufacturing 5 com- tal component of microelectronic inte- The year after, along with William B. ponents on the same substrate. The grated circuits, and is set to remain Shockley at Bell Laboratories, they 1970s saw the advent of the first micro- so with the necessary changes at the developed the bipolar transistor and processor, produced by Intel and incor- nanoelectronics scale: also well-sui- the associated theory. During the porating 2,250 transistors, and the first ted to amplification, among other func- 1950s, transistors were made with sili- memory. The complexity of integrated tions, it performs one essential basic con (Si), which to this day remains the circuits has grown exponentially (dou- function which is to open or close a most widely-used semiconductor due bling every 2 to 3 years according to current as required, like a switching to the exceptional quality of the inter- “Moore's law”) as transistors continue device (Figure). Its basic working prin- face created by silicon and silicon oxide to become increasingly miniaturized. ciple therefore applies directly to pro- cessing binary code (0, the current is blocked, 1 it goes through) in logic cir- control gate cuits (inverters, gates, adders, and memory cells). The transistor, which is based on the switch source drain transport of electrons in a solid and not in a vacuum, as in the electron gate tubes of the old triodes, comprises three electrodes (anode, cathode and gate), two of which serve as an elec- transistor source drain tron reservoir: the source, which acts as the emitter filament of an electron gate insulator tube, the drain, which acts as the col- source lector plate, with the gate as “control- gate drain ler”. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Using Embedded Resistor Emulation and Trimming to Demonstrate Measurement Methods and Associated Engineering Model Development*

IJEE 1830 Int. J. Engng Ed. Vol. 22, No. 1, pp. 000±000, 2006 0949-149X/91 $3.00+0.00 Printed in Great Britain. # 2006 TEMPUS Publications. Using Embedded Resistor Emulation and Trimming to Demonstrate Measurement Methods and Associated Engineering Model Development* PHILLIP A.M.SANDBORN AND PETER A.SANDBORN CALCE Electronic Products and Systems Center, Department of Mechanical Engineering, University of Maryland, College Park, MD, USA.E-mail: [email protected] Embedded resistors are planar resistors that are fabricated inside printed circuit boards and used as an alternative to discrete resistor components that are mounted on the surface of the boards.The successful use of embedded resistors in many applications requires that the resistors be trimmed to required design values prior to lamination into printed circuit boards.This paper describes a simple emulation approach utilizing conductive paper that can be used to characterize embedded resistor operation and experimentally optimize resistor trimming patterns.We also describe a hierarchy of simple modeling approaches appropriate to both college engineering students and pre-college students that can be verified with the experimental results, and used to extend the experimental trimming analysis.The methodology described in this paper is a simple and effective approach for demonstrating a combination of measurement methods, uncertainty analysis, and associated engineering model development. Keywords: embedded resistors; embedded passives; trimming INTRODUCTION process that starts with a layer pair that is pre- coated with resistive material that is selectively EMBEDDING PASSIVE components (capaci- removed to create the resistors.The layer contain- tors, resistors, and possibly inductors) within ing the resistor is laminated together with other printed circuit boards is one of a series of technol- layers to make the finished printed circuit board. -

Resistor Selection Application Notes Resistor Facts and Factors

Resistor Selection Application Notes RESISTOR FACTS AND FACTORS A resistor is a device connected into an electrical circuit to resistor to withstand, without deterioration, the temperature introduce a specified resistance. The resistance is measured in attained, limits the operating temperature which can be permit- ohms. As stated by Ohm’s Law, the current through the resistor ted. Resistors are rated to dissipate a given wattage without will be directly proportional to the voltage across it and inverse- exceeding a specified standard “hot spot” temperature and the ly proportional to the resistance. physical size is made large enough to accomplish this. The passage of current through the resistance produces Deviations from the standard conditions (“Free Air Watt heat. The heat produces a rise in temperature of the resis- Rating”) affect the temperature rise and therefore affect the tor above the ambient temperature. The physical ability of the wattage at which the resistor may be used in a specific applica- tion. SELECTION REQUIRES 3 STEPS Simple short-cut graphs and charts in this catalog permit rapid 1.(a) Determine the Resistance. determination of electrical parameters. Calculation of each (b) Determine the Watts to be dissipated by the Resistor. parameter is also explained. To select a resistor for a specific application, the following steps are recommended: 2.Determine the proper “Watt Size” (physical size) as controlled by watts, volts, permissible temperatures, mounting conditions and circuit conditions. 3.Choose the most suitable kind of unit, including type, terminals and mounting. STEP 1 DETERMINE RESISTANCE AND WATTS Ohm’s Law Why Watts Must Be Accurately Known 400 Stated non-technically, any change in V V (a) R = I or I = R or V = IR current or voltage produces a much larger change in the wattage (heat to be Ohm’s Law, shown in formula form dissipated by the resistor). -

Power MOSFET Basics by Vrej Barkhordarian, International Rectifier, El Segundo, Ca

Power MOSFET Basics By Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Breakdown Voltage......................................... 5 On-resistance.................................................. 6 Transconductance............................................ 6 Threshold Voltage........................................... 7 Diode Forward Voltage.................................. 7 Power Dissipation........................................... 7 Dynamic Characteristics................................ 8 Gate Charge.................................................... 10 dV/dt Capability............................................... 11 www.irf.com Power MOSFET Basics Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Discrete power MOSFETs Source Field Gate Gate Drain employ semiconductor Contact Oxide Oxide Metallization Contact processing techniques that are similar to those of today's VLSI circuits, although the device geometry, voltage and current n* Drain levels are significantly different n* Source t from the design used in VLSI ox devices. The metal oxide semiconductor field effect p-Substrate transistor (MOSFET) is based on the original field-effect Channel l transistor introduced in the 70s. Figure 1 shows the device schematic, transfer (a) characteristics and device symbol for a MOSFET. The ID invention of the power MOSFET was partly driven by the limitations of bipolar power junction transistors (BJTs) which, until recently, was the device of choice in power electronics applications. 0 0 V V Although it is not possible to T GS define absolutely the operating (b) boundaries of a power device, we will loosely refer to the I power device as any device D that can switch at least 1A. D The bipolar power transistor is a current controlled device. A SB (Channel or Substrate) large base drive current as G high as one-fifth of the collector current is required to S keep the device in the ON (c) state. Figure 1. Power MOSFET (a) Schematic, (b) Transfer Characteristics, (c) Also, higher reverse base drive Device Symbol.