Silicon Bicmos the Optimal Technology for RF Power Peter Gammel, Ph.D

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Hybrid Memristor–CMOS Implementation of Combinational Logic Based on X-MRL †

electronics Article Hybrid Memristor–CMOS Implementation of Combinational Logic Based on X-MRL † Khaled Alhaj Ali 1,* , Mostafa Rizk 1,2,3 , Amer Baghdadi 1 , Jean-Philippe Diguet 4 and Jalal Jomaah 3 1 IMT Atlantique, Lab-STICC CNRS, UMR, 29238 Brest, France; [email protected] (M.R.); [email protected] (A.B.) 2 Lebanese International University, School of Engineering, Block F 146404 Mazraa, Beirut 146404, Lebanon 3 Faculty of Sciences, Lebanese University, Beirut 6573, Lebanon; [email protected] 4 IRL CROSSING CNRS, Adelaide 5005, Australia; [email protected] * Correspondence: [email protected] † This paper is an extended version of our paper published in IEEE International Conference on Electronics, Circuits and Systems (ICECS) , 27–29 November 2019, as Ali, K.A.; Rizk, M.; Baghdadi, A.; Diguet, J.P.; Jomaah, J. “MRL Crossbar-Based Full Adder Design”. Abstract: A great deal of effort has recently been devoted to extending the usage of memristor technology from memory to computing. Memristor-based logic design is an emerging concept that targets efficient computing systems. Several logic families have evolved, each with different attributes. Memristor Ratioed Logic (MRL) has been recently introduced as a hybrid memristor–CMOS logic family. MRL requires an efficient design strategy that takes into consideration the implementation phase. This paper presents a novel MRL-based crossbar design: X-MRL. The proposed structure combines the density and scalability attributes of memristive crossbar arrays and the opportunity of their implementation at the top of CMOS layer. The evaluation of the proposed approach is performed through the design of an X-MRL-based full adder. -

Three-Dimensional Integrated Circuit Design: EDA, Design And

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to http://www.springer.com/series/7236 Yuan Xie · Jason Cong · Sachin Sapatnekar Editors Three-Dimensional Integrated Circuit Design EDA, Design and Microarchitectures 123 Editors Yuan Xie Jason Cong Department of Computer Science and Department of Computer Science Engineering University of California, Los Angeles Pennsylvania State University [email protected] [email protected] Sachin Sapatnekar Department of Electrical and Computer Engineering University of Minnesota [email protected] ISBN 978-1-4419-0783-7 e-ISBN 978-1-4419-0784-4 DOI 10.1007/978-1-4419-0784-4 Springer New York Dordrecht Heidelberg London Library of Congress Control Number: 2009939282 © Springer Science+Business Media, LLC 2010 All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights. Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) Foreword We live in a time of great change. -

A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes

382 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 65, NO. 2, FEBRUARY 2018 A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes for Communication—Part II: Device and VLSI Integration Challenges for Low-Dimensional Structures Hilal Cansizoglu , Member, IEEE, Aly F. Elrefaie, Fellow, IEEE, Cesar Bartolo-Perez, Toshishige Yamada, Senior Member, IEEE, Yang Gao, Ahmed S. Mayet, Mehmet F. Cansizoglu, Ekaterina Ponizovskaya Devine, Shih-Yuan Wang, Life Fellow, IEEE,and M. Saif Islam, Senior Member, IEEE (Invited Review Paper) Abstract— The ability to monolithically integrate high- Index Terms— CMOS integration, extended-reach links, speed photodetectors (PDs) with silicon (Si) can contribute high speed, high-efficiency photodetectors (PDs), high- to drastic reduction in cost. Such PDs are envisioned to performance computing, light detection and ranging, micro- be integral parts of high-speed optical interconnects in /nanostructures, single-photon detection, surface states, the future intrachip, chip-to-chip, board-to-board, rack-to- very-large-scale integration (VLSI) and ultralarge-scale inte- rack, and intra-/interdata center links. Si-based PDs are of gration (ULSI). special interest since they present the potential for mono- lithic integration with CMOS and BiCMOS very-large-scale integration and ultralarge-scale integration electronics. I. INTRODUCTION In the second part of this review, we present the efforts HE rise of distributed computing, cloud storage, social pursued by the researchers in engineering and integrating Si, SiGe alloys, and Ge PDs to CMOS and BiCMOS electron- Tmedia, and affordable hand-held devices currently allow ics and compare the performance of recently demonstrated extreme ease of transferring a plethora of data including CMOS-compatible ultrafast surface-illuminated Si PD with videos, pictures, and texts, all over the world. -

By Erika Azabache Villar a Thesis Submitted in Partial Fulfillment of The

SMALLER/FASTER DELTA-SIGMA DIGITAL PIXEL SENSORS by Erika Azabache Villar A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Integrated Circuits and Systems Department of Electrical and Computer Engineering University of Alberta c Erika Azabache Villar, 2016 Abstract A digital pixel sensor (DPS) array is an image sensor where each pixel has an analog-to-digital converter (ADC). Recently, a logarithmic delta-sigma (ΔΣ) DPS array, using first-order ΔΣ ADCs, achieved wide dynamic range and high signal-to-noise-and-distortion ratios at video rates, requirements that are difficult to meet using conventional image sensors. However, this state-of-the-art ΔΣ DPS design is either too large for some applications, such as optical imag- ing, or too slow for others, such as gamma imaging. Consequently, this master’s thesis investi- gates smaller or faster ΔΣ DPS designs, relative to the state of the art. All designs are validated through simulations. Commercial image sensors, for optical and gamma imaging, are used as targeted baselines to establish competitive specifications. To achieve a smaller pixel, process scaling is exploited. Three logarithmic ΔΣ DPS designs are presented for 180, 130, and 65 nm fabrication processes, demonstrating a path to competitiveness for the optical imaging market. Decimator and readout circuits are improved, compared to previous work, while reducing area, and capacitors in the modulator prove to be the limiting factor in deep-submicron processes. Area trends are used to construct a roadmap to even smaller pixels. To achieve a faster pixel, a higher-order ΔΣ architecture is exploited. -

An Area Efficient Sub-Threshold Voltage Level Shifter Using a Modified Wilson Current Mirror for Low Power Applications

An Area Efficient Sub-threshold Voltage Level Shifter using a Modified Wilson Current Mirror for Low Power Applications Biswarup Mukherjee & Aniruddha Ghosal Published online: 22 May 2019. Submit your article to this journal Article views: 12 View Crossmark data An Area Efficient Sub-threshold Voltage Level Shifter using a Modified Wilson Current Mirror for Low Power Applications Biswarup Mukherjee1 and Aniruddha Ghosal2 1Neotia Institute of Technology, Management and Science, Jhinga, Diamond Harbour Road, 24Pgs. (S), West Bengal, India; 2Institute of Radio Physics and Electronics, University of Calcutta, West Bengal, India ABSTRACT KEYWORDS In the present communication, a new technique has been introduced for implementing low-power Current mirror; CAD area efficient sub-threshold voltage level shifter (LS) circuit. The proposed LS circuit consists of only simulation; Level shifter (LS); nine transistors and can operate up to 100 MHz of input frequency successfully. The proposed LS Low power; Sub-threshold is made of single threshold voltage transistors which show least complexity in fabrication and bet- operation; Typical transistor (TT) ter performance in terms of delay analysis and power consumption compared to other available designs. CAD tool-based simulation at TSMC 180 nm technology and comparison between the pro- posed design and other available designs show that the proposed design performs better than other state-of-the-art designs for a similar range of voltage conversion with the most area efficiency. 1. INTRODUCTION are used to reduce the circuit activity or the capacitance value in order to reduce the switching power consump- With the increasing demand of portable devices in elec- tion. -

Overview of CMOS Sensors for Future Tracking Detectors

instruments Review Overview of CMOS Sensors for Future Tracking Detectors Ricardo Marco-Hernández Instituto de Física Corpuscular (CSIC-UV), 46980 Valencia, Spain; rmarco@ific.uv.es Received: 23 October 2020; Accepted: 27 November 2020; Published: 30 November 2020 Abstract: Depleted Complementary Metal-Oxide-Semiconductor (CMOS) sensors are emerging as one of the main candidate technologies for future tracking detectors in high luminosity colliders. Their capability of integrating the sensing diode into the CMOS wafer hosting the front-end electronics allows for reduced noise and higher signal sensitivity, due to the direct collection of the sensor signal by the readout electronics. They are suitable for high radiation environments due to the possibility of applying high depletion voltage and the availability of relatively high resistivity substrates. The use of a CMOS commercial fabrication process leads to their cost reduction and allows faster construction of large area detectors. In this contribution, a general perspective of the state of the art of CMOS detectors for High Energy Physics experiments is given. The main developments carried out with regard to these devices in the framework of the CERN RD50 collaboration are summarized. Keywords: DMAPS; CMOS; radiation sensors; electronics 1. Introduction Current large pixel detectors in High Energy Physics, such as the ones which will be part of the A Toroidal LHC (Large Hadron Collider) ApparatuS (ATLAS) Tracker Detector [1] or the Compact Muon Solenoid (CMS) Tracker Detector [2] upgrades for the High-Luminosity Large Hadron Collider (HL-LHC), mostly follow a hybrid approach. In a hybrid pixel detector the sensor and the readout electronics are independent devices connected by means of bump-bonding, as can be seen in Figure1. -

LDMOS for Improved Performance

> Submitted to IEEE Transactions on Electron Devices < Final MS # 8011B 1 Extended-p+ Stepped Gate (ESG) LDMOS for Improved Performance M. Jagadesh Kumar, Senior Member, IEEE and Radhakrishnan Sithanandam Abstract—In this paper, we propose a new Extended-p+ Stepped Gate (ESG) thin film SOI LDMOS with an extended-p+ region beneath the source and a stepped gate structure in the drift region of the LDMOS. The hole current generated due to impact ionization is now collected from an n+p+ junction instead of an n+p junction thus delaying the parasitic BJT action. The stepped gate structure enhances RESURF in the drift region, and minimizes the gate-drain capacitance. Based on two- dimensional simulation results, we show that the ESG LDMOS exhibits approximately 63% improvement in breakdown voltage, 38% improvement in on-resistance, 11% improvement in peak transconductance, 18% improvement in switching speed and 63% reduction in gate-drain charge density compared with the conventional LDMOS with a field plate. Index Terms—LDMOS, silicon on insulator (SOI), breakdown voltage, transconductance, on- resistance, gate charge I. INTRODUCTION ATERALLY double diffused metal oxide semiconductor (LDMOS) on SOI substrate is a promising Ltechnology for RF power amplifiers and wireless applications [1-5]. In the recent past, developing high voltage thin film LDMOS has gained importance due to the possibility of its integration with low power CMOS devices and heterogeneous microsystems [6]. But realization of high voltage devices in thin film SOI is challenging because floating body effects affect the breakdown characteristics. Often, body contacts are included to remove the floating body effects in RF devices [7]. -

A Area VLSI Design (SCL)

A Area VLSI Design (SCL) A1 Sub Area ASIC Design (SCL) A1.1 Design of Instrumentation Amplifier A High-Precision Instrumentation Amplifier with large CMRR is required for the Sensor Signal conditioning applications. Instrumentation amplifier is a versatile device used for amplification of small differential mode signals while rejecting large common mode signal at the same time. In a typical signal conditioning chain, the output of the sensor goes to the instrumentation amplifier. The instrumentation amplifier amplifies the small output signal of the sensor and gives it to the ADC for digitization. Target Specification: • Supply Voltage: 3.3V • Temperature Range: -40 degC to 125 degC • Programmable Gain: 1 to 1000 • Low noise < 0.3µV p-p at 0.1 Hz to 10 Hz • Low non linearity < 20ppm (Gain = 1) • High CMRR (Common Mode Rejection Ratio) > 90dB (Gain=1) • Low offset voltage < 100µV • 3 dB Bandwidth: 1MHz (at Gain = 1) The design of the proposed Instrumentation Amplifier is to be carried out in SCL 180 nm process. A1.2 Design of a Current Feedback Amplifier (CFA) Opamps come in two types: the voltage-feedback amplifier (VFA), for which the input error is a voltage; and the current-feedback amplifier (CFA), for which the input error is a current. The CFA noninverting amplifier is relatively free from a gain-bandwidth trade-off. Additional advantage of CFAs compared to VFAs is the absence of slew-rate limiting. CFA is primarily used where both high speed and low distortion signal processing is required. CFAs are mainly used in broadcast video systems, radar systems , IF and RF stages and other high speed circuits. -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

Vlsi Design Lecture Notes B.Tech (Iv Year – I Sem) (2018-19)

VLSI DESIGN LECTURE NOTES B.TECH (IV YEAR – I SEM) (2018-19) Prepared by Dr. V.M. Senthilkumar, Professor/ECE & Ms.M.Anusha, AP/ECE Department of Electronics and Communication Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India Unit -1 IC Technologies, MOS & Bi CMOS Circuits Unit -1 IC Technologies, MOS & Bi CMOS Circuits UNIT-I IC Technologies Introduction Basic Electrical Properties of MOS and BiCMOS Circuits MOS I - V relationships DS DS PMOS MOS transistor Threshold Voltage - VT figure of NMOS merit-ω0 Transconductance-g , g ; CMOS m ds Pass transistor & NMOS Inverter, Various BiCMOS pull ups, CMOS Inverter Technologies analysis and design Bi-CMOS Inverters Unit -1 IC Technologies, MOS & Bi CMOS Circuits INTRODUCTION TO IC TECHNOLOGY The development of electronics endless with invention of vaccum tubes and associated electronic circuits. This activity termed as vaccum tube electronics, afterward the evolution of solid state devices and consequent development of integrated circuits are responsible for the present status of communication, computing and instrumentation. • The first vaccum tube diode was invented by john ambrase Fleming in 1904. • The vaccum triode was invented by lee de forest in 1906. Early developments of the Integrated Circuit (IC) go back to 1949. German engineer Werner Jacobi filed a patent for an IC like semiconductor amplifying device showing five transistors on a common substrate in a 2-stage amplifier arrangement. -

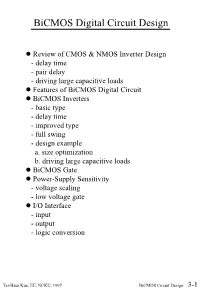

Bicmos Digital Circuit Design

BiCMOS Digital Circuit Design Review of CMOS & NMOS Inverter Design - delay time - pair delay - driving large capacitive loads Features of BiCMOS Digital Circuit BiCMOS Inverters -basic type - delay time - improved type - full swing - design example a. size optimization b. driving large capacitive loads BiCMOS Gate Power-Supply Sensitivity - voltage scaling - low voltage gate I/O Interface - input - output - logic conversion Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-1 NMOS DIGITAL CIRCUITS Static inverters Load Vout ==> V in driver A B C IDS VGS=V(1) C B A VDS (driver) VDD Vth VDD D: in in Vout VGS=V(1) VGS=V(0) V(0) V(0) V(1) V(0) V(1) Vin ― Static power dissipation during Vout=V(0) Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-2 Switching Characteristics of CMOS Inverter CMOS inverter VDD VDD T 2 V (t) o t Vin(t) T1 CL +VDD Vin(t) 0 t +VDD 0.9VDD 0.1VDD t td tf tr Trajectory of n-transistor operating point during switching in CMOS inverter Input transition : X1 X2 Output transition: X2 X3 Vds=Vgs-Vt UNSATURATED SATURATED STATE STATE X2 Vgs=VDD Ids OPERATING POINT AFTER COMPLETION OF SWITCHING INITIAL OPERATING POINT X3 X1 0 VDD Vo(t) Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-3 Rise Time and Fall Time of CMOS Inverter > Equivalent Circuit V DD VDD > Fall p-DEVICE p-DEVICE t=0 t=0 I Vin ↑ c Ic Idsn R V c C o Vo n-DEVICE L n-DEVICE CL Vo ↓ SATURATION: VVoD≥ D− Vtn 0 < VV≤ − V (a) SATURATION: 0 DD tn > Rise VDD VDD p-DEVICE p-DEVICE Idsp Rc Vin ↓ I Ic Vo ↑ t=0 c Vo Vo n-DEVICE CL n-DEVICE -

EP Activity Report 2015

EUROPRACTICE IC SERVICE THE RIGHT COCKTAIL OF ASIC SERVICES EUROPRACTICE IC SERVICE OFFERS YOU A PROVEN ROUTE TO ASICS THAT FEATURES: · .QYEQUV#5+%RTQVQV[RKPI · (NGZKDNGCEEGUUVQUKNKEQPECRCEKV[HQTUOCNNCPFOGFKWOXQNWOGRTQFWEVKQPSWCPVKVKGU · 2CTVPGTUJKRUYKVJNGCFKPIYQTNFENCUUHQWPFTKGUCUUGODN[CPFVGUVJQWUGU · 9KFGEJQKEGQH+%VGEJPQNQIKGU · &KUVTKDWVKQPCPFHWNNUWRRQTVQHJKIJSWCNKV[EGNNNKDTCTKGUCPFFGUKIPMKVUHQTVJGOQUVRQRWNCT%#&VQQNU · 46.VQ.C[QWVUGTXKEGHQTFGGRUWDOKETQPVGEJPQNQIKGU · (TQPVGPF#5+%FGUKIPVJTQWIJ#NNKCPEG2CTVPGTU +PFWUVT[KUTCRKFN[FKUEQXGTKPIVJGDGPG«VUQHWUKPIVJG'74124#%6+%'+%UGTXKEGVQJGNRDTKPIPGYRTQFWEVFGUKIPUVQOCTMGV SWKEMN[CPFEQUVGHHGEVKXGN[6JG'74124#%6+%'#5+%TQWVGUWRRQTVUGURGEKCNN[VJQUGEQORCPKGUYJQFQP°VPGGFCNYC[UVJG HWNNTCPIGQHUGTXKEGUQTJKIJRTQFWEVKQPXQNWOGU6JQUGEQORCPKGUYKNNICKPHTQOVJG¬GZKDNGCEEGUUVQUKNKEQPRTQVQV[RGCPF RTQFWEVKQPECRCEKV[CVNGCFKPIHQWPFTKGUFGUKIPUGTXKEGUJKIJSWCNKV[UWRRQTVCPFOCPWHCEVWTKPIGZRGTVKUGVJCVKPENWFGU+% OCPWHCEVWTKPIRCEMCIKPICPFVGUV6JKU[QWECPIGVCNNHTQO'74124#%6+%'+%UGTXKEGCUGTXKEGVJCVKUCNTGCF[GUVCDNKUJGF HQT[GCTUKPVJGOCTMGV THE EUROPRACTICE IC SERVICES ARE OFFERED BY THE FOLLOWING CENTERS: · KOGE.GWXGP $GNIKWO · (TCWPJQHGT+PUVKVWVHWGT+PVGITKGTVG5EJCNVWPIGP (TCWPJQHGT++5 'TNCPIGP )GTOCP[ This project has received funding from the European Union’s Seventh Programme for research, technological development and demonstration under grant agreement N° 610018. This funding is exclusively used to support European universities and research laboratories. © imec FOREWORD Dear EUROPRACTICE customers, We are at the start of the