Hybrid Memristor–CMOS Implementation of Combinational Logic Based on X-MRL †

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Memristor-The Future of Artificial Intelligence L.Kavinmathi, C.Gayathri, K.Kumutha Priya

International Journal of Scientific & Engineering Research, Volume 5, Issue 4, April-2014 358 ISSN 2229-5518 Memristor-The Future of Artificial Intelligence L.kavinmathi, C.Gayathri, K.Kumutha priya Abstract- Due to increasing demand on miniaturization and low power consumption, Memristor came into existence. Our design exploration is Reconfigurable Threshold Logic Gates based Programmable Analog Circuits using Memristor. Thus a variety of linearly separable and non- linearly separable logic functions such as AND, OR, NAND, NOR, XOR, XNOR have been realized using Threshold logic gate using Memristor. The functionality can be changed between these operations just by varying the resistance of the Memristor. Based on this Reconfigurable TLG, various Programmable Analog circuits can be built using Memristor. As an example of our approach, we have built Programmable analog Gain amplifier demonstrating Memristor-based programming of Threshold, Gain and Frequency. As our idea consisting of Programmable circuit design, in which low voltages are applied to Memristor during their operation as analog circuit element and high voltages are used to program the Memristor’s states. In these circuits the role of memristor is played by Memristor Emulator developed by us using FPGA. Reconfigurable is the option we are providing with the present system, so that the resistance ranges are varied by preprogram too. Index Terms— Memristor, TLG-threshold logic gates, Programmable Analog Circuits, FPGA-field programmable gate array, MTL- memristor threshold logic, CTL-capacitor Threshold logic, LUT- look up table. —————————— ( —————————— 1 INTRODUCTION CCORDING to Chua’s [founder of Memristor] definition, 9444163588. E-mail: [email protected] the internal state of an ideal Memristor depends on the • L.kavinmathi is currently pursuing bachelors degree program in electronics A and communication engineering in tagore engineering college under Anna integral of the voltage or current over time. -

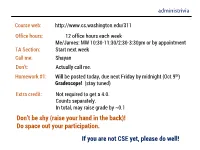

CSE Yet, Please Do Well! Logical Connectives

administrivia Course web: http://www.cs.washington.edu/311 Office hours: 12 office hours each week Me/James: MW 10:30-11:30/2:30-3:30pm or by appointment TA Section: Start next week Call me: Shayan Don’t: Actually call me. Homework #1: Will be posted today, due next Friday by midnight (Oct 9th) Gradescope! (stay tuned) Extra credit: Not required to get a 4.0. Counts separately. In total, may raise grade by ~0.1 Don’t be shy (raise your hand in the back)! Do space out your participation. If you are not CSE yet, please do well! logical connectives p q p q p p T T T T F T F F F T F T F NOT F F F AND p q p q p q p q T T T T T F T F T T F T F T T F T T F F F F F F OR XOR 푝 → 푞 • “If p, then q” is a promise: p q p q F F T • Whenever p is true, then q is true F T T • Ask “has the promise been broken” T F F T T T If it’s raining, then I have my umbrella. related implications • Implication: p q • Converse: q p • Contrapositive: q p • Inverse: p q How do these relate to each other? How to see this? 푝 ↔ 푞 • p iff q • p is equivalent to q • p implies q and q implies p p q p q Let’s think about fruits A fruit is an apple only if it is either red or green and a fruit is not red and green. -

Three-Dimensional Integrated Circuit Design: EDA, Design And

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to http://www.springer.com/series/7236 Yuan Xie · Jason Cong · Sachin Sapatnekar Editors Three-Dimensional Integrated Circuit Design EDA, Design and Microarchitectures 123 Editors Yuan Xie Jason Cong Department of Computer Science and Department of Computer Science Engineering University of California, Los Angeles Pennsylvania State University [email protected] [email protected] Sachin Sapatnekar Department of Electrical and Computer Engineering University of Minnesota [email protected] ISBN 978-1-4419-0783-7 e-ISBN 978-1-4419-0784-4 DOI 10.1007/978-1-4419-0784-4 Springer New York Dordrecht Heidelberg London Library of Congress Control Number: 2009939282 © Springer Science+Business Media, LLC 2010 All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights. Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) Foreword We live in a time of great change. -

The Memristor: Anew Bond Graph Element D

Paper No. n-Aut·N J The Society shall not be responsible for statements or opinions :<;111 pnp~,r~ or, in'Ldisao~slofl at me~,~in~s~f t~~ <~~,~iety, o,~, ot ,.its (I',~l)o'isjons:"or S,ecti ons;) lor- prlrU9d;:)ln tts j:~obllcaJLors. G. F.OSTER The Memristor: ANew Bond Graph Element D. M. AUSLANDER Mechanical Engineering Department. The "mcmris[.or," first deft ned by L. Clma for electrical drwits, 1·$ proposed as a new University of California, Berkeley, bond gra,ph clemel/t, on (1.11- equul footiug with R, L, & C, and having some unique Calif. modelling capubilities for nontinear systems. The Missing Constitutive Relation circuit thcory; howevcr, if wc look beyond the electrical doma.in it is not hard 1.0 find systems whose characteristics are con Ix HIS original lecture notes int.roducing the bond veniently represented by a memristor modcl. graph technique, Paynter drew a 1I1ctrahedron of state," (Fig. I) which sumnHlrir.cd j.he relationship between the sl.ate vl~riables Properties (c, I, p, q) [I, 2].1 There are G binary relationships possible be tween these 4 state variableii, Two of these are definitions: the The constitutive relation for a I-port memristor is a curve in the q-p ph~ne, Fig. 2. [n this context, we do not necessarily in_ displacement., q(t) = q(O) + f(t)clJ, and the qU:l.utit,y pet) = J:' terpret the quant.it,y p(l) = p(O) + ]:' e(t)dt as momentum, magneti(~ p(O) + }:' c(l)dt, which is interpreted ns momentum, flux, or pressure-momentum (2), buti merely as t.he integrated etTol't ("impulse!». -

LDMOS for Improved Performance

> Submitted to IEEE Transactions on Electron Devices < Final MS # 8011B 1 Extended-p+ Stepped Gate (ESG) LDMOS for Improved Performance M. Jagadesh Kumar, Senior Member, IEEE and Radhakrishnan Sithanandam Abstract—In this paper, we propose a new Extended-p+ Stepped Gate (ESG) thin film SOI LDMOS with an extended-p+ region beneath the source and a stepped gate structure in the drift region of the LDMOS. The hole current generated due to impact ionization is now collected from an n+p+ junction instead of an n+p junction thus delaying the parasitic BJT action. The stepped gate structure enhances RESURF in the drift region, and minimizes the gate-drain capacitance. Based on two- dimensional simulation results, we show that the ESG LDMOS exhibits approximately 63% improvement in breakdown voltage, 38% improvement in on-resistance, 11% improvement in peak transconductance, 18% improvement in switching speed and 63% reduction in gate-drain charge density compared with the conventional LDMOS with a field plate. Index Terms—LDMOS, silicon on insulator (SOI), breakdown voltage, transconductance, on- resistance, gate charge I. INTRODUCTION ATERALLY double diffused metal oxide semiconductor (LDMOS) on SOI substrate is a promising Ltechnology for RF power amplifiers and wireless applications [1-5]. In the recent past, developing high voltage thin film LDMOS has gained importance due to the possibility of its integration with low power CMOS devices and heterogeneous microsystems [6]. But realization of high voltage devices in thin film SOI is challenging because floating body effects affect the breakdown characteristics. Often, body contacts are included to remove the floating body effects in RF devices [7]. -

New Approaches for Memristive Logic Computations

Portland State University PDXScholar Dissertations and Theses Dissertations and Theses 6-6-2018 New Approaches for Memristive Logic Computations Muayad Jaafar Aljafar Portland State University Let us know how access to this document benefits ouy . Follow this and additional works at: https://pdxscholar.library.pdx.edu/open_access_etds Part of the Electrical and Computer Engineering Commons Recommended Citation Aljafar, Muayad Jaafar, "New Approaches for Memristive Logic Computations" (2018). Dissertations and Theses. Paper 4372. 10.15760/etd.6256 This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact [email protected]. New Approaches for Memristive Logic Computations by Muayad Jaafar Aljafar A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering Dissertation Committee: Marek A. Perkowski, Chair John M. Acken Xiaoyu Song Steven Bleiler Portland State University 2018 © 2018 Muayad Jaafar Aljafar Abstract Over the past five decades, exponential advances in device integration in microelectronics for memory and computation applications have been observed. These advances are closely related to miniaturization in integrated circuit technologies. However, this miniaturization is reaching the physical limit (i.e., the end of Moore’s Law). This miniaturization is also causing a dramatic problem of heat dissipation in integrated circuits. Additionally, approaching the physical limit of semiconductor devices in fabrication process increases the delay of moving data between computing and memory units hence decreasing the performance. The market requirements for faster computers with lower power consumption can be addressed by new emerging technologies such as memristors. -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

Physical Structure of CMOS Integrated Circuits

Physical Structure of CMOS Integrated Circuits Dae Hyun Kim EECS Washington State University References • John P. Uyemura, “Introduction to VLSI Circuits and Systems,” 2002. – Chapter 3 • Neil H. Weste and David M. Harris, “CMOS VLSI Design: A Circuits and Systems Perspective,” 2011. – Chapter 1 Goal • Understand the physical structure of CMOS integrated circuits (ICs) Logical vs. Physical • Logical structure • Physical structure Source: http://www.vlsi-expert.com/2014/11/cmos-layout-design.html Integrated Circuit Layers • Semiconductor – Transistors (active elements) • Conductor – Metal (interconnect) • Wire • Via • Insulator – Separators Integrated Circuit Layers • Silicon substrate, insulator, and two wires (3D view) Substrate • Side view Metal 1 layer Insulator Substrate • Top view Integrated Circuit Layers • Two metal layers separated by insulator (side view) Metal 2 layer Via 12 (connecting M1 and M2) Insulator Metal 1 layer Insulator Substrate • Top view Connected Not connected Integrated Circuit Layers Integrated Circuit Layers • Signal transfer speed is affected by the interconnect resistance and capacitance. – Resistance ↑ => Signal delay ↑ – Capacitance ↑ => Signal delay ↑ Integrated Circuit Layers • Resistance – = = = Direction of • : sheet resistance (constant) current flows ∙ ∙ • : resistivity (= , : conductivity) 1 – Material property (constant) – Unit: • : thickess (constant) Ω ∙ • : width (variable) • : length (variable) Cross-sectional area = • Example ∙ – : 17. , : 0.13 , : , : 1000 • = 17.1 -

Logic Functions Realized Using Clockless Gates for Rapid Single-Flux-Quantum Circuits

R2-4 SASIMI 2021 Proceedings Logic Functions Realized Using Clockless Gates for Rapid Single-Flux-Quantum Circuits Takahiro Kawaguchi Kazuyoshi Takagi Naofumi Takagi Graduate School of Informatics Graduate School of Engineering Graduate School of Informatics Kyoto University Mie University Kyoto University Kyoto, 606-8501, Japan Mie, 514-8507, Japan Kyoto, 606-8501, Japan [email protected] [email protected] [email protected] Abstract— Superconducting rapid single-flux- and the area occupied by a clock distribution network are quantum (RSFQ) circuit is a promising candidate reduced. The reduction of the pipeline depth leads to a for circuit technology in the post-Moore era. RSFQ fewer DFFs for path-balancing and a smaller circuit area. digital circuits operate with pulse logic and are A clockless AND gate and a clockless NIMPLY gate was usually composed of clocked gates. We have proposed proposed in [10]. A NIMPLY (not-imply) gate is an AND clockless gates, which can reduce the hardware gate with one inverted input, which implements x∧¬y.A amount of a circuit drastically. In this paper, we confluence buffer [1], which merges a pulse from its inputs first discuss logic functions realizable using clockless to its output, can be used as a clockless OR gate. gates. We show that all the 0-preserving functions A clockless gate realizes only a 0-preserving logic func- can be realized using the existing clockless gates, tion, which outputs 0 from the input value of all 0s, be- i.e., AND, OR, and NIMPLY (not-imply) gates. -

Characterization of the Cmos Finfet Structure On

CHARACTERIZATION OF THE CMOS FINFET STRUCTURE ON SINGLE-EVENT EFFECTS { BASIC CHARGE COLLECTION MECHANISMS AND SOFT ERROR MODES By Patrick Nsengiyumva Dissertation Submitted to the Faculty of the Graduate School of Vanderbilt University in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY in Electrical Engineering May 11, 2018 Nashville, Tennessee Approved: Lloyd W. Massengill, Ph.D. Michael L. Alles, Ph.D. Bharat B. Bhuva, Ph.D. W. Timothy Holman, Ph.D. Alexander M. Powell, Ph.D. © Copyright by Patrick Nsengiyumva 2018 All Rights Reserved DEDICATION In loving memory of my parents (Boniface Bimuwiha and Anne-Marie Mwavita), my uncle (Dr. Faustin Nubaha), and my grandmother (Verediana Bikamenshi). iii ACKNOWLEDGEMENTS This dissertation work would not have been possible without the support and help of many people. First of all, I would like to express my deepest appreciation and thanks to my advisor Dr. Lloyd Massengill for his continual support, wisdom, and mentoring throughout my graduate program at Vanderbilt University. He has pushed me to look critically at my work and become a better research scholar. I would also like to thank Dr. Michael Alles and Dr. Bharat Bhuva, who have helped me identify new paths in my research and have been a constant source of ideas. I am also very grateful to Dr. W. T. Holman and Dr. Alexander Powell for serving on my committee and for their constructive comments. Special thanks go to Dr. Jeff Kauppila, Jeff Maharrey, Rachel Harrington, and Tim Haeffner for their support with test IC designs and experiments. I would also like to thank Dennis Ball (Scooter) for his tremendous help with TCAD models. -

Memristor Nanodevice for Unconventional Computing:Review and Applications Mahyar Shahsavari, Pierre Boulet

Memristor nanodevice for unconventional computing:review and applications Mahyar Shahsavari, Pierre Boulet To cite this version: Mahyar Shahsavari, Pierre Boulet. Memristor nanodevice for unconventional computing:review and applications . [Research Report] Université de Lille 1, Sciences et Technologies; CRIStAL UMR 9189. 2016. hal-01480614 HAL Id: hal-01480614 https://hal.archives-ouvertes.fr/hal-01480614 Submitted on 1 Mar 2017 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Memristor nanodevice for unconventional computing: review and applications Mahyar Shahsavari, Pierre Boulet Univ. Lille, CNRS, Centrale Lille, UMR 9189 - CRIStAL Centre de Recherche en Informatique Signal et Automatique de Lille, F-59000 Lille, France. Abstract A memristor is a two-terminal nanodevice that its properties attract a wide community of re- searchers from various domains such as physics, chemistry, electronics, computer and neuroscience. The simple structure for manufacturing, small scalability, nonvolatility and potential of using in low power platforms are outstanding characteristics of this emerging nanodevice. In this report, we review a brief literature of memristor from mathematic model to the physical realization. We discuss different classes of memristors based on the material used for its manufacturing. The potential applications of memristor are presented and a wide domain of applications are explained and classified. -

The Roadmap to Realize Memristive Three- Dimensional Neuromorphic Computing System

We are IntechOpen, the world’s leading publisher of Open Access books Built by scientists, for scientists 4,800 122,000 135M Open access books available International authors and editors Downloads Our authors are among the 154 TOP 1% 12.2% Countries delivered to most cited scientists Contributors from top 500 universities Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI) Interested in publishing with us? Contact [email protected] Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com Chapter 2 The Roadmap to Realize Memristive Three- Dimensional Neuromorphic Computing System HongyuHongyu An, An, KangjunKangjun Bai Bai and Yang YiYang Yi Additional information is available at the end of the chapter http://dx.doi.org/10.5772/intechopen.78986 Abstract Neuromorphic computing, an emerging non-von Neumann computing mimicking the physical structure and signal processing technique of mammalian brains, potentially achieves the same level of computing and power efficiencies of mammalian brains. This chapter will discuss the state-of-the-art research trend on neuromorphic computing with memristors as electronic synapses. Furthermore, a novel three-dimensional (3D) neuro- morphic computing architecture combining memristor and monolithic 3D integration technology would be introduced; such computing architecture has capabilities to reduce the system power consumption, provide high connectivity, resolve the routing congestion issues, and offer the massively parallel data processing. Moreover, the design methodology of applying the capacitance formed by the through-silicon vias (TSVs) to generate a mem- brane potential in 3D neuromorphic computing system would be discussed in this chapter.