New Approaches for Memristive Logic Computations

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

CMOS Gate Drive IC with Embedded Cross Talk Suppression Circuitry for Power Electronic Applications

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Masters Theses Graduate School 8-2015 CMOS Gate Drive IC With Embedded Cross Talk Suppression Circuitry For Power Electronic Applications Jeffery M. Dix University of Tennessee - Knoxville, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_gradthes Recommended Citation Dix, Jeffery M., "CMOS Gate Drive IC With Embedded Cross Talk Suppression Circuitry For Power Electronic Applications. " Master's Thesis, University of Tennessee, 2015. https://trace.tennessee.edu/utk_gradthes/3471 This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a thesis written by Jeffery M. Dix entitled "CMOS Gate Drive IC With Embedded Cross Talk Suppression Circuitry For Power Electronic Applications." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Master of Science, with a major in Electrical Engineering. Benjamin J. Blalock, Major Professor We have read this thesis and recommend its acceptance: Jeremy Holleman, Daniel J. Costinett Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) CMOS Gate Drive IC With Embedded Cross Talk Suppression Circuitry For Power Electronic Applications A Thesis Presented for the Master of Science Degree The University of Tennessee, Knoxville Jeffery M. -

Episode 5.02 – NAND Logic

Episode 5.02 – NAND Logic Welcome to the Geek Author series on Computer Organization and Design Fundamentals. I’m David Tarnoff, and in this series, we are working our way through the topics of Computer Organization, Computer Architecture, Digital Design, and Embedded System Design. If you’re interested in the inner workings of a computer, then you’re in the right place. The only background you’ll need for this series is an understanding of integer math, and if possible, a little experience with a programming language such as Java. And one more thing. Our topics involve a bit of figuring, so it might help to keep a pencil and paper handy. In our last episode, we covered three attributes of the sum-of-product expression including its general format and the benefits derived from it, a method to generate a truth table from a given sum-of- products expression, and lastly, a simple procedure we can use to create the proper sum-of-products expression from a given truth table. In this episode, we’re going to look at a fourth attribute. While this last trait may appear to be no more than an interesting exercise in Boolean algebra, it turns out that it offers several benefits when we implement our SOP expressions with digital circuitry. In Episode 4.08 – DeMorgan’s Theorem, we showed how an inverter can be distributed across the inputs of an AND or an OR gate by flipping the operation. In other words, we can distribute an inverter from the output of an AND gate across all the gate’s inputs as long as we change the gate operation to an OR. -

LINEAR ALGEBRA METHODS in COMBINATORICS László Babai

LINEAR ALGEBRA METHODS IN COMBINATORICS L´aszl´oBabai and P´eterFrankl Version 2.1∗ March 2020 ||||| ∗ Slight update of Version 2, 1992. ||||||||||||||||||||||| 1 c L´aszl´oBabai and P´eterFrankl. 1988, 1992, 2020. Preface Due perhaps to a recognition of the wide applicability of their elementary concepts and techniques, both combinatorics and linear algebra have gained increased representation in college mathematics curricula in recent decades. The combinatorial nature of the determinant expansion (and the related difficulty in teaching it) may hint at the plausibility of some link between the two areas. A more profound connection, the use of determinants in combinatorial enumeration goes back at least to the work of Kirchhoff in the middle of the 19th century on counting spanning trees in an electrical network. It is much less known, however, that quite apart from the theory of determinants, the elements of the theory of linear spaces has found striking applications to the theory of families of finite sets. With a mere knowledge of the concept of linear independence, unexpected connections can be made between algebra and combinatorics, thus greatly enhancing the impact of each subject on the student's perception of beauty and sense of coherence in mathematics. If these adjectives seem inflated, the reader is kindly invited to open the first chapter of the book, read the first page to the point where the first result is stated (\No more than 32 clubs can be formed in Oddtown"), and try to prove it before reading on. (The effect would, of course, be magnified if the title of this volume did not give away where to look for clues.) What we have said so far may suggest that the best place to present this material is a mathematics enhancement program for motivated high school students. -

UNIT-I Mathematical Logic Statements and Notations

UNIT-I Mathematical Logic Statements and notations: A proposition or statement is a declarative sentence that is either true or false (but not both). For instance, the following are propositions: “Paris is in France” (true), “London is in Denmark” (false), “2 < 4” (true), “4 = 7 (false)”. However the following are not propositions: “what is your name?” (this is a question), “do your homework” (this is a command), “this sentence is false” (neither true nor false), “x is an even number” (it depends on what x represents), “Socrates” (it is not even a sentence). The truth or falsehood of a proposition is called its truth value. Connectives: Connectives are used for making compound propositions. The main ones are the following (p and q represent given propositions): Name Represented Meaning Negation ¬p “not p” Conjunction p q “p and q” Disjunction p q “p or q (or both)” Exclusive Or p q “either p or q, but not both” Implication p ⊕ q “if p then q” Biconditional p q “p if and only if q” Truth Tables: Logical identity Logical identity is an operation on one logical value, typically the value of a proposition that produces a value of true if its operand is true and a value of false if its operand is false. The truth table for the logical identity operator is as follows: Logical Identity p p T T F F Logical negation Logical negation is an operation on one logical value, typically the value of a proposition that produces a value of true if its operand is false and a value of false if its operand is true. -

Hybrid Memristor–CMOS Implementation of Combinational Logic Based on X-MRL †

electronics Article Hybrid Memristor–CMOS Implementation of Combinational Logic Based on X-MRL † Khaled Alhaj Ali 1,* , Mostafa Rizk 1,2,3 , Amer Baghdadi 1 , Jean-Philippe Diguet 4 and Jalal Jomaah 3 1 IMT Atlantique, Lab-STICC CNRS, UMR, 29238 Brest, France; [email protected] (M.R.); [email protected] (A.B.) 2 Lebanese International University, School of Engineering, Block F 146404 Mazraa, Beirut 146404, Lebanon 3 Faculty of Sciences, Lebanese University, Beirut 6573, Lebanon; [email protected] 4 IRL CROSSING CNRS, Adelaide 5005, Australia; [email protected] * Correspondence: [email protected] † This paper is an extended version of our paper published in IEEE International Conference on Electronics, Circuits and Systems (ICECS) , 27–29 November 2019, as Ali, K.A.; Rizk, M.; Baghdadi, A.; Diguet, J.P.; Jomaah, J. “MRL Crossbar-Based Full Adder Design”. Abstract: A great deal of effort has recently been devoted to extending the usage of memristor technology from memory to computing. Memristor-based logic design is an emerging concept that targets efficient computing systems. Several logic families have evolved, each with different attributes. Memristor Ratioed Logic (MRL) has been recently introduced as a hybrid memristor–CMOS logic family. MRL requires an efficient design strategy that takes into consideration the implementation phase. This paper presents a novel MRL-based crossbar design: X-MRL. The proposed structure combines the density and scalability attributes of memristive crossbar arrays and the opportunity of their implementation at the top of CMOS layer. The evaluation of the proposed approach is performed through the design of an X-MRL-based full adder. -

CSE Yet, Please Do Well! Logical Connectives

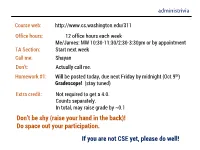

administrivia Course web: http://www.cs.washington.edu/311 Office hours: 12 office hours each week Me/James: MW 10:30-11:30/2:30-3:30pm or by appointment TA Section: Start next week Call me: Shayan Don’t: Actually call me. Homework #1: Will be posted today, due next Friday by midnight (Oct 9th) Gradescope! (stay tuned) Extra credit: Not required to get a 4.0. Counts separately. In total, may raise grade by ~0.1 Don’t be shy (raise your hand in the back)! Do space out your participation. If you are not CSE yet, please do well! logical connectives p q p q p p T T T T F T F F F T F T F NOT F F F AND p q p q p q p q T T T T T F T F T T F T F T T F T T F F F F F F OR XOR 푝 → 푞 • “If p, then q” is a promise: p q p q F F T • Whenever p is true, then q is true F T T • Ask “has the promise been broken” T F F T T T If it’s raining, then I have my umbrella. related implications • Implication: p q • Converse: q p • Contrapositive: q p • Inverse: p q How do these relate to each other? How to see this? 푝 ↔ 푞 • p iff q • p is equivalent to q • p implies q and q implies p p q p q Let’s think about fruits A fruit is an apple only if it is either red or green and a fruit is not red and green. -

Conditional Statement/Implication Converse and Contrapositive

Conditional Statement/Implication CSCI 1900 Discrete Structures •"ifp then q" • Denoted p ⇒ q – p is called the antecedent or hypothesis Conditional Statements – q is called the consequent or conclusion Reading: Kolman, Section 2.2 • Example: – p: I am hungry q: I will eat – p: It is snowing q: 3+5 = 8 CSCI 1900 – Discrete Structures Conditional Statements – Page 1 CSCI 1900 – Discrete Structures Conditional Statements – Page 2 Conditional Statement/Implication Truth Table Representing Implication (continued) • In English, we would assume a cause- • If viewed as a logic operation, p ⇒ q can only be and-effect relationship, i.e., the fact that p evaluated as false if p is true and q is false is true would force q to be true. • This does not say that p causes q • If “it is snowing,” then “3+5=8” is • Truth table meaningless in this regard since p has no p q p ⇒ q effect at all on q T T T • At this point it may be easiest to view the T F F operator “⇒” as a logic operationsimilar to F T T AND or OR (conjunction or disjunction). F F T CSCI 1900 – Discrete Structures Conditional Statements – Page 3 CSCI 1900 – Discrete Structures Conditional Statements – Page 4 Examples where p ⇒ q is viewed Converse and contrapositive as a logic operation •Ifp is false, then any q supports p ⇒ q is • The converse of p ⇒ q is the implication true. that q ⇒ p – False ⇒ True = True • The contrapositive of p ⇒ q is the –False⇒ False = True implication that ~q ⇒ ~p • If “2+2=5” then “I am the king of England” is true CSCI 1900 – Discrete Structures Conditional Statements – Page 5 CSCI 1900 – Discrete Structures Conditional Statements – Page 6 1 Converse and Contrapositive Equivalence or biconditional Example Example: What is the converse and •Ifp and q are statements, the compound contrapositive of p: "it is raining" and q: I statement p if and only if q is called an get wet? equivalence or biconditional – Implication: If it is raining, then I get wet. -

ECSE-4760 Real-Time Applications in Control & Communications

Rensselaer Polytechnic Institute ECSE-4760 Real-Time Applications in Control & Communications EXPERIMENTS IN DIGITAL LOGIC DESIGN Number of Sessions – 4 INTRODUCTION Over the past few decades the digital world has come into its own. Even though engineering has gone into specialization, it is necessary to understand digital circuits to be able to communicate with others. This experiment attempts to teach a simple method of designing digital circuits. Due to the quick pace of the lab, it is highly recommended that you read one of the references. This will enable you to proceed quickly through the preliminary problems so you will have more time for the design problems. The following is an outline of the experiment. Following each section will be a set of questions that should be answered to show an understanding of the material presented. Any difficulties should be referred to a reference or your instructor. You should use the DesignWorks (LogicWorks or any other you may have) logic circuit simulator on the Macintosh after most sections to cement together all the preceding sections. BACKGROUND THEORY Boolean Algebra Switching Algebra Combinational Logic Minimization Flip-Flops and Registers Counters Synthesis of Synchronous Circuits EXPERIMENTAL PROCEDURE Questions and Problems Simulator Operation & FPGA Implementation REFERENCES It is required that you show all circuits, as built, in your write-up. Please include equations too. The first part of the procedure section contains all the questions and problems to be answered and the second part describes the use of DesignWorks. Note: all references to DesignWorks (on Macintosh computers) throughout this procedure may be replaced with LogicWorks on the lab Windows PCs. -

Digital Logic Design

Digital Logic Design Chapter 3 Gate-Level Minimization Nasser M. Sabah Outline of Chapter 3 2 Introduction The Map Method Four-Variable Map Five-Variable Map Product of Sums Simplification NAND & NOR Implementation Other Two-Level Implementations Exclusive-OR Function Introduction 3 Gate-level minimization refers to the design task of finding an optimal gate-level implementation of Boolean functions describing a digital circuit. The Map Method 4 The complexity of the digital logic gates The complexity of the algebraic expression Logic minimization Algebraic approaches: lack specific rules The Karnaugh map A simple straight forward procedure A pictorial form of a truth table A diagram made up of squares Each square represents one minterm of the function that is to be minimized. Review of Boolean Function 5 Boolean function Sum of minterms Sum of products (or product of sum) in the simplest form A minimum number of terms A minimum number of literals The simplified expression may not be unique Two-Variable Map 6 A two-variable map Four minterms x' = row 0; x = row 1 y' = column 0; y = column 1 A truth table in square diagram Figure 3.1 Two-variable Map xy m3 xym 1 m 2 m 3 xyxy'' xy Representation of functions in the map Three-Variable Map 7 A three-variable map Eight minterms The Gray code sequence Any two adjacent squares in the map differ by only on variable. Primed in one square and unprimed in the other. e.g., m5 and m7 can be simplified. m57 m xy'(') z xyz xz y y xz Three-variable Map Three-Variable -

Lab 1: Study of Gates & Flip-Flops

Lab 1: Study of Gates & Flip-flops Aim To familiarize with circuit implementations using ICs and test the behavior of different logic gates and Flip-flops. Hardware Requirement a. Equipments - Digital IC Trainer Kit b. Discrete Components - 74LS00 Quad 2-Input NAND gate 74LS02 Quad 2-Input NOR gate 74LS04 Hex 1-Input NOT gate 74LS08 Quad 2-Input AND gate 74LS10 Triple 3-Input NAND gate 74LS11 Triple 3-Input AND gate 74LS32 Quad 2-Input OR gate 74LS86 Quad 2-Input XOR 74LS73 JK-Flip flop 74LS74 D Flip flop Background Digital logic devices are the circuits that electronically perform logic operations on binary variables. The binary information is represented by high and low voltage levels, which the device processes electronically. The devices that perform the simplest of the logic operations (such as AND, OR, NAND, etc.) are called gates. For example, an AND gate electronically computes the AND of the voltage encoded binary signals appearing at its inputs and presents the voltage encoded result at its output. The digital logic circuits used in this laboratory are contained in integrated circuit (IC) packages, with generally 14 or 16 pins for electrical connections. Each IC is labeled (usually with an 74LSxx number) to identify the logic it performs. The logic diagrams and pin connections for these IC’s are described in the TTL Data Book by Texas Instruments1. The transistor-transistor logic(TTL) IC’s used in this laboratory require a 5.0 volt power supply for operation. TTL inputs require a voltage greater than 2 volts to represent a binary 1 and a voltage less than 0.8 volts to represent a binary 0. -

Realization of Morphing Logic Gates in a Repressilator with Quorum Sensing Feedback

Realization of Morphing Logic Gates in a Repressilator with Quorum Sensing Feedback Vidit Agarwal, Shivpal Singh Kang and Sudeshna Sinha Indian Institute of Science Education and Research (IISER) Mohali, Knowledge City, SAS Nagar, Sector 81, Manauli PO 140 306, Punjab, India Abstract We demonstrate how a genetic ring oscillator network with quorum sensing feedback can operate as a robust logic gate. Specifically we show how a range of logic functions, namely AND/NAND, OR/NOR and XOR/XNOR, can be realized by the system, thus yielding a versatile unit that can morph between different logic operations. We further demonstrate the capacity of this system to yield complementary logic operations in parallel. Our results then indicate the computing potential of this biological system, and may lead to bio-inspired computing devices. arXiv:1310.8267v1 [physics.bio-ph] 30 Oct 2013 1 I. INTRODUCTION The operation of any computing device is necessarily a physical process, and this funda- mentally determines the possibilities and limitations of the computing machine. A common thread in the history of computers is the exploitation and manipulation of different natural phenomena to obtain newer forms of computing paradigms [1]. For instance, chaos comput- ing [2], neurobiologically inspired computing, quantum computing[3], and DNA computing[4] all aim to utilize, at the basic level, some of the computational capabilities inherent in natural systems. In particular, larger understanding of biological systems has triggered the interest- ing question: what new directions do bio-systems offer for understanding and implementing computations? The broad idea then, is to create machines that benefit from natural phenomena and utilize patterns inherent in systems to encode inputs and subsequently obtain a desired output. -

Logical Connectives Good Problems: March 25, 2008

Logical Connectives Good Problems: March 25, 2008 Mathematics has its own language. As with any language, effective communication depends on logically connecting components. Even the simplest “real” mathematical problems require at least a small amount of reasoning, so it is very important that you develop a feeling for formal (mathematical) logic. Consider, for example, the two sentences “There are 10 people waiting for the bus” and “The bus is late.” What, if anything, is the logical connection between these two sentences? Does one logically imply the other? Similarly, the two mathematical statements “r2 + r − 2 = 0” and “r = 1 or r = −2” need to be connected, otherwise they are merely two random statements that convey no useful information. Warning: when mathematicians talk about implication, it means that one thing must be true as a consequence of another; not that it can be true, or might be true sometimes. Words and symbols that tie statements together logically are called logical connectives. They allow you to communicate the reasoning that has led you to your conclusion. Possibly the most important of these is implication — the idea that the next statement is a logical consequence of the previous one. This concept can be conveyed by the use of words such as: therefore, hence, and so, thus, since, if . then . , this implies, etc. In the middle of mathematical calculations, we can represent these by the implication symbol (⇒). For example 3 − x x + 7y2 = 3 ⇒ y = ± ; (1) r 7 x ∈ (0, ∞) ⇒ cos(x) ∈ [−1, 1]. (2) Converse Note that “statement A ⇒ statement B” does not necessarily mean that the logical converse — “statement B ⇒ statement A” — is also true.