Vlsi Design Lecture Notes B.Tech (Iv Year – I Sem) (2018-19)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Role of Mosfets Transconductance Parameters and Threshold Voltage in CMOS Inverter Behavior in DC Mode

Preprints (www.preprints.org) | NOT PEER-REVIEWED | Posted: 28 July 2017 doi:10.20944/preprints201707.0084.v1 Article Role of MOSFETs Transconductance Parameters and Threshold Voltage in CMOS Inverter Behavior in DC Mode Milaim Zabeli1, Nebi Caka2, Myzafere Limani2 and Qamil Kabashi1,* 1 Department of Engineering Informatics, Faculty of Mechanical and Computer Engineering ([email protected]) 2 Department of Electronics, Faculty of Electrical and Computer Engineering ([email protected], [email protected]) * Correspondence: [email protected]; Tel.: +377-44-244-630 Abstract: The objective of this paper is to research the impact of electrical and physical parameters that characterize the complementary MOSFET transistors (NMOS and PMOS transistors) in the CMOS inverter for static mode of operation. In addition to this, the paper also aims at exploring the directives that are to be followed during the design phase of the CMOS inverters that enable designers to design the CMOS inverters with the best possible performance, depending on operation conditions. The CMOS inverter designed with the best possible features also enables the designing of the CMOS logic circuits with the best possible performance, according to the operation conditions and designers’ requirements. Keywords: CMOS inverter; NMOS transistor; PMOS transistor; voltage transfer characteristic (VTC), threshold voltage; voltage critical value; noise margins; NMOS transconductance parameter; PMOS transconductance parameter 1. Introduction CMOS logic circuits represent the family of logic circuits which are the most popular technology for the implementation of digital circuits, or digital systems. The small dimensions, low power of dissipation and ease of fabrication enable extremely high levels of integration (or circuits packing densities) in digital systems [1-5]. -

"Bob" Schreiner

Oral History of Robert “Bob” Schreiner Interviewed by: Stephen Diamond Recorded: June 10, 2013 Mountain View, California CHM Reference number: X6873.2014 © 2013 Computer History Museum Oral History of Robert “Bob” Schreiner Stephen Diamond: We're here at the Computer History Museum with Bob Schreiner. It's June 10th, 2013, and we're going to talk about the oral history of Synertek and the 6502. Welcome, Bob. Thanks for being here. Can you introduce yourself to us? Robert “Bob” Schreiner: Okay. My name is Bob Schreiner. I'm an ex-Fairchilder, one of the Fairchildren in the valley, and then involved in running a couple of other small semiconductor companies, and I started a semiconductor company. Diamond: So that would be Synertek. Schreiner: Synertek. Diamond: Tell us about that. Schreiner: Okay. As you know from an earlier session I left Fairchild Semiconductor around 1971. And at the time I left I was running the LSI program at Fairchild, and I was a big believer that the future marketplace for MOS technology would be in the custom area. And since Fairchild let that whole thing fall apart, I decided there's got to be room for a company to start up to do that very thing, work with big producers of hardware and develop custom chips for them so they would have a propriety product that would be difficult to copy. So I wrote a business plan, and I went around to a number of manufacturers. I had a computer guy [General Automation], and I had Bulova Watch Company, and I had a company that made electronic telephones [American Telephones], and who was the fourth guy? Escapes my memory right now, but the pitch basically was, "Your business, which now you manufacture things with discrete components, it's going to change. -

Logic Styles with Mosfets

Logic Styles with MOSFETs NMOS Logic One way of using MOSFET transistors to produce logic circuits uses only n-type (n-p-n) transistors, and this style is called NMOS logic (N for n-type transistors). An inverter circuit in NMOS is shown in the figure with n-p-n transistors replacing both the switch and the resistor of the inverter circuit examined earlier. The lower transistor in the circuit operates as a switch exactly as the idealised switch in the original circuit: with 5V on the Gate input, the conducting channel is created in the transistor and the “switch” is closed; with 0V on the Gate there is no channel and the transistor is non-conducting - the “switch” is open. The depletion mode transistor is produced by adding a small amount of donor material to the The upper transistor, called a depletion mode channel region of a n-p-n transistor, so that there are a small number of free electrons in the channel transistor, operates as a resistor to limit current even when there is no electric field across the flow when the “switch” is closed. This transistor is insulator. This provides a connection through the a modified n-p-n transistor that always has a transistor for all Gate voltages. The conductivity of channel present and is always conducting, although the channel is lowest (Resistance is highest) when the conductivity is low when there is 0V on the the Gate is at 0V. When the Gate is at 5V and more Gate and higher when 5V is on the Gate: see Box. -

A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes

382 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 65, NO. 2, FEBRUARY 2018 A New Paradigm in High-Speed and High-Efficiency Silicon Photodiodes for Communication—Part II: Device and VLSI Integration Challenges for Low-Dimensional Structures Hilal Cansizoglu , Member, IEEE, Aly F. Elrefaie, Fellow, IEEE, Cesar Bartolo-Perez, Toshishige Yamada, Senior Member, IEEE, Yang Gao, Ahmed S. Mayet, Mehmet F. Cansizoglu, Ekaterina Ponizovskaya Devine, Shih-Yuan Wang, Life Fellow, IEEE,and M. Saif Islam, Senior Member, IEEE (Invited Review Paper) Abstract— The ability to monolithically integrate high- Index Terms— CMOS integration, extended-reach links, speed photodetectors (PDs) with silicon (Si) can contribute high speed, high-efficiency photodetectors (PDs), high- to drastic reduction in cost. Such PDs are envisioned to performance computing, light detection and ranging, micro- be integral parts of high-speed optical interconnects in /nanostructures, single-photon detection, surface states, the future intrachip, chip-to-chip, board-to-board, rack-to- very-large-scale integration (VLSI) and ultralarge-scale inte- rack, and intra-/interdata center links. Si-based PDs are of gration (ULSI). special interest since they present the potential for mono- lithic integration with CMOS and BiCMOS very-large-scale integration and ultralarge-scale integration electronics. I. INTRODUCTION In the second part of this review, we present the efforts HE rise of distributed computing, cloud storage, social pursued by the researchers in engineering and integrating Si, SiGe alloys, and Ge PDs to CMOS and BiCMOS electron- Tmedia, and affordable hand-held devices currently allow ics and compare the performance of recently demonstrated extreme ease of transferring a plethora of data including CMOS-compatible ultrafast surface-illuminated Si PD with videos, pictures, and texts, all over the world. -

MOSFET - Wikipedia, the Free Encyclopedia

MOSFET - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/MOSFET MOSFET From Wikipedia, the free encyclopedia The metal-oxide-semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, pMOS FET). The 'metal' in the name (for transistors upto the 65 nanometer technology node) is an anachronism from early chips in which the gates were metal; They use polysilicon gates. IGFET is a related, more general term meaning insulated-gate field-effect transistor, and is almost synonymous with "MOSFET", though it can refer to FETs with a gate insulator that is not oxide. Some prefer to use "IGFET" when referring to devices with polysilicon gates, but most still call them MOSFETs. With the new generation of high-k technology that Intel and IBM have announced [1] (http://www.intel.com/technology/silicon/45nm_technology.htm) , metal gates in conjunction with the a high-k dielectric material replacing the silicon dioxide are making a comeback replacing the polysilicon. Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM, have begun to use a mixture of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs. -

DEVICE and CIRCUIT DESIGN for VLSI by Amr Mohsen

31 DEVICE AND CIRCUIT DESIGN FOR VLSI by Amr Mohsen* Intel Corporation 3065 Bowers Avenue Santa Clara, California 95051 ABSTRACT A review of the device and circuit design complexity and limitations for VLSI is presented. VLSI device performance will be limited by second order device effects, interconnection line de lay and current density and chip power dissipation. The complexity of VLSI circuit design will require hierarchial structured design methodology with special consideration of testability dnd more emphasis on redundancy. New organizations of logic function architectures and smart memories will evolve to take advantage of the topological properties of the VLSI silicon technology. * The author is also on the faculty of California Institute of Technology CALTECH CONFERENCE ON VLSI, January 1979 32 Amr Mohsen I. INTRODUCTION: As semiconductor technology has evolved from discrete to small-scale to medium-scale and through large-scale integration levels a rapid decrease in the cost per function provided by the technology have opened up new applications and industries. Today there is a large interest in the next phase of integration: very large scale integration (VLSI). The semi conductor technology will be able to fabricate chips with more than lOOK devices (l) in the 1980's. The continuous scaling of the semi- conductor devices and increase in components counts on a single chip is resulting in more complex technology developments, device and circuit designs and product definition. In this review paper, projections of how device technology will evolve in the future and the problems and limitations of device and circuit design for VLSI are presented. VLSI TECHNOLOGIES: In Fig. -

An Integrated Semiconductor Device Enabling Non-Optical Genome Sequencing

ARTICLE doi:10.1038/nature10242 An integrated semiconductor device enabling non-optical genome sequencing Jonathan M. Rothberg1, Wolfgang Hinz1, Todd M. Rearick1, Jonathan Schultz1, William Mileski1, Mel Davey1, John H. Leamon1, Kim Johnson1, Mark J. Milgrew1, Matthew Edwards1, Jeremy Hoon1, Jan F. Simons1, David Marran1, Jason W. Myers1, John F. Davidson1, Annika Branting1, John R. Nobile1, Bernard P. Puc1, David Light1, Travis A. Clark1, Martin Huber1, Jeffrey T. Branciforte1, Isaac B. Stoner1, Simon E. Cawley1, Michael Lyons1, Yutao Fu1, Nils Homer1, Marina Sedova1, Xin Miao1, Brian Reed1, Jeffrey Sabina1, Erika Feierstein1, Michelle Schorn1, Mohammad Alanjary1, Eileen Dimalanta1, Devin Dressman1, Rachel Kasinskas1, Tanya Sokolsky1, Jacqueline A. Fidanza1, Eugeni Namsaraev1, Kevin J. McKernan1, Alan Williams1, G. Thomas Roth1 & James Bustillo1 The seminal importance of DNA sequencing to the life sciences, biotechnology and medicine has driven the search for more scalable and lower-cost solutions. Here we describe a DNA sequencing technology in which scalable, low-cost semiconductor manufacturing techniques are used to make an integrated circuit able to directly perform non-optical DNA sequencing of genomes. Sequence data are obtained by directly sensing the ions produced by template-directed DNA polymerase synthesis using all-natural nucleotides on this massively parallel semiconductor-sensing device or ion chip. The ion chip contains ion-sensitive, field-effect transistor-based sensors in perfect register with 1.2 million wells, which provide confinement and allow parallel, simultaneous detection of independent sequencing reactions. Use of the most widely used technology for constructing integrated circuits, the complementary metal-oxide semiconductor (CMOS) process, allows for low-cost, large-scale production and scaling of the device to higher densities and larger array sizes. -

Mos Technology, 1963-1974: a Dozen Crucial Years

One of IBM’s most important MOS Technology, 1963-1974: A Dozen Crucial Years contributions to MOS research came from the Components Division, which was responsible for developing by Ross Knox Bassett and manufacturing bipolar transistors for its large computer systems and had very little interest in MOS transistors line can be drawn from the as such. As part of its work on Frosch’s and Derick’s work on bipolar transistors, Donald Kerr and silicon dioxide to the MOS (metal- a group of engineers had discovered A that depositing small amounts of oxide-semiconductor) transistor’s domi- nance of semiconductor technology, phosphorous on the silicon-dioxide but it is neither short nor straight. That surface and forming a layer of line has several discernable segments, phosphosilicate glass (PSG) could first from Frosch and Derick’s work, limit the amount of leakage in bipolar until 1963. In this interval, by and transistors and play an important role large, no one thought seriously about a in enhancing the stability of MOS metal-oxide-semiconductor as a viable transistors. Jerome Eldridge and Pieter technology in its own right. The second Balk from IBM Research implemented segment runs from 1963, when the this work by using thin layers of combination of integrated circuits and PSG to make stable MOS devices. the planar manufacturing process had Other important work on the physics FIG. 2. Drawing of Atalla and Kahng’s “silicon-silicon dioxide surface device,” now known as and chemistry of MOS devices done led people to see MOS transistors as a the MOS transistor, from a 1961 Bell Labs technical memorandum by Kahng. -

6502 Introduction

6502 Introduction Philipp Koehn 18 September 2019 Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1 some history Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1971 2 • First microprocessor on an integrated circuit: Intel 4004 • 4-bit central processing unit, 12 bit address space (4KB) Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1975 3 • MOS Technology 6502 • Dominant CPU in home computers for a decade (Atari, Apple II, Nintendo Entertainment System, Commodore PET) Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1977 4 • Atari 2600 • Video game console: Pong, Pac Man, ... connected to TV Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1980 5 • Commodore VIC20 • 1 MHz, 5KB RAM, BASIC, 3.5KB RAM, 176x184 3 bit color video Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1982 6 • Commodore C64 • 64KB RAM, 320x200 4 bit color video Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 Commodore C64 7 • BASIC programming language, but serious programs written in assembly • No fancy stuff like multi-process, user accounts, virtual memory, etc. • Machine itself had no mass storage - had to buy tape drive, then floppy disk drive, machine was obsolete once hard drives came around Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 BASIC Demo 8 • Commands get executed (just like Python interpreter) -

Bicmos Digital Circuit Design

BiCMOS Digital Circuit Design Review of CMOS & NMOS Inverter Design - delay time - pair delay - driving large capacitive loads Features of BiCMOS Digital Circuit BiCMOS Inverters -basic type - delay time - improved type - full swing - design example a. size optimization b. driving large capacitive loads BiCMOS Gate Power-Supply Sensitivity - voltage scaling - low voltage gate I/O Interface - input - output - logic conversion Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-1 NMOS DIGITAL CIRCUITS Static inverters Load Vout ==> V in driver A B C IDS VGS=V(1) C B A VDS (driver) VDD Vth VDD D: in in Vout VGS=V(1) VGS=V(0) V(0) V(0) V(1) V(0) V(1) Vin ― Static power dissipation during Vout=V(0) Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-2 Switching Characteristics of CMOS Inverter CMOS inverter VDD VDD T 2 V (t) o t Vin(t) T1 CL +VDD Vin(t) 0 t +VDD 0.9VDD 0.1VDD t td tf tr Trajectory of n-transistor operating point during switching in CMOS inverter Input transition : X1 X2 Output transition: X2 X3 Vds=Vgs-Vt UNSATURATED SATURATED STATE STATE X2 Vgs=VDD Ids OPERATING POINT AFTER COMPLETION OF SWITCHING INITIAL OPERATING POINT X3 X1 0 VDD Vo(t) Tai-Haur Kuo, EE, NCKU, 1997 BiCMOS Circuit Design 3-3 Rise Time and Fall Time of CMOS Inverter > Equivalent Circuit V DD VDD > Fall p-DEVICE p-DEVICE t=0 t=0 I Vin ↑ c Ic Idsn R V c C o Vo n-DEVICE L n-DEVICE CL Vo ↓ SATURATION: VVoD≥ D− Vtn 0 < VV≤ − V (a) SATURATION: 0 DD tn > Rise VDD VDD p-DEVICE p-DEVICE Idsp Rc Vin ↓ I Ic Vo ↑ t=0 c Vo Vo n-DEVICE CL n-DEVICE -

The Ultimate C64 Overview Michael Steil, 25Th Chaos Communication Congress 2008

The Ultimate C64 Overview Michael Steil, http://www.pagetable.com/ 25th Chaos Communication Congress 2008 Retrocomputing is cool as never before. People play Look and Feel C64 games in emulators and listen to SID music, but few people know much about the C64 architecture A C64 only needs to be connected to power and a TV and its limitations, and what programming was like set (or monitor) to be fully functional. When turned back then. This paper attempts to give a comprehen- on, it shows a blue-on-blue theme with a startup mes- sive overview of the Commodore 64, including its in- sage and drops into a BASIC interpreter derived from ternals and quirks, making the point that classic Microsoft BASIC. In order to load and save BASIC computer systems aren't all that hard to understand - programs or use third party software, the C64 re- and that programmers today should be more aware of quires mass storage - either a “datasette” cassette the art that programming once used to be. tape drive or a disk drive like the 5.25" Commodore 1541. Commodore History Unless the user really wanted to interact with the BA- SIC interpreter, he would typically only use the BA- Commodore Business Machines was founded in 1962 SIC instructions LOAD, LIST and RUN in order to by Jack Tramiel. The company specialized on elec- access mass storage. LOAD"$",8 followed by LIST tronic calculators, and in 1976, Commodore bought shows the directory of the disk in the drive, and the chip manufacturer MOS Technology and decided LOAD"filename",8 followed by RUN would load and to have Chuck Peddle from MOS evolve their KIM-1 start a program. -

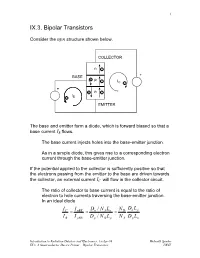

IX.3. a Semiconductor Device Primer – Bipolar Transistors LBNL 2

1 IX.3. Bipolar Transistors Consider the npn structure shown below. COLLECTOR n- BASE + +p -IC- + +n- I -B EMITTER The base and emitter form a diode, which is forward biased so that a base current IB flows. The base current injects holes into the base-emitter junction. As in a simple diode, this gives rise to a corresponding electron current through the base-emitter junction. If the potential applied to the collector is sufficiently positive so that the electrons passing from the emitter to the base are driven towards the collector, an external current IC will flow in the collector circuit. The ratio of collector to base current is equal to the ratio of electron to hole currents traversing the base-emitter junction. In an ideal diode IC I nBE Dn / N ALn N D Dn Lp = = = I B I pBE Dp / N D Lp N A Dp Ln Introduction to Radiation Detctors and Electronics, 13-Apr-99 Helmuth Spieler IX.3. A Semiconductor Device Primer – Bipolar Transistors LBNL 2 If the ratio of doping concentrations in the emitter and base regions ND /NA is sufficiently large, the collector current will be greater than the base current. ⇒ DC current gain Furthermore, we expect the collector current to saturate when the collector voltage becomes large enough to capture all of the minority carrier electrons injected into the base. Since the current inside the transistor comprises both electrons and holes, the device is called a bipolar transistor. Dimensions and doping levels of a modern high-frequency transistor (5 – 10 GHz bandwidth) 0 0.5 1.0 1.5 Distance [µm] (adapted from Sze) Introduction to Radiation Detctors and Electronics, 13-Apr-99 Helmuth Spieler IX.3.