The Ultimate C64 Overview Michael Steil, 25Th Chaos Communication Congress 2008

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

"Bob" Schreiner

Oral History of Robert “Bob” Schreiner Interviewed by: Stephen Diamond Recorded: June 10, 2013 Mountain View, California CHM Reference number: X6873.2014 © 2013 Computer History Museum Oral History of Robert “Bob” Schreiner Stephen Diamond: We're here at the Computer History Museum with Bob Schreiner. It's June 10th, 2013, and we're going to talk about the oral history of Synertek and the 6502. Welcome, Bob. Thanks for being here. Can you introduce yourself to us? Robert “Bob” Schreiner: Okay. My name is Bob Schreiner. I'm an ex-Fairchilder, one of the Fairchildren in the valley, and then involved in running a couple of other small semiconductor companies, and I started a semiconductor company. Diamond: So that would be Synertek. Schreiner: Synertek. Diamond: Tell us about that. Schreiner: Okay. As you know from an earlier session I left Fairchild Semiconductor around 1971. And at the time I left I was running the LSI program at Fairchild, and I was a big believer that the future marketplace for MOS technology would be in the custom area. And since Fairchild let that whole thing fall apart, I decided there's got to be room for a company to start up to do that very thing, work with big producers of hardware and develop custom chips for them so they would have a propriety product that would be difficult to copy. So I wrote a business plan, and I went around to a number of manufacturers. I had a computer guy [General Automation], and I had Bulova Watch Company, and I had a company that made electronic telephones [American Telephones], and who was the fourth guy? Escapes my memory right now, but the pitch basically was, "Your business, which now you manufacture things with discrete components, it's going to change. -

The Canon Cat After of Release Before Macintosh

LORI EMERSON & FINN BRUNTON THE CANON CAT PROCESSING ADVANCED WORK In the fall of 2014, Finn Brunton, an assistant professor at NYU, contacted Lori Emerson, Director of the Media Archaeology Lab (MAL) at the University of Colorado, Boulder, about a rare fi nd he came across on ebay: a Canon Cat, which billed itself in 1986 as an “advanced work processor.” The MAL wasn’t immediately able to purchase the machine; however, Brunton purchased the Canon Cat with the agreement that he’d experiment with the Canon Cat for six months or so, sell it to the MAL, and then he and Emerson would co-write a piece – now, this piece – on the obscure machine from an ever-more distant past. Here, we hope to give you a glimpse into what computing could have been and still could be. 353 [SHIFT]+[DOCUMENT] [SHIFT]+[DOCUMENT] Who will the user be? The shape that early personal Jef Raskin began to work on designing the Canon Cat after computing takes rests in part on this question, with he left Apple in 1982, two years before release of Macintosh. its implicit temporal paradox. The scenario, or persona, The Cat was then introduced to the public by Canon in 1987 or model, or instance of the user threads through the for $1495 – roughly $3100 in 2015. Although the Cat was production of the machine, from input devices and discontinued after only six months, around 20,000 units performance criteria to software, industrial design, and were sold during this time. The Canon Cat fascinates me marketing. -

Sensors: Sensing and Data Acquisidon

Sensors: Sensing and Data Acquisi3on Prof. Yan Luo For UMass Lowell 16.480/552 Sensors: Sensing and Data Acquisi3on 1 Prof. Yan Luo, UMass Lowell Outline • Sensors • Sensor interfacing • Sensor data conversion and acquisi3on • PIC microcontroller programming • Lab 1: Sensor design and data acquisi3on (a light intensity sensor) Sensors: Sensing and Data Acquisi3on 2 Prof. Yan Luo, UMass Lowell Basic Principle of Sensors • Transducer: a device that converts energy from one form to another • Sensor: converts a physical parameter to an electric output – Electric output is desirable as it enables further signal processing. • Actuator: coverts an electric signal to a physical output Sensors: Sensing and Data Acquisi3on 3 Prof. Yan Luo, UMass Lowell Sensors • Cameras • Analog sensors • Accelerometer - Con3nuously varying output • Rate gyro • Digital sensors • Strain gauge - on/off • Microphone - Pulse trains (freq convey measurement) • Magnetometer • Chemical sensors • Op3cal sensors Sensors: Sensing and Data Acquisi3on 4 Prof. Yan Luo, UMass Lowell Example: Photoresistor • Or Light Dependent Resistor (LDR) – Resistance decreases with increasing light intensity – Made of semiconductor – Photons absorbed cause electrons to jump into conduc3on band Sensors: Sensing and Data Acquisi3on 5 Prof. Yan Luo, UMass Lowell Interfacing with Sensors • Interface circuitry • ADC • Interfaces of the embedded system • SoVware drivers and APIs Sensors: Sensing and Data Acquisi3on 6 Prof. Yan Luo, UMass Lowell Example voltage divider circuit Vcc R2 V=Vcc x R1/(R1+R2) V R1 Sensors: Sensing and Data Acquisi3on 7 Prof. Yan Luo, UMass Lowell Analog-Digital Converter (ADC) • Types of ADC – Integrang ADC • Internal voltage controlled oscillator • slow – Successive approximaon ADC • Digital code driving the analog reference voltage – Flash ADC • A bank of comparators • Fast Sensors: Sensing and Data Acquisi3on 8 Prof. -

New Book on Commodore’S First Computer, the Bil Herd — AKA “The Animal,” He PET

Fort Worth Dallas Atari, and Nintendo. Designer of New Book on Commodore’s first computer, the Bil Herd — AKA “The Animal,” he PET. His relationship with Jack designed the ill-fated Plus/4 Commodore Tramiel eventually soured with computer and later went on to disastrous consequences. design the Commodore 128. Known About the Book to wrestle executives in the hallways September 2005 Robert Yannes — Frustrated of Commodore. Responsible for The Spectacular Rise and Fall of musician and synthesizer aficionado. many holes in the walls of Commodore tells the story of Designed the Commodore 64 and Commodore headquarters. Commodore through first-hand its famous sound chip, the SID. accounts by the actual Commodore Jay Miner — Brilliant ex-Atari engineers and managers who made Al Charpentier — Chain smoking engineer responsible for the Atari the company. From their entry into computer graphics pioneer and 800 computer. Co-designer of the computers in 1976 until their demise architect of the VIC and VIC-II Atari 2600. Inventor of the ground in 1994, the Commodore years were chips. breaking Amiga computer for always turbulent and exciting. Commodore. All his projects were Commodore had astounding success Thomas Rattigan — One time co-designed by his faithful dog and with their computers, including the President and CEO of Commodore official Commodore employee, Pet, the Vic-20, the Commodore 64 computers who saved the company Mitchy. and the incredible Amiga computers. from bankruptcy, only to collide Although other companies received with financier Irving Gould. On his George Robbins — Designer of the more press, Commodore sold more last day with Commodore he was low cost Amiga 500 computer. -

Retrocomputing As Preservation and Remix

Retrocomputing as Preservation and Remix Yuri Takhteyev Quinn DuPont University of Toronto University of Toronto [email protected] [email protected] Abstract This paper looks at the world of retrocomputing, a constellation of largely non-professional practices involving old computing technology. Retrocomputing includes many activities that can be seen as constituting “preservation.” At the same time, it is often transformative, producing assemblages that “remix” fragments from the past with newer elements or joining together historic components that were never combined before. While such “remix” may seem to undermine preservation, it allows for fragments of computing history to be reintegrated into a living, ongoing practice, contributing to preservation in a broader sense. The seemingly unorganized nature of retrocomputing assemblages also provides space for alternative “situated knowledges” and histories of computing, which can sometimes be quite sophisticated. Recognizing such alternative epistemologies paves the way for alternative approaches to preservation. Keywords: retrocomputing, software preservation, remix Recovering #popsource In late March of 2012 Jordan Mechner received a shipment from his father, a box full of old floppies. Among them was a 3.5 inch disk labelled: “Prince of Persia / Source Code (Apple) / ©1989 Jordan Mechner (Original).” Mechner’s announcement of this find on his blog the next day took the world of nerds by storm.1 Prince of Persia, a game that Mechner single-handedly developed in the late 1980s, revolutionized computer games when it came out due to its surprisingly realistic representation of human movement. After being ported to DOS and Apple’s Mac OS in the early 1990s the game sold 2 million copies (Pham, 2001). -

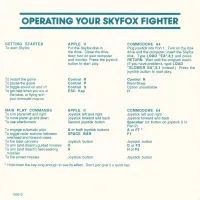

Skyfox Fighter

OPERATING YOUR SKYFOX FIGHTER GETTING STARTED APPLE II COMMODORE 64 To start Skyfox Put the Skyfox disk in Plug joystick into Port 1. Turn on the disk the drive. Close the drive drive and the computer; insert the Skyfox door; turn on your computer disk. Type LOAD "EA",8,1 and press and monitor. Press the joystick RETURN. Wait until the program loads. button to start play. (If you have problems, type LOAD "SLOWER EA",8,1 instead.) Press the joystick button to start play. To restart the game Control R Control R To pause the game Control P Run/Stop To toggle sound on and off Control S Option unavailable To get help when you are at ESC Key H the base, or flying with your computer map up MAIN PLAY COMMANDS APPLE II COMMODORE 64 To turn plane left and right Joystick left and right Joystick left and right To move plane up and down Joystick forward and back Joystick forward and back To use afterburners Second joystick button Spacebar (or button on joystick 2 in Port 2) To engage automatic pilot A or both joystick buttons AorF7* To toggle radar scanner between SPACE BAR F1 overhead and forward views To fire laser cannons Joystick button Joystick button To arm (and disarm) guided missiles G G or F3 To arm (and disarm) heat-seeking H H or F5 missiles To fire armed missiles Joystick button Joystick button • Hold down the key long enough to see' its effect. Don't just give it a quick tap. 103619 GETTING STARTED ATARI ST COMMODORE AMIGA To start Skyfox Put the Skyfox disk in After kickstarting your Amiga, insert the the drive and turn on the Skyfox disk in the drive. -

Go Forth with TTL !

Go Forth with TTL ! The Gigatron TTL Color Computer Forth for a Very Unusual Processor Ken Boak SV Fig. Forth Day 2019 . In September of 1975, MOS Technology launched the 6502 at the Wescon75 Computer Conference in San Francisco. Chuck Peddle and his team had created a very lean, stripped down, small die cpu. Costing just $25, the 6502 was a fraction of the cost of its nearest competitor. At that time the Intel 8080 was $360 and the Motorola 6800 was $175 . The 6502 was clearly a disruptive usurper. 25 year old, HP Engineer, Steve Wozniak, realised that this new microprocessor would be a game-changer and went on to incorporate it into the small computer he was developing. That machine went on to become the Apple I. In 1975 7400 TTL was the “Bread and Butter” of logic design: 7400 series TTL integrated circuits were developed in the early 1960’s. Initially quite expensive so mainly used in Military and Aerospace applications. By the early 1970’s TTL had become a versatile family of standardised, low cost,. easy to use logic. Typically about $1 per device. 7400 series logic was widely used in the design of minicomputers, including the PDP-11, the Data General Nova 1200 and later models of PDP-8. TTL was a viable, faster and cheaper processing solution than the emerging 8-bit microprocessors such as MOS 6502, Intel 8080 and the Motorola 6800. Essential Reading 16-bit TTL CPU board from Data General Nova 1200 The Gigatron TTL Computer – What is it? Started as a Hackaday.io project in Spring 2017 by Marcel van Kervinck of The Hague, Netherlands. -

Exploring Software Inefficiency With

ZeroSpy: Exploring Software Inefficiency with Redundant Zeros Xin You∗, Hailong Yang∗y, Zhongzhi Luan∗, Depei Qian∗ and Xu Liuz Beihang University, China∗, North Carolina State University, USAz State Key Laboratory of Mathematical Engineering and Advanced Computing, Wuxi, Chinay fyouxin2015,hailong.yang,07680,[email protected]∗, [email protected] Abstract—Redundant zeros cause inefficiencies in which the 1 for(int i=0;i<1000;++i) { 2 A[i] = 0; B[i] = i; zero values are loaded and computed repeatedly, resulting in 3 } 4 ... unnecessary memory traffic and identity computation that waste 5 for(int i=0;i<1000;++i) memory bandwidth and CPU resources. Optimizing compilers 6 I C[i] = A[i]-B[i]; is difficult in eliminating these zero-related inefficiencies due to Listing 1. An example code working on redundant zeros, where all variables are 32-bit integers. limitations in static analysis. Hardware approaches, in contrast, optimize inefficiencies without code modification, but are not enough to fulfill the computation, which yields better cache widely adopted in commodity processors. In this paper, we 1 propose ZeroSpy - a fine-grained profiler to identify redundant usage and vectorization potentials . zeros caused by both inappropriate use of data structures and Actually, a larger number of real-world applications (e.g., useless computation. ZeroSpy also provides intuitive optimization deep neural network and high-efficiency video coding) have guidance by revealing the locations where the redundant zeros already been reported to contain a significant amount of happen in source lines and calling contexts. The experimental redundant zeros and achieved significant speedup from the results demonstrate ZeroSpy is capable of identifying redundant zeros in programs that have been highly optimized for years. -

"Firefly" Z80 General-Purpose Retro Computing Platform

"FIREFLY" Z80 GENERAL-PURPOSE RETRO COMPUTING PLATFORM THREE FARTHING LABS http://www.threefarthing.com Page 1 of 13 PREFACE A project has to have a name and this one wound up being called "Firefly" as it©s the culmination of a wirewrap board begun several years ago while binge-watching the series of the same name. That board, in turn, was a redesign of a single board computer I created in 1998, creatively named the "SBCZ1." All three of these projects were begun as a chance to tinker with a processor I first met hands- on in 1984, the ZiLOG Z-80, though it was long-established by that time and dominated the business computer market. It was the CPU of preference behind most CP/M machines and CP/M was what I wanted to tinker with again, from the ground up ± not in some cozy emulator. When I began preparing to design the board I looked around on the Internet and found many excellent Z80 projects, including kit options. The choice was made to "roll my own" for numerous reasons. In the SBCZ1 I had most of a good design and wanted to retain a lot of hard work (done before I had Internet access, mind you). There were also specific reasons for wanting "to stay within ZiLOG canon" and work with a particular hardware configuration. I saw no kits that did just what I wanted in the way that I wanted. There was also a desire to maintain modularity and be extensible but not require a proliferation of modules for what I considered core functionality, yet great restraint was employed to keep "core functionality" spartan. -

Commodore 64 Users Guide

INTRODUCTION Now that you've become more intimately involved with your Commo- dore 64, we want you to know that our customer support does not stop here. You may not know it, but Commodore has been in business for over 23 years. In the 1970's we introduced the first self-contained per- sonal computer (the PET). We have since become the leading computer company in many countries of the world. Our ability to design and manufacture our own computer chips allows us to bring you new and better personal computers at prices way below what you'd expect for this level of technical excellence. Commodore is committed to supporting not only you, the end user, but also the dealer you bought your computer from, magazines which publish how-to articles showing you new applications or techniques, and . importantly . software developers who produce programs on cartridge, disk and tape for use with your computer. We encourage you to establish or join a Commodore "user club" where you can learn new techniques, exchange ideas and share discoveries. We publish two separate magazines which contain programming tips, information on new products and ideas for computer applications. (See Appendix N). In North America, Commodore provides a "Commodore Information Network" on the CompuServe Information Service . to access this network, all you need is your Commodore 64 computer and our low cost VICMODEMtelephone interface cartridge (or other compatible modem). The following APPENDICEScontain charts, tables, and other informa- tion which help you program your Commodore 64 faster and more efficiently. They also include important information on the wide variety of Commodore products you may be interested in, and a bibliography listing of over 20 books and magazines which can help you develop your programming skills and keep you current on the latest information con- cerning your computer and peripherals. -

Commodore 128 Book 2 Adva

COMMODORE C12S BOOK 2 ADVANCED PROGRAMMING COMMODORE el28 ADVANCED PROGRAMMING by Ian Sinclair Glentop Publishers Ltd MARCH 1986 All programs in this book have been written expressly to illustrate specific teaching points. They are not warranted as being suitable for any particular application. Every care has been taken in the writing and presentation of this book but no responsibility is assumed by the author or publishers for any errors or omissions contained herein. COPYRIGHT © Glentop Publishers Ltd 1986 World rights reserved No part of this pUblication may be copied, transmitted or stored in a retrieval system or reproduced in any way including but not limited to photography, photocopy, magnetic or other recording means, without prior permission from the publishers, with the exception of material entered and executed on a computer system for the reader's own use ISBN 1 85181 034 X Published by: Glentop Publishers Ltd Standfast House Bath Place High Street Barnet Herts ENS SXE Tel: 01-441-4130 Printed in Great Britain by The Eastern Press Ltd., London and Reading Contents PREFACE CHAPTER 1 Reminders roundup • Storage space • Machine code • Principles of programming. Other languages CHAPTER 2 Why use disks? • What is a disk system? • Tracks, sectors and density. Formatting disks. Storage space. The disk filing system • Loading and saving • More disk commands • Clearing, retitling and erasing. Backing up • Copying a named flle • Deleting flles • Wildcards and wiping. Protecting disks and programs. Renaming flles CHAPTER 3 Text display. Screen clear and print location. Print fielding. Formatting numbers • Standard form • Money amounts • Titles and centering. Windows. Hard copy CHAPTER 4 Working with numbers. -

IEEE Spectrum: 25 Microchip

IEEE Spectrum: 25 Microchips That Shook the World http://www.spectrum.ieee.org/print/8747 Sponsored By Select Font Size: A A A 25 Microchips That Shook the World By Brian R. Santo This is part of IEEE Spectrum 's Special Report: 25 Microchips That Shook the World . In microchip design, as in life, small things sometimes add up to big things. Dream up a clever microcircuit, get it sculpted in a sliver of silicon, and your little creation may unleash a technological revolution. It happened with the Intel 8088 microprocessor. And the Mostek MK4096 4-kilobit DRAM. And the Texas Instruments TMS32010 digital signal processor. Among the many great chips that have emerged from fabs during the half-century reign of the integrated circuit, a small group stands out. Their designs proved so cutting-edge, so out of the box, so ahead of their time, that we are left groping for more technology clichés to describe them. Suffice it to say that they gave us the technology that made our brief, otherwise tedious existence in this universe worth living. We’ve compiled here a list of 25 ICs that we think deserve the best spot on the mantelpiece of the house that Jack Kilby and Robert Noyce built. Some have become enduring objects of worship among the chiperati: the Signetics 555 timer, for example. Others, such as the Fairchild 741 operational amplifier, became textbook design examples. Some, like Microchip Technology’s PIC microcontrollers, have sold billions, and are still doing so. A precious few, like Toshiba’s flash memory, created whole new markets.