Xcell Journal Issue 43, Summer 2002

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Vhsic Hardware Description Language Compiler for Logic Cell Arrays

A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS by Bing Liu A thesis presented to the university of Mânitoba in partial fulfillment of úe requirements of the degree of Maste¡ of Science in Elecrical and Computel Engineering Winnipeg, Manitoba, Canada @ Bing Liu, January 1990 Bibliothèque nat¡onale rE fr"3""i"i;tjo'",' du Canada Canadian Theses Serv¡ce Service des thèses canadiennes Otta'¿/ã. Can¿da Kl A ON¡ The author has granted an inevocable non' L'auteur a accordé une licence iffévocable et exclusive licence allowing the National Library non exclusive permettant à h Bibliothèque of Canada to reproduce, loan, distribute or sell nationale du Canada.de reproduire, prêter, copies of his/her thesis by any means and in distribuer ou vendre des copies de sa thèse any form or format, making this thesis avaihble de quelque manière et sous quelque forme to ¡nterested persons. que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées. The author retains ownership of the copyright L auteur conserve la propriété du droit d'auteur in his/her thesis. Neither the thesis nor qui protà?e sa thèse. Ni la thèse ni des extraits substantial extracts from it may be printed or substantiels de celle-ci ne doivent être otherw¡se reproduced without his/her per' imprimés ou autrement reproduits sans son mission. autorisation. ISBN ø-315-7 r7s t -3 Canadä A VHSIC HARDWARE DESCRIPTION I.ANGUAGE COMPILER FOR LOG]C CEI,L ARRAYS BY BING LIU A thesis subnrined lo thc Fact¡lty of Crâduate Studies of the University of M¿nitoba in partial fulfìllment of the requirenrents of the degree of MASTM O¡' SC]MICE o 1990 Permission has becn granted to the L¡BRÁRY OF THE UNIVER' SITY OF MANITOBA to lend o¡ sell copies of tlt¡s thesis. -

Going Vertical: a New Integration Era in the Semiconductor Industry Table of Contents

Going vertical: A new integration era in the semiconductor industry Table of contents 01 Executive overview Integration in the 02 semiconductor industry Strategic options for 03 semiconductor companies Moving forward: what semiconductor 04 companies must consider today Going vertical: A new integration era in the semiconductor industry 2 Executive overview Like many industries, the semiconductor industry is not immune to waves of diversification and consolidation through inorganic and organic growth. While inflection points with large-scale systemic changes in the value chain are relatively rare, our perspective is that there is a systemic change currently trending in the industry. Since the inception of the industry, semiconductor companies have recognized the value of technology. Accordingly, the market has rewarded semiconductor companies for specializing in distinct parts of the value chain by developing technological advantages by investing in R&D and by scaling technology through horizontal integration. This way of working transformed an industry that was initially vertically integrated (semiconductor design, semiconductor manufacturing, and system integration) into an ecosystem focused on specific areas of design, manufacturing, and/or systems. In the past five years, business value in some segments has moved from underlying technology to specific use cases to better monetize end-customer data and experience. • 5G, automotive, AI, cloud, system integration and hardware-software integration System integrators and software and cloud platform companies are no longer just important customers for the semiconductor industry—they are directly expanding into multiple upstream areas. • Taking advantage of silicon and system design • Control more of the technology stack • Optimize system performance • Improve the customer experience This vertical integration trend is distinctly different from the vertical integration which occurred at the inception of the semiconductor and integrated device manufacturing industry more than 50 years ago. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

A Vhdl-Based Digital Slot Machine Implementation Using A

A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE by Lucas C. Pascute Submitted in Partial Fulfillment ofthe Requirements for the Degree of Master ofScience ofEngineering in the Electrical Engineering Program YOUNGSTOWN STATE UNIVERSITY December, 2002 A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE Lucas C. Pascute I hereby release this thesis to the public. I understand that this thesis will be made available from the OhioLINK ETD Center and the Maag Library Circulation Desk for public access. I also authorize the University or other individuals to make copies ofthis thesis as needed for scholarly research. Signature: ;/ (' , p ~-~_.._--- c:;.--_. ~ ~b IZ-3-Cl7., Lucas C. Pascute, Student Date Approvals: r. Faramarz Mossayebi, Thesis Advisor 12-:}--02- Date S~?c~ /"L/ 0:5 /u C Dr. Salvatore Pansino, Committee Member Date Dr. Peter J. K: vinsky, Dean ofGradua 111 ABSTRACT The intent ofthis project is to provide an educational resource from which future students can learn the basics ofprogrammable logic and the design process involved. More specifically, the area ofinterest involves very large scale integration (VLSI) design and the advantages associated with it such as reduced chip count and development time. The methodology used within is to first implement a design; using small and medium scale integration (SSI/MSI) packages in order to have a baseline for comparison. The design is then translated for use with the very high speed integrated circuit hardware description language (VHDL) and implemented onto a complex programmable logic device (CPLD). A discussion ofthis implementation process as well as VHDL lessons is provided to serve as a tutorial for the interested reader. -

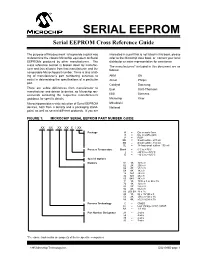

Serial EEPROM Cross Reference Guide

SERIAL EEPROM Serial EEPROM Cross Reference Guide The purpose of this document is to provide a quick way interested in a part that is not listed in this book, please to determine the closest Microchip equivalent to Serial refer to the Microchip data book, or contact your local EEPROMs produced by other manufacturers. The distributor or sales representative for assistance. cross reference section is broken down by manufac- The manufacturers* included in this document are as turer and lists all parts from that manufacturer, and the follows: comparable Microchip part number. There is also a list- ing of manufacturer’s part numbering schemes to AKM Oki assist in determining the specifications of a particular Atmel Philips part. Catalyst Samsung There are subtle differences from manufacturer to Exel SGS-Thomson manufacturer and device to device, so Microchip rec- ommends consulting the respective manufacturer’s ISSI Siemens gadabout for specific details. Microchip Xicor Microchip provides a wide selection of Serial EEPROM Mitsubishi devices, both from a density and a packaging stand- National point, as well as several different protocols. If you are FIGURE 1: MICROCHIP SERIAL EEPROM PART NUMBER GUIDE XX XX XX XX X / XX Package W = Die in wafer form S = Die in waffle pack P = PDIP SM = Small outline .207 mil SN = Small outline .150 mil SL = 14-lead small outline .150 mil Process Temperature Blank = 0°C to +70°C I = -40°C to +125°C E = -40°C to +125°C Special Options Memory 01 1K 128 x 8 02 2K 256 x 8 04 4K 512 x 8 08 8K 1K x 8 16 16K 2K x 8 32 32K 4K x 8 65 64K 8K x 8 11 1K 128K x 8 or 64 x 16 72 1K 128 x 8 82 2K 256 x 8 92 4K 512 x 8 06 256 Bit 16 x 16 46 1K 64 x 16/128 x 8 56 2K 256 x 8/128 x 16 66 4K 512 x 8/256 x 16 Process Technology C – CMOS LC – Low Voltage (2.5V) CMOS AA – 1.8 Volt Part Number Designator 24 – 2-wire 59 – 4-wire 85 – 2-wire 93 – 3-wire *The above trademarks are property of their respective companies. -

Programmable Logic Design Quick Start Handbook

00-Beginners Book front.fm Page i Wednesday, October 8, 2003 10:58 AM Programmable Logic Design Quick Start Handbook by Karen Parnell and Nick Mehta August 2003 Xilinx • i 00-Beginners Book front.fm Page ii Wednesday, October 8, 2003 10:58 AM PROGRAMMABLE LOGIC DESIGN: QUICK START HANDBOOK • © 2003, Xilinx, Inc. “Xilinx” is a registered trademark of Xilinx, Inc. Any rights not expressly granted herein are reserved. The Programmable Logic Company is a service mark of Xilinx, Inc. All terms mentioned in this book are known to be trademarks or service marks and are the property of their respective owners. Use of a term in this book should not be regarded as affecting the validity of any trade- mark or service mark. All rights reserved. No part of this book may be reproduced, in any form or by any means, without written permission from the publisher. PN 0402205 Rev. 3, 10/03 Xilinx • ii 00-Beginners Book front.fm Page iii Wednesday, October 8, 2003 10:58 AM ABSTRACT Whether you design with discrete logic, base all of your designs on micro- controllers, or simply want to learn how to use the latest and most advanced programmable logic software, you will find this book an interesting insight into a different way to design. Programmable logic devices were invented in the late 1970s and have since proved to be very popular, now one of the largest growing sectors in the semi- conductor industry. Why are programmable logic devices so widely used? Besides offering designers ultimate flexibility, programmable logic devices also provide a time-to-market advantage and design integration. -

The Birth of the Semiconductor Industry

The Birth of the Semiconductor Industry" With thanks to Angela Creager," Princeton" Image Credits" •# Most of the images in these slides came from the Computer History Museum’s online exhibit" •# http://www.computerhistory.org/semiconductor/ welcome.html" •# Also see SV Modern: Celebrating the Silicon Valley’s Mid-century Past" •# http://www.svmodern.com/index.html" Semiconductor Industry! •# An undersung hero in the history of technology" •# Amazing growth postwar" •# Large, coordinated industrial research, not madcap entrepreneurs" •# Impacts Silicon Valley, defense industry, and Moore’s law" •# Electron Tubes" –# Thermionic emission of electrons in a vacuum" •# Transistor" –# The next wave of the electronics industry" –# Based on the conductive properties (The “Fairchild Eight” Founders of the company) of semiconductors" Independent Inventors" •# A pervasive cultural mythology surrounding invention" •# Common biographies" •# Telegraphy" –# > 400 patents to individuals, 1865-1880" –# Western Union underwrites inventions though buying patents" –# WU is transcontinental in 1861, dominant by 1867" Alexander Graham Bell" •# He started inventing after reading about Western Union buying a patent for a duplex telegraph" Thomas A. Edison" •# Independents modeled themselves on him" •# Originally a telegraph operator, savvy with Wall Street and WU" •# “Invention Factory” in Menlo Park, NJ, 1876-1881" •# Invention as risky, and WU’s corporate strategy to externalize it" Industrial Labs" •# GE and Willis R. Whitney, 1900" –# MIT Chemist" –# Offered a quasi academic environment to lure talent" –# 1902: 45 scientists, budget of $15,830" –# Offers a variety of services to GE" Industrial Labs" •# Interwar Expansion" –# 1921: 1,600 company labs employ 33,000" –# 1940: 2,000 R&D departments employ 70,000" •# Bell Labs, 1925! ! - during WWII 80% of budget from were gvt contracts" Bell Labs! •# William Shockley, John Bardeen, and Walter Brattain " –# Crucial experiments (Dec. -

Psoc® 4 Is Here!

CYPRESS TOUCH-SENSING SOLUTIONS: A SUPERIOR USER EXPERIENCE Consumers are demanding elegant, sophisticated user interfaces for their home appliances, automobiles, smartphones, tablets and consumer electronics. Cypress is the No. 1 provider of capacitive touch sensing products, including our TrueTouch® and CapSense® solutions. We have shipped more than one billion capacitive touch units. Our sensing technology can be found in automobiles from Tesla to Toyota, nine of the Top 10 mobile phone suppliers, and a wide range of consumer electronics. Our newest product, the Gen5 TrueTouch controller, features patented analog sensing technology that delivers awless touch perfor- mance in the face of electronic “noise” from chargers and displays. This allows customers to create thinner mobile devices that work with any charger. Gen5 also delivers the industry’s best waterproong, along with user-friendly functionality such as activating by 2012 ANNUAL REPO R T Cypress Cypress Cypress sensing an approaching nger and tracking touches when the user is wearing a glove. ® CYPRESS AUTOMOTIVE TOUCH SOLUTIONS HIGH-PERFORMANCE SOLUTIONS 30 YEARS OF INNOVATION PSoC 4 Is Here! Semiconductor Semiconductor Semiconductor Cypress celebrated its 30th birthday on CPU SubsystemSubsystem SWD/TCSWD/TC SPCIFSPCIF December 1, 2012 with the launch of its Cortex FLASH SRAM ROM DataWire/ M0 48 MHzMHz 128 kBkB 32 kBkB 4 kBkB DMA FASTFAST MULMUL most important chip ever. ReadRead AcceleratorAccelerator SRAMSRAM ControllerController ROMROM ControllerController Initiator/MMIOInitiator/MMIO -

Introducing the 3000 Contents

INTRODUCING THE 3000 CONTENTS INTRODUCING THE SERIES 3000 BIPOLAR MICROPROCESSOR .... 3 N3001 MICROPROGRAM CONTROL UNIT ....................... 9 N3002 CENTRAL PROCESSING ELEMENT ....................... 20 S54/N74S182 HIGH SPEED LOOK-AHEAD CARRY GENERATOR .... 32 82S09 576-BIT BIPOLAR RAM (64x9) ............................ 35 82S10 1024x1 BIT BIPOLAR RAM (OPEN COLLECTOR) ........... 39 82S11 1024x1 BIT BIPOLAR RAM (TRI-STATE) .................. 39 82S25 64-BIT BIPOLAR SCRATCH PAD MEMORY (16x4 RAM) ...... 43 82S100 BIPOLAR FIELD-PROGRAMMABLE LOGIC ARRAY ......... 47 (16x8x48 FPLA)-TRI-STATE 82S101 BIPOLAR FIELD-PROGRAMMABLE LOGIC ARRAY ......... 47 (16x8x48 FPLA)-OPEN COLLECTOR 82S114 2048-BIT BIPOLAR ROM (256x8 PROM) .................. 52 82S115 4096-BIT BIPOLAR ROM (512x8 PROM) .................. 52 82S116 256-BIT BIPOLAR RAM (256x1 RAM)-TRI-STATE ........ 58 82S117 256-BIT BIPOLAR RAM (256x1 RAM)-OPEN COLLECTOR. .. 58 82S126 1024-BIT BIPOLAR PROGRAMMABLE ROM (256x4 PROM) ... 62 82S129 1024-BIT BIPOLAR PROGRAMMABLE ROM (256x4 PROM) ... 62 8T26A TRI-STATE QUAD BUS TRANSCEIVER ................ " 67 8T28 TRI-STATE QUAD BUS TRANSCEIVER .................... 67 8T31 8-BIT BIDI RECTIONAL I/O PORT ......................... 71 PACKAGE INFORMATION. .. .. .. .. .. 74 SALES OFFICE LIST ......................................... 80 1 2 INTRODUCING THE SERIES 3000 BIPOLAR MICROPROCESSOR The introduction of the Signetics Series 3000 complete 2-bit slice through the data processing Bipolar Microprocessor Chip Set has brought new section of a computer. -

Binary Addition and the Full Adder; Decoder and Encoder

KATA PENGANTAR Puji syukur kehadirat Tuhan Yang Maha Esa, akhirnya penyusunan Buku Penuntun Praktikum Elektronika Digital edisi 2018 dapat diselesaikan. Buku penuntun ini merupakan, acuan yang akan digunakan oleh praktikan yang akan melakukan Praktikum Elektronika II dan merupakan lanjutan dari Praktikum Elektronika I sebelumnya. Pada edisi ini, setiap modul mengalami penyempurnaan dari modul sebelumnya dan telah disesuaikan dengan Mata Kuliah Elektronika dan perkembangan dunia elektronika. Penambahan juga dilakukan seperti pada modul 6 – 9 yang menggunakan perangkat ZYBO™ FPGA Board dengan menggunakan VHDL sebagai bahasa pemrogramannya. Kami berharap, praktikan tidak hanya terasah kemampuannya pada sisi hardware saja namun juga pada bagian back-end (software), serta alur pemikiran konstruktifnya. Akhirnya, kami mengucapkan terima kasih kepada bapak Dr. rer. nat. Agus Salam selaku Ketua Departemen Fisika yang telah banyak men-support baik moril maupun materil hingga penyusunan buku ini dapat terlaksana dengan baik. Buku Penuntun Praktikum ini jauh dari kata sempurna, maka saran dan kritik yang membangun selalu kami nantikan demi penyempurnaan dan perkembangan kita semua. Buku ini kami persembahkan secara special kepada Departemen Fisika UI, semoga dapat bermanfaat. Amin. Depok, 1 Maret 2018 Sastra Kusuma Wijaya, Ph.D Dian Wulan Hastuti, S.Si Affan Hifzhi, S.Si Rizki Arif Lab. Elektronika, Dept. Fisika, FMIPA UI © 2018 1 DAFTAR ISI Kata Pengantar ........................................................................................................................................ -

基于 Arm ® Cortex® -M 的 微控制器产品方案介绍

基于 Arm® Cortex® -M 的 微控制器产品方案介绍 Wei Wang September 2018 | APF-TRD-T3275 Company External – NXP, the NXP logo, and NXP secure connections for a smarter world are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2018 NXP B.V. Agenda • 通用市场新产品概览 • 专用市场新产品概览 • 跨界处理器 • 一站式开发工具和方案 • 参考设计和方案 • 物联网开发平台 • i.MX RT • Kinetis, DSC, S08 • LPC • 无线连接 – JN/QN/KW PUBLIC 1 关注 NXP 官方公众号和 MCU 技术公众号 NXP客栈 恩智浦MCU加油站 PUBLIC 2 HOME ETHERNET GATEWAY SWITCH Cloud Infrastructure NXP Cloud Software Platform built on top of leading cloud partners (e.g. Azure, AWS, GCP, Alibaba, Baidu, etc.) WIRELESS INDUSTRIAL ROUTER CONTROLLER Customer Solution App App App Provisioning & Authentication Middleware Data Analytics RTOS, Linux, Android … Services foundation NXP SW Platform Machine Learning PUBLIC 3 面向 AI-IOT 的可扩展处理器平台 M4 – A53 – A72 4K HEVC M4 - A53 128 GFLOPS GPU 4K HDR - Dolby A7 64GFLOPS GPU LX2160 CSI - LCD LS 2088 16xA72 M4 – A35 LS1046 280 GFlops 4K i.MX 8 8xA72 100 Gbps 28GFLOPS GPU LS1043 i.MX 8M 128 GFlops 40 Gbps i.MX 8X LS 1012 4xA72 58 GFlops i.MX 6UL/ULL/ULZ 4xA53 20 Gbps i.MX RT i.MX 7ULP 50 GFlops Performance 1xA53 10 Gbps 12 GFlops M4 + Connectivity 2 Gbps Secure Boot Crypto accel K4 LPC QN, JN M7 @ 600 MHz QSPI Secure Boot Multimedia Acceleration Networking Acceleration Integration PUBLIC 4 可扩展的嵌入式 AI-IOT “云管端”平台 Voice Gesture Active Object Personal / Home Multi-stream Multi-camera Augmented Processing Control Recognition Property Environment Camera Observation Reality & 360 view Low-end Edge Compute