Chapter 20 Signal Integrity

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Modeling System Signal Integrity Uncertainty Considerations

WHITE PAPER Intel® FPGA Modeling System Signal Integrity Uncertainty Considerations Authors Abstract Ravindra Gali This white paper describes signal integrity (SI) mechanisms that cause system-level High-Speed I/O Applications timing uncertainty and how these mechanisms are modeled in the Intel® Quartus® Engineering, Intel® Corporation Prime software Timing Analyzer to achieve timing closure for external memory interface designs. Zhi Wong By using the Intel Quartus Prime software to achieve timing closure for external High-Speed I/O Applications memory interfaces, a designer does not need to allocate a separate SI timing Engineering, Intel Corporation budget to account for simultaneous switching output (SSO), simultaneous Navid Azizi switching input (SSI), intersymbol interference (ISI), and board-level crosstalk for Software Engineeringr flip-chip device families such as Stratix® IV and Arria® II FPGAs for typical user Intel Corporation implementation of external memory interfaces following good board design practices. John Oh High-Speed I/O Applications Introduction Engineering, Intel Corporation The widening performance gap between FPGAs, microprocessors, and memory Arun VR devices, along with the growth of memory-intensive applications, are driving the Memory I/O Applications Engineering, need for faster memory technologies. This push to higher bandwidths has been Intel Corporation accompanied by an increase in the signal count and the signaling rates of FPGAs and memory devices. In order to attain faster bandwidths, device makers continue to reduce the supply voltage. Initially, industry-standard DIMMs operated at 5 V. However, due to improvements in DRAM storage density, the operating voltage was decreased to 3.3 V (SDR), then to 2.5V (DDR), 1.8 V (DDR2), 1.5 V (DDR3), and 1.35 V (DDR3) to allow the memory to run faster and consume less power. -

A Vhsic Hardware Description Language Compiler for Logic Cell Arrays

A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS by Bing Liu A thesis presented to the university of Mânitoba in partial fulfillment of úe requirements of the degree of Maste¡ of Science in Elecrical and Computel Engineering Winnipeg, Manitoba, Canada @ Bing Liu, January 1990 Bibliothèque nat¡onale rE fr"3""i"i;tjo'",' du Canada Canadian Theses Serv¡ce Service des thèses canadiennes Otta'¿/ã. Can¿da Kl A ON¡ The author has granted an inevocable non' L'auteur a accordé une licence iffévocable et exclusive licence allowing the National Library non exclusive permettant à h Bibliothèque of Canada to reproduce, loan, distribute or sell nationale du Canada.de reproduire, prêter, copies of his/her thesis by any means and in distribuer ou vendre des copies de sa thèse any form or format, making this thesis avaihble de quelque manière et sous quelque forme to ¡nterested persons. que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées. The author retains ownership of the copyright L auteur conserve la propriété du droit d'auteur in his/her thesis. Neither the thesis nor qui protà?e sa thèse. Ni la thèse ni des extraits substantial extracts from it may be printed or substantiels de celle-ci ne doivent être otherw¡se reproduced without his/her per' imprimés ou autrement reproduits sans son mission. autorisation. ISBN ø-315-7 r7s t -3 Canadä A VHSIC HARDWARE DESCRIPTION I.ANGUAGE COMPILER FOR LOG]C CEI,L ARRAYS BY BING LIU A thesis subnrined lo thc Fact¡lty of Crâduate Studies of the University of M¿nitoba in partial fulfìllment of the requirenrents of the degree of MASTM O¡' SC]MICE o 1990 Permission has becn granted to the L¡BRÁRY OF THE UNIVER' SITY OF MANITOBA to lend o¡ sell copies of tlt¡s thesis. -

The Printed Circuit Designer's Guide To... Signal Integrity by Example

PEER REVIEWERS This book has been reviewed for technical accuracy by the following experts from the PCB industry. Happy Holden Consulting Technical Editor, I-Connect007 Happy Holden is the retired director of electronics and innovations for Gentex Corporation. Happy is the former chief technical officer for the world’s largest PCB fabricator, Hon Hai Precision Industries (Foxconn). Prior to Foxconn, Holden was the senior PCB technologist for Mentor Graphics and advanced technology manager at Nan Ya/ Westwood Associates and Merix. Happy previously worked at Hewlett-Packard for over 28 years as director of PCB R&D and manufacturing engineering manager. He has been involved in advanced PCB technologies for over 47 years. Eric Bogatin Eric Bogatin is currently the dean of the Teledyne LeCroy Signal Integrity Academy. Additionally, he is an adjunct professor at the University of Colorado- Boulder in the ECEE department, where he teaches a graduate class in signal integrity and is also the editor of Signal Integrity Journal. Bogatin received his BS in physics from MIT, and MS and PhD in physics from the University of Arizona in Tucson. Eric has held senior engineering and management positions at Bell Labs, Raychem, Sun Microsystems, Ansoft and Interconnect Devices. Bogatin has written six technical books in the field, and presented classes and lectures on signal integrity worldwide. MEET THE AUTHOR Fadi Deek Signal/Power Integrity Specialist Corporate Application Engineer In 2005, Fadi received his B.S. degree in computer and communications from the American University of Science and Technology (AUST) in Beirut, Lebanon. That same year, he joined Fidus Systems as a design engineer. -

Going Vertical: a New Integration Era in the Semiconductor Industry Table of Contents

Going vertical: A new integration era in the semiconductor industry Table of contents 01 Executive overview Integration in the 02 semiconductor industry Strategic options for 03 semiconductor companies Moving forward: what semiconductor 04 companies must consider today Going vertical: A new integration era in the semiconductor industry 2 Executive overview Like many industries, the semiconductor industry is not immune to waves of diversification and consolidation through inorganic and organic growth. While inflection points with large-scale systemic changes in the value chain are relatively rare, our perspective is that there is a systemic change currently trending in the industry. Since the inception of the industry, semiconductor companies have recognized the value of technology. Accordingly, the market has rewarded semiconductor companies for specializing in distinct parts of the value chain by developing technological advantages by investing in R&D and by scaling technology through horizontal integration. This way of working transformed an industry that was initially vertically integrated (semiconductor design, semiconductor manufacturing, and system integration) into an ecosystem focused on specific areas of design, manufacturing, and/or systems. In the past five years, business value in some segments has moved from underlying technology to specific use cases to better monetize end-customer data and experience. • 5G, automotive, AI, cloud, system integration and hardware-software integration System integrators and software and cloud platform companies are no longer just important customers for the semiconductor industry—they are directly expanding into multiple upstream areas. • Taking advantage of silicon and system design • Control more of the technology stack • Optimize system performance • Improve the customer experience This vertical integration trend is distinctly different from the vertical integration which occurred at the inception of the semiconductor and integrated device manufacturing industry more than 50 years ago. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

A Vhdl-Based Digital Slot Machine Implementation Using A

A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE by Lucas C. Pascute Submitted in Partial Fulfillment ofthe Requirements for the Degree of Master ofScience ofEngineering in the Electrical Engineering Program YOUNGSTOWN STATE UNIVERSITY December, 2002 A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE Lucas C. Pascute I hereby release this thesis to the public. I understand that this thesis will be made available from the OhioLINK ETD Center and the Maag Library Circulation Desk for public access. I also authorize the University or other individuals to make copies ofthis thesis as needed for scholarly research. Signature: ;/ (' , p ~-~_.._--- c:;.--_. ~ ~b IZ-3-Cl7., Lucas C. Pascute, Student Date Approvals: r. Faramarz Mossayebi, Thesis Advisor 12-:}--02- Date S~?c~ /"L/ 0:5 /u C Dr. Salvatore Pansino, Committee Member Date Dr. Peter J. K: vinsky, Dean ofGradua 111 ABSTRACT The intent ofthis project is to provide an educational resource from which future students can learn the basics ofprogrammable logic and the design process involved. More specifically, the area ofinterest involves very large scale integration (VLSI) design and the advantages associated with it such as reduced chip count and development time. The methodology used within is to first implement a design; using small and medium scale integration (SSI/MSI) packages in order to have a baseline for comparison. The design is then translated for use with the very high speed integrated circuit hardware description language (VHDL) and implemented onto a complex programmable logic device (CPLD). A discussion ofthis implementation process as well as VHDL lessons is provided to serve as a tutorial for the interested reader. -

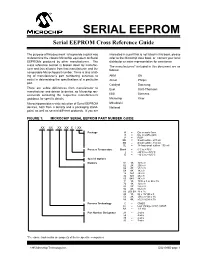

Serial EEPROM Cross Reference Guide

SERIAL EEPROM Serial EEPROM Cross Reference Guide The purpose of this document is to provide a quick way interested in a part that is not listed in this book, please to determine the closest Microchip equivalent to Serial refer to the Microchip data book, or contact your local EEPROMs produced by other manufacturers. The distributor or sales representative for assistance. cross reference section is broken down by manufac- The manufacturers* included in this document are as turer and lists all parts from that manufacturer, and the follows: comparable Microchip part number. There is also a list- ing of manufacturer’s part numbering schemes to AKM Oki assist in determining the specifications of a particular Atmel Philips part. Catalyst Samsung There are subtle differences from manufacturer to Exel SGS-Thomson manufacturer and device to device, so Microchip rec- ommends consulting the respective manufacturer’s ISSI Siemens gadabout for specific details. Microchip Xicor Microchip provides a wide selection of Serial EEPROM Mitsubishi devices, both from a density and a packaging stand- National point, as well as several different protocols. If you are FIGURE 1: MICROCHIP SERIAL EEPROM PART NUMBER GUIDE XX XX XX XX X / XX Package W = Die in wafer form S = Die in waffle pack P = PDIP SM = Small outline .207 mil SN = Small outline .150 mil SL = 14-lead small outline .150 mil Process Temperature Blank = 0°C to +70°C I = -40°C to +125°C E = -40°C to +125°C Special Options Memory 01 1K 128 x 8 02 2K 256 x 8 04 4K 512 x 8 08 8K 1K x 8 16 16K 2K x 8 32 32K 4K x 8 65 64K 8K x 8 11 1K 128K x 8 or 64 x 16 72 1K 128 x 8 82 2K 256 x 8 92 4K 512 x 8 06 256 Bit 16 x 16 46 1K 64 x 16/128 x 8 56 2K 256 x 8/128 x 16 66 4K 512 x 8/256 x 16 Process Technology C – CMOS LC – Low Voltage (2.5V) CMOS AA – 1.8 Volt Part Number Designator 24 – 2-wire 59 – 4-wire 85 – 2-wire 93 – 3-wire *The above trademarks are property of their respective companies. -

High Speed Signal Integrity Analysis and Differential Signaling

High Speed Signal Integrity Analysis and Differential Signaling Project Report of EE201C: Modeling of VLSI Circuits and Systems Tongtong Yu, UID: 904025158 Zhiyuan Shen, UID: 803987916 Abstract— This course project is designated for independent electric mechanism of semiconductor circuit doesn’t change study of various topics relating to VLSI modeling. In our very much, so the concentration is on the interconnects and project, the first part is an extension of the class presentation packaging. where we introduced the basic idea of signal integrity. Here we address the philosophy behind frequency domain and time The impact of to the system can be classified to signal domain. Then, we give two examples of interconnects, a critical integrity, which refers to the contamination of signal’s in- issue related to signal integrity. The second part is about tegrity due to parasitic effects of interconnects and packaging, differential signaling used in high speed application. After compared with ideal case. This may result in unsatisfactory analyzing general principles, we simulate two parallel-trace performance. For example, we design the systems for 10Gbps; transmission line, which has practical meaning in real design case. Maybe this project is not fancy, but we believe all the however, due to this effect, it can only achieve 5Gbps. Also, fundamentals provided here and those reference list in the end this may produce inaccurate logic state and even logical are the best material for everyone who wants to go further in failure. This impact can be classified in two ways this area. 1) Delay, distortion and cross-talk directly happening on We would like to express our deepest gratitude to Prof. -

Signal Integrity Analysis and Simulation Tools Include IBIS Models

High Frequency Products From September 2004 High Frequency Electronics Copyright ® 2004 Summit Technical Media, LLC HIGH-SPEED MODELS Signal Integrity Analysis and Simulation Tools Include IBIS Models By John Olah and Sanjeev Gupta, Agilent EEsof EDA, and Carlos Chavez-Dagostino, Altera Corporation ignal integrity is a several hybrid-domain simulation techniques, This issue’s cover highlights major concern for where the simulator is conversant in both the introduction of Agilent Sengineers working time and frequency domain and can combine Technologies’ ADS2004A, on high data rate designs. models suitable for either domain. This article which now includes Effects such as crosstalk, describes the types of models that need to be greatly enhanced capa- coupling and delays in taken together for high-speed signal integrity bilities for signal integrity transmission lines have a analysis, and illustrates their use in a simula- modeling in both time big impact on signal tion of a high-speed memory circuit. and frequency domains integrity. High-speed dig- ital board designers can Requirements for High-Speed now use design tools that combine time- Signal Integrity Simulations domain IC-specific I/O Buffer Information In broad terms, there are three important Specification (IBIS) models with accurate simulation requirements for analog high- transmission line models to get a better speed signal integrity characterization: understanding of the signal distortion due to coupling and delays. 1. A hybrid-domain simulator that handles time-domain and frequency-domain models Introduction 2. Accurate transmission line structures (best In terms of analog simulators, historically, described in the frequency-domain) there have been two main camps; time- 3. -

Programmable Logic Design Quick Start Handbook

00-Beginners Book front.fm Page i Wednesday, October 8, 2003 10:58 AM Programmable Logic Design Quick Start Handbook by Karen Parnell and Nick Mehta August 2003 Xilinx • i 00-Beginners Book front.fm Page ii Wednesday, October 8, 2003 10:58 AM PROGRAMMABLE LOGIC DESIGN: QUICK START HANDBOOK • © 2003, Xilinx, Inc. “Xilinx” is a registered trademark of Xilinx, Inc. Any rights not expressly granted herein are reserved. The Programmable Logic Company is a service mark of Xilinx, Inc. All terms mentioned in this book are known to be trademarks or service marks and are the property of their respective owners. Use of a term in this book should not be regarded as affecting the validity of any trade- mark or service mark. All rights reserved. No part of this book may be reproduced, in any form or by any means, without written permission from the publisher. PN 0402205 Rev. 3, 10/03 Xilinx • ii 00-Beginners Book front.fm Page iii Wednesday, October 8, 2003 10:58 AM ABSTRACT Whether you design with discrete logic, base all of your designs on micro- controllers, or simply want to learn how to use the latest and most advanced programmable logic software, you will find this book an interesting insight into a different way to design. Programmable logic devices were invented in the late 1970s and have since proved to be very popular, now one of the largest growing sectors in the semi- conductor industry. Why are programmable logic devices so widely used? Besides offering designers ultimate flexibility, programmable logic devices also provide a time-to-market advantage and design integration. -

10 Ways ADS Overcomes Signal and Power Integrity Challenges

Keysight Technologies 10 Ways ADS Overcomes Signal and Power Integrity Challenges Technical Overview 02 | Keysight | 8 Ways ADS Overcomes Signal and Power Integrity Challenges - Technical Overview Keysight EEsof EDA’s Advanced Design System (ADS) software is the world’s leading electronic design automation solution for RF, microwave, and high-speed digital applications. ADS features a host of new, technologies designed to improve productivity, including two electromagnetic (EM) software solutions specifically created to help signal and power integrity engineers improve high-speed link performance in PCB designs. What follows is a listing of 8 ways in which ASD can help you, the engineer, overcome your signal and power integrity challenges. 1. ADS provides speed and accuracy for your SI EM characterization ........................Page 2 2. ADS simplifies the use of S-parameter files for your parts .......................................Page 4 3. ADS provides access to industry-leading channel simulator technology ...................................................................................................Page 6 4. ADS stays ahead of technology waves (such as PAM-4) ..........................................Page 9 5. ADS accelerates DDR4 simulation methodologies ....................................................Page 12 6. ADS puts power in the hands of designers (PI analyses) ..........................................Page 15 7. ADS enables flat PDN impedance responses ............................................................Page