Binary Addition and the Full Adder; Decoder and Encoder

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Digital Electronic Circuits

DIGITAL ELECTRONIC CIRCUITS SUBJECT CODE: PEI4I103 B.Tech, Fourth Semester Prepared By Dr. Kanhu Charan Bhuyan Asst. Professor Instrumentation and Electronics Engineering COLLEGE OF ENGINEERING AND TECHNOLOGY BHUBANESWAR B.Tech (E&IE/AE&I) detail Syllabus for Admission Batch 2015-16 PEI4I103- DIGITAL ELECTRONICS University level 80% MODULE – I (12 Hours)1. Number System: Introduction to various number systems and their Conversion. Arithmetic Operation using 1’s and 2`s Compliments, Signed Binary and Floating Point Number Representation Introduction to Binary codes and their applications. (5 Hours) 2. Boolean Algebra and Logic Gates: Boolean algebra and identities, Complete Logic set, logic gates and truth tables. Universal logic gates, Algebraic Reduction and realization using logic gates (3 Hours) 3. Combinational Logic Design: Specifying the Problem, Canonical Logic Forms, Extracting Canonical Forms, EX-OR Equivalence Operations, Logic Array, K-Maps: Two, Three and Four variable K-maps, NAND and NOR Logic Implementations. (4 Hours) MODULE – II (14 Hours) 4. Logic Components: Concept of Digital Components, Binary Adders, Subtraction and Multiplication, An Equality Detector and comparator, Line Decoder, encoders, Multiplexers and De-multiplexers. (5 Hours) 5. Synchronous Sequential logic Design: sequential circuits, storage elements: Latches (SR,D), Storage elements: Flip-Flops inclusion of Master-Slave, characteristics equation and state diagram of each FFs and Conversion of Flip-Flops. Analysis of Clocked Sequential circuits and Mealy and Moore Models of Finite State Machines (6 Hours) 6. Binary Counters: Introduction, Principle and design of synchronous and asynchronous counters, Design of MOD-N counters, Ring counters. Decade counters, State Diagram of binary counters (4 hours) MODULE – III (12 hours) 7. -

A Vhsic Hardware Description Language Compiler for Logic Cell Arrays

A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS by Bing Liu A thesis presented to the university of Mânitoba in partial fulfillment of úe requirements of the degree of Maste¡ of Science in Elecrical and Computel Engineering Winnipeg, Manitoba, Canada @ Bing Liu, January 1990 Bibliothèque nat¡onale rE fr"3""i"i;tjo'",' du Canada Canadian Theses Serv¡ce Service des thèses canadiennes Otta'¿/ã. Can¿da Kl A ON¡ The author has granted an inevocable non' L'auteur a accordé une licence iffévocable et exclusive licence allowing the National Library non exclusive permettant à h Bibliothèque of Canada to reproduce, loan, distribute or sell nationale du Canada.de reproduire, prêter, copies of his/her thesis by any means and in distribuer ou vendre des copies de sa thèse any form or format, making this thesis avaihble de quelque manière et sous quelque forme to ¡nterested persons. que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées. The author retains ownership of the copyright L auteur conserve la propriété du droit d'auteur in his/her thesis. Neither the thesis nor qui protà?e sa thèse. Ni la thèse ni des extraits substantial extracts from it may be printed or substantiels de celle-ci ne doivent être otherw¡se reproduced without his/her per' imprimés ou autrement reproduits sans son mission. autorisation. ISBN ø-315-7 r7s t -3 Canadä A VHSIC HARDWARE DESCRIPTION I.ANGUAGE COMPILER FOR LOG]C CEI,L ARRAYS BY BING LIU A thesis subnrined lo thc Fact¡lty of Crâduate Studies of the University of M¿nitoba in partial fulfìllment of the requirenrents of the degree of MASTM O¡' SC]MICE o 1990 Permission has becn granted to the L¡BRÁRY OF THE UNIVER' SITY OF MANITOBA to lend o¡ sell copies of tlt¡s thesis. -

Going Vertical: a New Integration Era in the Semiconductor Industry Table of Contents

Going vertical: A new integration era in the semiconductor industry Table of contents 01 Executive overview Integration in the 02 semiconductor industry Strategic options for 03 semiconductor companies Moving forward: what semiconductor 04 companies must consider today Going vertical: A new integration era in the semiconductor industry 2 Executive overview Like many industries, the semiconductor industry is not immune to waves of diversification and consolidation through inorganic and organic growth. While inflection points with large-scale systemic changes in the value chain are relatively rare, our perspective is that there is a systemic change currently trending in the industry. Since the inception of the industry, semiconductor companies have recognized the value of technology. Accordingly, the market has rewarded semiconductor companies for specializing in distinct parts of the value chain by developing technological advantages by investing in R&D and by scaling technology through horizontal integration. This way of working transformed an industry that was initially vertically integrated (semiconductor design, semiconductor manufacturing, and system integration) into an ecosystem focused on specific areas of design, manufacturing, and/or systems. In the past five years, business value in some segments has moved from underlying technology to specific use cases to better monetize end-customer data and experience. • 5G, automotive, AI, cloud, system integration and hardware-software integration System integrators and software and cloud platform companies are no longer just important customers for the semiconductor industry—they are directly expanding into multiple upstream areas. • Taking advantage of silicon and system design • Control more of the technology stack • Optimize system performance • Improve the customer experience This vertical integration trend is distinctly different from the vertical integration which occurred at the inception of the semiconductor and integrated device manufacturing industry more than 50 years ago. -

EE 2008 Fall 2008 EE 231 Exam 3 November 19, 2008 Name: Show All Work. Partial Credit Will Be Given. No Credit Will Be Given If

EE 2008 Fall 2008 EE 231 Exam 3 November 19, 2008 Name: Show all work. Partial credit will be given. No credit will be given if an answer appears with no supporting work. 1. Circle the correct answer to questions (a) through (i); give a numerical answer for (j) and (k): (a) A movement of data from right (least significant bit) to left (most significant bit) is what type of shift: A. Right B. Left C. Parallel D. Finite state machine (b) A serial shift register with non-complemented feedback from the output of the last flip-flop to the input of the first is called a: A. Binary Counter B. Gray Code Counter C. Johnson Counter D. Ring Counter (c) A finite state machine in which the output depends on the present state and the present inputs is called a: A. Mealy machine B. Mannie machine C. Moore machine D. Vending machine (d) A finite state machine in which the output depends only on the present state is called a: A. Mealy machine B. Mannie machine C. Moore machine D. Vending machine VCC Q VCC (e) The circuit shown above is used for what purpose? A. Counter B. Pulser C. Shift register D. Switch debounce (f) The multiplexer is an example of what type of Boolean circuit? A. Sequential B. Combinational C. Moore machine D. Analog (g) Which sequential device has an output that is only dependent on the level of the inputs? A. Latch B. Multiplexer C. Flip-Flop D. Clock Tree 1 EE 2008 Fall 2008 module ex3 (input clock, clear, load, x, output reg y) always @(posedge clock, negedge clear) if (clear == 1’b0) y <= 0; else if (load == 1’b0) y <= x; else y <= y; endmodule (h) For the Verilog code above, what type on input is clear? A. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

Laboratory Sequence Circuits

Laboratory Sequence Circuits Digital Design IE1204/5 Attention! To access the laboratory experiment you must have: • booked a lab time in the reservation system (Daisy). • completed your personal knowledge control on the Web (Web-quiz). • done all preparation tasks mentioned in the lab booklet. If a preparation task has this "label", you must also be prepared to to present an oral solution for your peers at the lab. During the lab you work in groups of two, but both students are responsible individually for their preparation and implementation. Booth students should bring their lab booklets. This frontpage is used as your receipt that the lab is completed. Save the receipt until you have received the full course registered in the database (Ladok). Since this is your receipt you must fill in the table with ink. 1 Introduction This lab is about sequence circuits in synchronously clocked applications. We continue to use standard CMOS circuits. It's the CMOS technology that has enabled extremely low-power battery-operated portable devices. CMOS gates only consume power at the clock pulse edges! (In the lab equipment it is the LEDs that are the big "power consumers"). On the breadboard you will connect and measure some basic sequence circuits like latches and clocked D flip-flops. With a systematic method you construct a state machine, a controlled counter, which you then test in the laboratory. Other sequence circuits with simple structure, such as feedback shift registers, can often be examined directly. The task will be to "control" such a sequence circuit to run through various cycles. -

Final-Del-Lab-Manual-2018-19

LAB MANUAL DIGITAL ELECTRONICS LABORATORY Subject Code: 210246 2018 - 19 INDEX Batch : - Page Date of Date of Signature of Sr.No Title No Conduction Submission Staff GROUP - A Realize Full Adder and Subtractor using 1 a) Basic Gates and b) Universal Gates Design and implement Code converters-Binary to Gray and BCD to 2 Excess-3 Design of n-bit Carry Save Adder (CSA) and Carry Propagation Adder (CPA). Design and Realization of BCD 3 Adder using 4-bit Binary Adder (IC 7483). Realization of Boolean Expression for suitable combination logic using MUX 4 74151 / DMUX 74154 Verify the truth table of one bit and two bit comparators using logic gates and 5 comparator IC Design & Implement Parity Generator 6 using EX-OR. GROUP - B Flip Flop Conversion: Design and 7 Realization Design of Ripple Counter using suitable 8 Flip Flops a. Realization of 3 bit Up/Down Counter using MS JK Flip Flop / D-FF 9 b. Realization of Mod -N counter using ( 7490 and 74193 ) Design and Realization of Ring Counter 10 and Johnson Ring counter Design and implement Sequence 11 generator using JK flip-flop INDEX Batch : - Design and implement pseudo random 12 sequence generator. Design and implement Sequence 13 detector using JK flip-flop Design of ASM chart using MUX 14 controller Method. GROUP - C Design and Implementation of 15 Combinational Logic using PLAs. Design and simulation of - Full adder , 16 Flip flop, MUX using VHDL (Any 2) Use different modeling styles. Design & simulate asynchronous 3- bit 17 counter using VHDL. Design and Implementation of 18 Combinational Logic using PALs GROUP - D Study of Shift Registers ( SISO,SIPO, 19 PISO,PIPO ) Study of TTL Logic Family: Feature, 20 Characteristics and Comparison with CMOS Family Study of Microcontroller 8051 : 21 Features, Architecture and Programming Model ` Digital Electronics Lab (Pattern 2015) GROUP - A Digital Electronics Lab (Pattern 2015) Assignment: 1 Title: Adder and Subtractor Objective: 1. -

A Vhdl-Based Digital Slot Machine Implementation Using A

A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE by Lucas C. Pascute Submitted in Partial Fulfillment ofthe Requirements for the Degree of Master ofScience ofEngineering in the Electrical Engineering Program YOUNGSTOWN STATE UNIVERSITY December, 2002 A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE Lucas C. Pascute I hereby release this thesis to the public. I understand that this thesis will be made available from the OhioLINK ETD Center and the Maag Library Circulation Desk for public access. I also authorize the University or other individuals to make copies ofthis thesis as needed for scholarly research. Signature: ;/ (' , p ~-~_.._--- c:;.--_. ~ ~b IZ-3-Cl7., Lucas C. Pascute, Student Date Approvals: r. Faramarz Mossayebi, Thesis Advisor 12-:}--02- Date S~?c~ /"L/ 0:5 /u C Dr. Salvatore Pansino, Committee Member Date Dr. Peter J. K: vinsky, Dean ofGradua 111 ABSTRACT The intent ofthis project is to provide an educational resource from which future students can learn the basics ofprogrammable logic and the design process involved. More specifically, the area ofinterest involves very large scale integration (VLSI) design and the advantages associated with it such as reduced chip count and development time. The methodology used within is to first implement a design; using small and medium scale integration (SSI/MSI) packages in order to have a baseline for comparison. The design is then translated for use with the very high speed integrated circuit hardware description language (VHDL) and implemented onto a complex programmable logic device (CPLD). A discussion ofthis implementation process as well as VHDL lessons is provided to serve as a tutorial for the interested reader. -

Serial EEPROM Cross Reference Guide

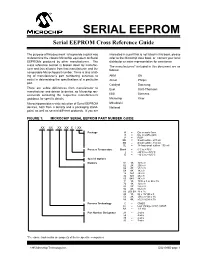

SERIAL EEPROM Serial EEPROM Cross Reference Guide The purpose of this document is to provide a quick way interested in a part that is not listed in this book, please to determine the closest Microchip equivalent to Serial refer to the Microchip data book, or contact your local EEPROMs produced by other manufacturers. The distributor or sales representative for assistance. cross reference section is broken down by manufac- The manufacturers* included in this document are as turer and lists all parts from that manufacturer, and the follows: comparable Microchip part number. There is also a list- ing of manufacturer’s part numbering schemes to AKM Oki assist in determining the specifications of a particular Atmel Philips part. Catalyst Samsung There are subtle differences from manufacturer to Exel SGS-Thomson manufacturer and device to device, so Microchip rec- ommends consulting the respective manufacturer’s ISSI Siemens gadabout for specific details. Microchip Xicor Microchip provides a wide selection of Serial EEPROM Mitsubishi devices, both from a density and a packaging stand- National point, as well as several different protocols. If you are FIGURE 1: MICROCHIP SERIAL EEPROM PART NUMBER GUIDE XX XX XX XX X / XX Package W = Die in wafer form S = Die in waffle pack P = PDIP SM = Small outline .207 mil SN = Small outline .150 mil SL = 14-lead small outline .150 mil Process Temperature Blank = 0°C to +70°C I = -40°C to +125°C E = -40°C to +125°C Special Options Memory 01 1K 128 x 8 02 2K 256 x 8 04 4K 512 x 8 08 8K 1K x 8 16 16K 2K x 8 32 32K 4K x 8 65 64K 8K x 8 11 1K 128K x 8 or 64 x 16 72 1K 128 x 8 82 2K 256 x 8 92 4K 512 x 8 06 256 Bit 16 x 16 46 1K 64 x 16/128 x 8 56 2K 256 x 8/128 x 16 66 4K 512 x 8/256 x 16 Process Technology C – CMOS LC – Low Voltage (2.5V) CMOS AA – 1.8 Volt Part Number Designator 24 – 2-wire 59 – 4-wire 85 – 2-wire 93 – 3-wire *The above trademarks are property of their respective companies. -

Draft Chapter on the ENIAC Circuits

CHAPTER 1 CIRCUITS Section 1. Vacuum Tube Basics 1. Introduction During the 1940s, when the ENIAC was under construction, the basic principles of vacuum tubes and their circuits were familiar to most electrical engineers. Today, however, that knowledge is far less common. For that reason, we begin our discussion of the circuit design of the ENIAC with a brief look at how vacuum tubes work and how they are used as switching elements in circuits. Conversely, the reader is expected to be somewhat familiar with the functions of other circuit components, especially resistors and capacitors. 2. Tube Structure As the name implies a vacuum tube operates in a vacuum. This allows the electrons (e−) to flow freely between the electrodes in the tube without being impeded by gas molocules. That vacuum is usually contained in a glass envelope, though sometimes we find them in metal cans. These devices contain at least two electrodes, and those that are used in logic circuits that we study here all have at least three. a. Cathode. The cathode is the electrode from which the electrons origi- nate. To cause it to give off electrons, its temperature is raised with a heater. In some tubes the heater is the cathode, but for the tubes used in the logic of the ENIAC, the heater is inside a small metal can. This can is coated with a mixture of oxides, such as those of barium and strontium, that efficiently emit electrons at lower temperatures than the heater itself. b. Plate. The plate (or sometimes anode) is physically designed as a metal can surrounding the cathode with some free space between them. -

Design and Implementation of an On-Chip Test Generation Scheme

Available online at www.sciencedirect.com ScienceDirect Procedia Computer Science 46 ( 2015 ) 1409 – 1416 International Conference on Information and Communication Technologies (ICICT 2014) Design and Implementation of an On-Chip Test Generation Scheme Based on Reconfigurable Run-Time Programmable and Multiple Twisted-Ring Counters Aida S Tharakana*, Binu K Mathewb a,bDept. of Electronics and Communication, Saintgits College of Engineering, Kottayam-686532, India Abstract Built-in-self-test (BIST) has emerged as a very effective solution to VLSI testing problems. Related work based on single fixed- order twisted-ring-counter design requires longer testing time to achieve high fault coverage and large storage space to store the seeds and the control data. By using multiple programmable twisted-ring-counters (PTRC), a considerable reduction in test application cycles were achieved. In this paper, an on-chip test generation scheme based on reconfigurable run-time programmable multiple twisted-ring-counters is proposed to generate more number of different test patterns based on the requirements. The design was modeled in VHDL and simulated and synthesized using Xilinx ISE 14.2. ©© 2015 2014 The The Authors. Authors. Published Published by by Elsevier Elsevier B.V. B.V. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/). Peer-review under responsibility of organizing committee of the International Conference on Information and Communication Peer-review under responsibility of organizing committee of the International Conference on Information and Communication Technologies (ICICT 2014). Technologies (ICICT 2014) Keywords: Fault Coverage;Logic BIST;Reconfiguration;Twisted-ring-counters 1.