Digital Beamforming Implementation on an FPGA Platform (Projecte Fi De Carrera)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Vhsic Hardware Description Language Compiler for Logic Cell Arrays

A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS by Bing Liu A thesis presented to the university of Mânitoba in partial fulfillment of úe requirements of the degree of Maste¡ of Science in Elecrical and Computel Engineering Winnipeg, Manitoba, Canada @ Bing Liu, January 1990 Bibliothèque nat¡onale rE fr"3""i"i;tjo'",' du Canada Canadian Theses Serv¡ce Service des thèses canadiennes Otta'¿/ã. Can¿da Kl A ON¡ The author has granted an inevocable non' L'auteur a accordé une licence iffévocable et exclusive licence allowing the National Library non exclusive permettant à h Bibliothèque of Canada to reproduce, loan, distribute or sell nationale du Canada.de reproduire, prêter, copies of his/her thesis by any means and in distribuer ou vendre des copies de sa thèse any form or format, making this thesis avaihble de quelque manière et sous quelque forme to ¡nterested persons. que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées. The author retains ownership of the copyright L auteur conserve la propriété du droit d'auteur in his/her thesis. Neither the thesis nor qui protà?e sa thèse. Ni la thèse ni des extraits substantial extracts from it may be printed or substantiels de celle-ci ne doivent être otherw¡se reproduced without his/her per' imprimés ou autrement reproduits sans son mission. autorisation. ISBN ø-315-7 r7s t -3 Canadä A VHSIC HARDWARE DESCRIPTION I.ANGUAGE COMPILER FOR LOG]C CEI,L ARRAYS BY BING LIU A thesis subnrined lo thc Fact¡lty of Crâduate Studies of the University of M¿nitoba in partial fulfìllment of the requirenrents of the degree of MASTM O¡' SC]MICE o 1990 Permission has becn granted to the L¡BRÁRY OF THE UNIVER' SITY OF MANITOBA to lend o¡ sell copies of tlt¡s thesis. -

Going Vertical: a New Integration Era in the Semiconductor Industry Table of Contents

Going vertical: A new integration era in the semiconductor industry Table of contents 01 Executive overview Integration in the 02 semiconductor industry Strategic options for 03 semiconductor companies Moving forward: what semiconductor 04 companies must consider today Going vertical: A new integration era in the semiconductor industry 2 Executive overview Like many industries, the semiconductor industry is not immune to waves of diversification and consolidation through inorganic and organic growth. While inflection points with large-scale systemic changes in the value chain are relatively rare, our perspective is that there is a systemic change currently trending in the industry. Since the inception of the industry, semiconductor companies have recognized the value of technology. Accordingly, the market has rewarded semiconductor companies for specializing in distinct parts of the value chain by developing technological advantages by investing in R&D and by scaling technology through horizontal integration. This way of working transformed an industry that was initially vertically integrated (semiconductor design, semiconductor manufacturing, and system integration) into an ecosystem focused on specific areas of design, manufacturing, and/or systems. In the past five years, business value in some segments has moved from underlying technology to specific use cases to better monetize end-customer data and experience. • 5G, automotive, AI, cloud, system integration and hardware-software integration System integrators and software and cloud platform companies are no longer just important customers for the semiconductor industry—they are directly expanding into multiple upstream areas. • Taking advantage of silicon and system design • Control more of the technology stack • Optimize system performance • Improve the customer experience This vertical integration trend is distinctly different from the vertical integration which occurred at the inception of the semiconductor and integrated device manufacturing industry more than 50 years ago. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

MACABEL ABEL for the APPLE MACINTOSH Nor IIX WORKSTATION A/UX VERSION

SPECIFICATIONS MACABEL ABEL FOR THE APPLE MACINTOSH nOR IIX WORKSTATION A/UX VERSION GENERAL DESCRIPTION ABEL.'" the industry standard PLD design software, is now available on the Apple Macintosh® II or IIx workstation. MacABEL allows you to take advantage of the personal productivity features of the Macintosh to easily describe and implement logic designs in programmable logic devices (PLDs) and PROMs. Like ABEL Version 3.0 for other popular workstations, MacABEL combines a natural high-level design language with a language processor that converts logic descriptions to programmer load files. These files contain the required information to program and test PLDs. MacABEL allows you to describe your design in any combi nation of Boolean equations, truth tables or state diagrams whichever best suits the logic you are describing or your comfort level. Meaningful names can be assigned to signals; signals grouped into sets; and macros used to simplify logic descriptions - making your logic design easy to read and • Boolean equations understand. • State machine diagram entry, using IF-THEN-ELSE, CASE, In addition, the software's language processor provides GOTQ and WITH-ENDWITH statements powerful logic reduction, extensive syntax and logic error • Truth tables to specify input to output relationships for both checking - before your device is programmed. MacABEL combinatorial and registered outputs supports the most powerful and innovative complex PLDs just • High-level equation entry, incorporating the boolean introduced on the market, as well as many still in development. operators used in most logic designs < 1 1 & 1 # 1 $ 1 1 $ ) , MacABEL runs under the Apple A/UX'" operating system arithmetic operators <- I + I * I I I %I < < I > > ) , relational utilizing the Macintosh user interface. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

A Vhdl-Based Digital Slot Machine Implementation Using A

A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE by Lucas C. Pascute Submitted in Partial Fulfillment ofthe Requirements for the Degree of Master ofScience ofEngineering in the Electrical Engineering Program YOUNGSTOWN STATE UNIVERSITY December, 2002 A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE Lucas C. Pascute I hereby release this thesis to the public. I understand that this thesis will be made available from the OhioLINK ETD Center and the Maag Library Circulation Desk for public access. I also authorize the University or other individuals to make copies ofthis thesis as needed for scholarly research. Signature: ;/ (' , p ~-~_.._--- c:;.--_. ~ ~b IZ-3-Cl7., Lucas C. Pascute, Student Date Approvals: r. Faramarz Mossayebi, Thesis Advisor 12-:}--02- Date S~?c~ /"L/ 0:5 /u C Dr. Salvatore Pansino, Committee Member Date Dr. Peter J. K: vinsky, Dean ofGradua 111 ABSTRACT The intent ofthis project is to provide an educational resource from which future students can learn the basics ofprogrammable logic and the design process involved. More specifically, the area ofinterest involves very large scale integration (VLSI) design and the advantages associated with it such as reduced chip count and development time. The methodology used within is to first implement a design; using small and medium scale integration (SSI/MSI) packages in order to have a baseline for comparison. The design is then translated for use with the very high speed integrated circuit hardware description language (VHDL) and implemented onto a complex programmable logic device (CPLD). A discussion ofthis implementation process as well as VHDL lessons is provided to serve as a tutorial for the interested reader. -

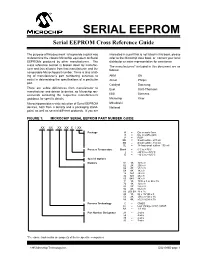

Serial EEPROM Cross Reference Guide

SERIAL EEPROM Serial EEPROM Cross Reference Guide The purpose of this document is to provide a quick way interested in a part that is not listed in this book, please to determine the closest Microchip equivalent to Serial refer to the Microchip data book, or contact your local EEPROMs produced by other manufacturers. The distributor or sales representative for assistance. cross reference section is broken down by manufac- The manufacturers* included in this document are as turer and lists all parts from that manufacturer, and the follows: comparable Microchip part number. There is also a list- ing of manufacturer’s part numbering schemes to AKM Oki assist in determining the specifications of a particular Atmel Philips part. Catalyst Samsung There are subtle differences from manufacturer to Exel SGS-Thomson manufacturer and device to device, so Microchip rec- ommends consulting the respective manufacturer’s ISSI Siemens gadabout for specific details. Microchip Xicor Microchip provides a wide selection of Serial EEPROM Mitsubishi devices, both from a density and a packaging stand- National point, as well as several different protocols. If you are FIGURE 1: MICROCHIP SERIAL EEPROM PART NUMBER GUIDE XX XX XX XX X / XX Package W = Die in wafer form S = Die in waffle pack P = PDIP SM = Small outline .207 mil SN = Small outline .150 mil SL = 14-lead small outline .150 mil Process Temperature Blank = 0°C to +70°C I = -40°C to +125°C E = -40°C to +125°C Special Options Memory 01 1K 128 x 8 02 2K 256 x 8 04 4K 512 x 8 08 8K 1K x 8 16 16K 2K x 8 32 32K 4K x 8 65 64K 8K x 8 11 1K 128K x 8 or 64 x 16 72 1K 128 x 8 82 2K 256 x 8 92 4K 512 x 8 06 256 Bit 16 x 16 46 1K 64 x 16/128 x 8 56 2K 256 x 8/128 x 16 66 4K 512 x 8/256 x 16 Process Technology C – CMOS LC – Low Voltage (2.5V) CMOS AA – 1.8 Volt Part Number Designator 24 – 2-wire 59 – 4-wire 85 – 2-wire 93 – 3-wire *The above trademarks are property of their respective companies. -

Review of FPD's Languages, Compilers, Interpreters and Tools

ISSN 2394-7314 International Journal of Novel Research in Computer Science and Software Engineering Vol. 3, Issue 1, pp: (140-158), Month: January-April 2016, Available at: www.noveltyjournals.com Review of FPD'S Languages, Compilers, Interpreters and Tools 1Amr Rashed, 2Bedir Yousif, 3Ahmed Shaban Samra 1Higher studies Deanship, Taif university, Taif, Saudi Arabia 2Communication and Electronics Department, Faculty of engineering, Kafrelsheikh University, Egypt 3Communication and Electronics Department, Faculty of engineering, Mansoura University, Egypt Abstract: FPGAs have achieved quick acceptance, spread and growth over the past years because they can be applied to a variety of applications. Some of these applications includes: random logic, bioinformatics, video and image processing, device controllers, communication encoding, modulation, and filtering, limited size systems with RAM blocks, and many more. For example, for video and image processing application it is very difficult and time consuming to use traditional HDL languages, so it’s obligatory to search for other efficient, synthesis tools to implement your design. The question is what is the best comparable language or tool to implement desired application. Also this research is very helpful for language developers to know strength points, weakness points, ease of use and efficiency of each tool or language. This research faced many challenges one of them is that there is no complete reference of all FPGA languages and tools, also available references and guides are few and almost not good. Searching for a simple example to learn some of these tools or languages would be a time consuming. This paper represents a review study or guide of almost all PLD's languages, interpreters and tools that can be used for programming, simulating and synthesizing PLD's for analog, digital & mixed signals and systems supported with simple examples. -

Dissertation Applications of Field Programmable Gate

DISSERTATION APPLICATIONS OF FIELD PROGRAMMABLE GATE ARRAYS FOR ENGINE CONTROL Submitted by Matthew Viele Department of Mechanical Engineering In partial fulfillment of the requirements For the Degree of Doctor of Philosophy Colorado State University Fort Collins, Colorado Summer 2012 Doctoral Committee: Advisor: Bryan D. Willson Anthony J. Marchese Robert N. Meroney Wade O. Troxell ABSTRACT APPLICATIONS OF FIELD PROGRAMMABLE GATE ARRAYS FOR ENGINE CONTROL Automotive engine control is becoming increasingly complex due to the drivers of emissions, fuel economy, and fault detection. Research in to new engine concepts is often limited by the ability to control combustion. Traditional engine-targeted micro controllers have proven difficult for the typical engine researchers to use and inflexible for advanced concept engines. With the advent of Field Programmable Gate Array (FPGA) based engine control system, many of these impediments to research have been lowered. This dissertation will talk about three stages of FPGA engine controller appli- cation. The most basic and widely distributed is the FPGA as an I/O coprocessor, tracking engine position and performing other timing critical low-level tasks. A later application of FPGAs is the use of microsecond loop rates to introduce feedback con- trol on the crank angle degree level. Lastly, the development of custom real-time computing machines to tackle complex engine control problems is presented. This document is a collection of papers and patents that pertain to the use of FPGAs for the above tasks. Each task is prefixed with a prologue section to give the history of the topic and context of the paper in the larger scope of FPGA based engine control. -

MACHXL Software User's Guide

MACHXL Software User's Guide © 1993 Advanced Micro Devices, Inc. TEL: 408-732-2400 P.O. Box 3453 TWX: 910339-9280 Sunnyvale, CA 94088 TELEX: 34-6306 TOLL FREE: 800-538-8450 APPLICATIONS HOTLINE: 800-222-9323 (US) 44-(0)-256-811101 (UK) 0590-8621 (France) 0130-813875 (Germany) 1678-77224 (Italy) Advanced Micro Devices reserves the right to make changes in specifications at any time and without notice. The information furnished by Advanced Micro Devices is believed to be accurate and reliable. However, no responsibility is assumed by Advanced Micro Devices for its use, nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Advanced Micro Devices. Epson® is a registered trademark of Epson America, Inc. Hewlett-Packard®, HP®, and LaserJet® are registered trademarks of Hewlett-Packard Company. IBM® is a registered trademark and IBM PCä is a trademark of International Business Machines Corporation. Microsoft® and MS-DOS® are registered trademarks of Microsoft Corporation. PAL® and PALASM® are registered trademarks and MACHä and MACHXL ä are trademarks of Advanced Micro Devices, Inc. Pentiumä is a trademark of Intel Corporation. Wordstar® is a registered trademark of MicroPro International Corporation. Document revision 1.2 Published October, 1994. Printed inU.S.A. ii Contents Chapter 1. Installation Hardware Requirements 2 Software Requirements 3 Installation Procedure 4 Updating System Files 6 AUTOEXEC.BAT 7 CONFIG.SYS 7 Creating a Windows Icon -

Programmable Logic Design Quick Start Handbook

00-Beginners Book front.fm Page i Wednesday, October 8, 2003 10:58 AM Programmable Logic Design Quick Start Handbook by Karen Parnell and Nick Mehta August 2003 Xilinx • i 00-Beginners Book front.fm Page ii Wednesday, October 8, 2003 10:58 AM PROGRAMMABLE LOGIC DESIGN: QUICK START HANDBOOK • © 2003, Xilinx, Inc. “Xilinx” is a registered trademark of Xilinx, Inc. Any rights not expressly granted herein are reserved. The Programmable Logic Company is a service mark of Xilinx, Inc. All terms mentioned in this book are known to be trademarks or service marks and are the property of their respective owners. Use of a term in this book should not be regarded as affecting the validity of any trade- mark or service mark. All rights reserved. No part of this book may be reproduced, in any form or by any means, without written permission from the publisher. PN 0402205 Rev. 3, 10/03 Xilinx • ii 00-Beginners Book front.fm Page iii Wednesday, October 8, 2003 10:58 AM ABSTRACT Whether you design with discrete logic, base all of your designs on micro- controllers, or simply want to learn how to use the latest and most advanced programmable logic software, you will find this book an interesting insight into a different way to design. Programmable logic devices were invented in the late 1970s and have since proved to be very popular, now one of the largest growing sectors in the semi- conductor industry. Why are programmable logic devices so widely used? Besides offering designers ultimate flexibility, programmable logic devices also provide a time-to-market advantage and design integration. -

Legal Notice

Altera Digital Library September 1996 P-CD-ADL-01 Legal Notice This CD contains documentation and other information related to products and services of Altera Corporation (“Altera”) which is provided as a courtesy to Altera’s customers and potential customers. By copying or using any information contained on this CD, you agree to be bound by the terms and conditions described in this Legal Notice. The documentation, software, and other materials contained on this CD are owned and copyrighted by Altera and its licensors. Copyright © 1994, 1995, 1996 Altera Corporation, 2610 Orchard Parkway, San Jose, California 95134, USA and its licensors. All rights reserved. You are licensed to download and copy documentation and other information from this CD provided you agree to the following terms and conditions: (1) You may use the materials for informational purposes only. (2) You may not alter or modify the materials in any way. (3) You may not use any graphics separate from any accompanying text. (4) You may distribute copies of the documentation available on this CD only to customers and potential customers of Altera products. However, you may not charge them for such use. Any other distribution to third parties is prohibited unless you obtain the prior written consent of Altera. (5) You may not use the materials in any way that may be adverse to Altera’s interests. (6) All copies of materials that you copy from this CD must include a copy of this Legal Notice. Altera, MAX, MAX+PLUS, FLEX, FLEX 10K, FLEX 8000, FLEX 8000A, MAX 9000, MAX 7000,