Nanodot-Based Organic Memory Devices Zhengchun Liu Louisiana Tech University

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 3 Semiconductor Memories

Chapter 3 Semiconductor Memories Jin-Fu Li Department of Electrical Engineering National Central University Jungli, Taiwan Outline Introduction Random Access Memories Content Addressable Memories Read Only Memories Flash Memories Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 2 Overview of Memory Types Semiconductor Memories Read/Write Memory or Random Access Memory (RAM) Read Only Memory (ROM) Random Access Non-Random Access Memory (RAM) Memory (RAM) •Mask (Fuse) ROM •Programmable ROM (PROM) •Erasable PROM (EPROM) •Static RAM (SRAM) •FIFO/LIFO •Electrically EPROM (EEPROM) •Dynamic RAM (DRAM) •Shift Register •Flash Memory •Register File •Content Addressable •Ferroelectric RAM (FRAM) Memory (CAM) •Magnetic RAM (MRAM) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 3 Memory Elements – Memory Architecture Memory elements may be divided into the following categories Random access memory Serial access memory Content addressable memory Memory architecture 2m+k bits row decoder row decoder 2n-k words row decoder row decoder column decoder k column mux, n-bit address sense amp, 2m-bit data I/Os write buffers Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 4 1-D Memory Architecture S0 S0 Word0 Word0 S1 S1 Word1 Word1 S2 S2 Word2 Word2 A0 S3 S3 A1 Decoder Ak-1 Sn-2 Storage Sn-2 Wordn-2 element Wordn-2 Sn-1 Sn-1 Wordn-1 Wordn-1 m-bit m-bit Input/Output Input/Output n select signals are reduced n select signals: S0-Sn-1 to k address signals: A0-Ak-1 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 5 Memory Architecture S0 Word0 Wordi-1 S1 A0 A1 Ak-1 Row Decoder Sn-1 Wordni-1 A 0 Column Decoder Aj-1 Sense Amplifier Read/Write Circuit m-bit Input/Output Advanced Reliable Systems (ARES) Lab. -

Error Detection and Correction Methods for Memories Used in System-On-Chip Designs

International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-8, Issue-2S2, January 2019 Error Detection and Correction Methods for Memories used in System-on-Chip Designs Gunduru Swathi Lakshmi, Neelima K, C. Subhas ABSTRACT— Memory is the basic necessity in any SoC Static Random Access Memory (SRAM): It design. Memories are classified into single port memory and consists of a latch or flipflop to store each bit of multiport memory. Multiport memory has ability to source more memory and it does not required any refresh efficient execution of operation and high speed performance operation. SRAM is mostly used in cache memory when compared to single port. Testing of semiconductor memories is increasing because of high density of current in the and in hand-held devices. It has advantages like chips. Due to increase in embedded on chip memory and memory high speed and low power consumption. It has density, the number of faults grow exponentially. Error detection drawback like complex structure and expensive. works on concept of redundancy where extra bits are added for So, it is not used for high capacity applications. original data to detect the error bits. Error correction is done in Read Only Memory (ROM): It is a non-volatile memory. two forms: one is receiver itself corrects the data and other is It can only access data but cannot modify data. It is of low receiver sends the error bits to sender through feedback. Error detection and correction can be done in two ways. One is Single cost. Some applications of ROM are scanners, ID cards, Fax bit and other is multiple bit. -

Low Voltage, One-Time Programmable, Read-Only Memory

Features • Fast read access time – 90ns • Dual voltage range operation – Low voltage power supply range, 3.0V to 3.6V, or – Standard power supply range, 5V 10% • Compatible with JEDEC standard Atmel® AT27C512R • Low-power CMOS operation – 20µA max standby (less than 1µA, typical) for VCC = 3.6V – 29mW max active at 5MHz for VCC = 3.6V 512K (64K x 8) • JEDEC standard package – 32-lead PLCC Low Voltage, • High-reliability CMOS technology One-time – 2,000V ESD protection Programmable, – 200mA latchup immunity • Rapid programming algorithm – 100µs/byte (typical) Read-only Memory • CMOS- and TTL-compatible inputs and outputs – JEDEC standard for LVTTL • Integrated product identification code Atmel AT27LV512A • Industrial temperature range • Green (Pb/halide-free) packaging option 1. Description The Atmel AT27LV512A is a high-performance, low-power, low-voltage, 524,288-bit, one- time programmable, read-only memory (OTP EPROM) organized as 64K by 8 bits. It requires only one supply in the range of 3.0 to 3.6V in normal read mode operation, making it ideal for fast, portable systems using battery power. The Atmel innovative design techniques provide fast speeds that rival 5V parts, while keep- ing the low power consumption of a 3.3V supply. At VCC = 3.0V, any byte can be accessed in less than 90ns. With a typical power dissipation of only 18mW at 5MHz and VCC = 3.3V, the AT27LV512A consumes less than one-fifth the power of a standard, 5V EPROM. Standby mode supply current is typically less than 1µA at 3.3V. The AT27LV512A is available in industry-standard, JEDEC-approved, one-time programmable (OTP) PLCC package. -

Semiconductor Memories

Semiconductor Memories Prof. MacDonald Types of Memories! l" Volatile Memories –" require power supply to retain information –" dynamic memories l" use charge to store information and require refreshing –" static memories l" use feedback (latch) to store information – no refresh required l" Non-Volatile Memories –" ROM (Mask) –" EEPROM –" FLASH – NAND or NOR –" MRAM Memory Hierarchy! 100pS RF 100’s of bytes L1 1nS SRAM 10’s of Kbytes 10nS L2 100’s of Kbytes SRAM L3 100’s of 100nS DRAM Mbytes 1us Disks / Flash Gbytes Memory Hierarchy! l" Large memories are slow l" Fast memories are small l" Memory hierarchy gives us illusion of large memory space with speed of small memory. –" temporal locality –" spatial locality Register Files ! l" Fastest and most robust memory array l" Largest bit cell size l" Basically an array of large latches l" No sense amps – bits provide full rail data out l" Often multi-ported (i.e. 8 read ports, 2 write ports) l" Often used with ALUs in the CPU as source/destination l" Typically less than 10,000 bits –" 32 32-bit fixed point registers –" 32 60-bit floating point registers SRAM! l" Same process as logic so often combined on one die l" Smaller bit cell than register file – more dense but slower l" Uses sense amp to detect small bit cell output l" Fastest for reads and writes after register file l" Large per bit area costs –" six transistors (single port), eight transistors (dual port) l" L1 and L2 Cache on CPU is always SRAM l" On-chip Buffers – (Ethernet buffer, LCD buffer) l" Typical sizes 16k by 32 Static Memory -

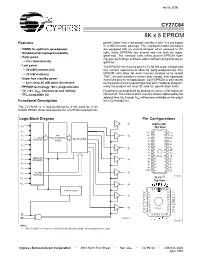

8K X 8 EPROM Features Powers Down Into a Low-Power Standby Mode

1CY 27C6 4 fax id: 3006 CY27C64 8K x 8 EPROM Features powers down into a low-power standby mode. It is packaged in a 600-mil-wide package. The reprogrammable packages • CMOS for optimum speed/power are equipped with an erasure window; when exposed to UV • Windowed for reprogrammability light, these EPROMs are erased and can then be repro- • High speed grammed. The memory cells utilize proven EPROM float- ing-gate technology and byte-wide intelligent programming al- — 0 ns (commercial) gorithms. • Low power The EPROM cell requires only 12.5V for the super voltage and — 40 mW (commercial) low–current requirements allow for gang programming. The — 30 mW (military) EPROM cells allow for each memory location to be tested 100%, as each location is written into, erased, and repeatedly • Super low standby power exercised prior to encapsulation. Each EPROM is also tested — Less than 85 mW when deselected for AC performance to guarantee that after customer program- • EPROM technology 100% programmable ming, the product will meet DC and AC specification limits. ± • 5V 10% VCC, commercial and military Reading is accomplished by placing an active LOW signal on • TTL-compatible I/O OE and CE. The contents of the memory location addressed by the address lines (A0 through A12) will become available on the output Functional Description lines (O0 through O7). The CY27C64 is a high-performance 8192 word by 8 bit CMOS PROM. When deselected, the CY27C64 automatically Logic Block Diagram Pin Configurations O7 DIP/CerDIP A0 Top View A1 VCC 1 28 VCC 2 27 A2 64K O6 A12 VCC ROW PROGRAMMABLE A7 3 26 NC A ADDRESS MULTIPLEXER 3 ARRAY A 4 6 25 A8 A5 5 24 A9 A4 A 6 4 23 A11 O5 A5 A3 7 22 OE A2 8 21 A10 A6 A1 9 27C64 20 CE ADDRESS A A7 O 0 10 19 O7 DECODER 4 O0 11 18 O6 A8 O1 12 17 O5 O 13 16 O A9 2 4 GND 14 15 O3 O A10 COLUMN 3 ADDRESS [1] 27C64-2 A11 PLCC Top View A 12 O2 4 POWER DOWN 32132 31 30 A A 6 5 29 8 A 5 6 28 A9 O1 A 4 7 27 A11 A 3 8 26 NC A 2 9 25 OE A A 1 10 24 10 A0 23 CE O0 11 27C64 NC 12 22 O7 O0 13 21 O6 14 15 16 17 18 19 20 CE OE 27C64-1 27C64-3 Notes: 1. -

Archiving Online Data to Optical Disk

ARCHIVING ONLINE DATA TO OPTICAL DISK By J. L. Porter, J. L. Kiesler, and D. A. Stedfast U.S. GEOLOGICAL SURVEY Open-File Report 90-575 Reston, Virginia 1990 U.S. DEPARTMENT OF THE INTERIOR MANUEL LUJAN, JR., Secretary U.S. GEOLOGICAL SURVEY Dallas L. Peck, Director For additional information Copies of this report can be write to: purchased from: Chief, Distributed Information System U.S. Geological Survey U.S. Geological Survey Books and Open-File Reports Section Mail Stop 445 Federal Center, Bldg. 810 12201 Sunrise Valley Drive Box 25425 Reston, Virginia 22092 Denver, Colorado 80225 CONTENTS Page Abstract ............................................................. 1 Introduction ......................................................... 2 Types of optical storage ............................................... 2 Storage media costs and alternative media used for data archival. ......... 3 Comparisons of storage media ......................................... 3 Magnetic compared to optical media ............................... 3 Compact disk read-only memory compared to write-once/read many media ................................... 6 Erasable compared to write-once/read many media ................. 7 Paper and microfiche compared to optical media .................... 8 Advantages of write-once/read-many optical storage ..................... 8 Archival procedure and results ........................................ 9 Summary ........................................................... 13 References .......................................................... -

The Future of Data Storage Technologies

International Technology Research Institute World Technology (WTEC) Division WTEC Panel Report on The Future of Data Storage Technologies Sadik C. Esener (Panel Co-Chair) Mark H. Kryder (Panel Co-Chair) William D. Doyle Marvin Keshner Masud Mansuripur David A. Thompson June 1999 International Technology Research Institute R.D. Shelton, Director Geoffrey M. Holdridge, WTEC Division Director and ITRI Series Editor 4501 North Charles Street Baltimore, Maryland 21210-2699 WTEC Panel on the Future of Data Storage Technologies Sponsored by the National Science Foundation, Defense Advanced Research Projects Agency and National Institute of Standards and Technology of the United States government. Dr. Sadik C. Esener (Co-Chair) Dr. Marvin Keshner Dr. David A. Thompson Prof. of Electrical and Computer Director, Information Storage IBM Fellow Engineering & Material Sciences Laboratory Research Division Dept. of Electrical & Computer Hewlett-Packard Laboratories International Business Machines Engineering 1501 Page Mill Road Corporation University of California, San Diego Palo Alto, CA 94304-1126 Almaden Research Center 9500 Gilman Drive Mail Stop K01/802 La Jolla, CA 92093-0407 Dr. Masud Mansuripur 650 Harry Road Optical Science Center San Jose, CA 95120-6099 Dr. Mark H. Kryder (Co-Chair) University of Arizona Director, Data Storage Systems Center Tucson, AZ 85721 Carnegie Mellon University Roberts Engineering Hall, Rm. 348 Pittsburgh, PA 15213-3890 Dr. William D. Doyle Director, MINT Center University of Alabama Box 870209 Tuscaloosa, AL 35487-0209 INTERNATIONAL TECHNOLOGY RESEARCH INSTITUTE World Technology (WTEC) Division WTEC at Loyola College (previously known as the Japanese Technology Evaluation Center, JTEC) provides assessments of foreign research and development in selected technologies under a cooperative agreement with the National Science Foundation (NSF). -

3 Secondary Storage.PDF

CAPE COMPUTER SCIENCE SECONDARY STORAGE Secondary storage is needed 1. because there is a limit on the size of primary memory (due to cost) and 2. because RAM is volatile and so data needed for future use must be stored somewhere else so that it can be retrieved when necessary. Secondary storage is also used for backup and archives. When we consider secondary storage devices we must bear in mind the following characteristics of each device : Capacity Access speed Access method and portability Floppy Disk This is a 3.5 inch magnetic disk of flexible material which until recently was a standard feature on most microcomputers. Typically it stores 1.44 MB of data. It’s a thin plastic circle coated with a magnetic material and encased in a rigid plastic to protect it. A metal sliding access shuttle opens when the disk is in the machine allowing the read/write head access to the disk. Data can be written to and erased from a floppy disk. A write protect tab can be used to prevent accidental overwriting of data. Before data can be written to a disk, it must be formatted. This prepares the disk for use by creating a magnetic map on the disks surface. This map consists of tracks and sectors. Formatting also prepares the file allocation table (FAT). The address of a file on a floppy disk is comprised of the track number and the sector number. Floppy disks are direct access devices but they are slow compared to hard disks. The floppies great advantage has been its use as a device to help transport small files between machines. -

Unit 5: Memory Organizations

Memory Organizations Unit 5: Memory Organizations Introduction This unit considers the organization of a computer's memory system. The characteristics of the most important storage technologies are described in detail. Basically memories are classified as main memory and secondary memory. Main memory with many different categories are described in Lesson 1. Lesson 2 focuses the secondary memory including the details of floppy disks and hard disks. Lesson 1: Main Memory 1.1 Learning Objectives On completion of this lesson you will be able to : • describe the memory organization • distinguish between ROM, RAM, PROM, EEPROM and • other primary memory elements. 1.2 Organization Computer systems combine binary digits to form groups called words. The size of the word varies from system to system. Table 5.1 illustrates the current word sizes most commonly used with the various computer systems. Two decades ago, IBM introduced their 8-bit PC. This was Memory Organization followed a few years later by the 16-bit PC AT microcomputer, and already it has been replaced with 32- and 64-bit systems. The machine with increased word size is generally faster because it can process more bits of information in the same time span. The current trend is in the direction of the larger word size. Microcomputer main memories are generally made up of many individual chips and perform different functions. The ROM, RAM, Several types of semi- PROM, and EEPROM memories are used in connection with the conductor memories. primary memory of a microcomputers. The main memory generally store computer words as multiple of bytes; each byte consisting of eight bits. -

SŁOWNIK POLSKO-ANGIELSKI ELEKTRONIKI I INFORMATYKI V.03.2010 (C) 2010 Jerzy Kazojć - Wszelkie Prawa Zastrzeżone Słownik Zawiera 18351 Słówek

OTWARTY SŁOWNIK POLSKO-ANGIELSKI ELEKTRONIKI I INFORMATYKI V.03.2010 (c) 2010 Jerzy Kazojć - wszelkie prawa zastrzeżone Słownik zawiera 18351 słówek. Niniejszy słownik objęty jest licencją Creative Commons Uznanie autorstwa - na tych samych warunkach 3.0 Polska. Aby zobaczyć kopię niniejszej licencji przejdź na stronę http://creativecommons.org/licenses/by-sa/3.0/pl/ lub napisz do Creative Commons, 171 Second Street, Suite 300, San Francisco, California 94105, USA. Licencja UTWÓR (ZDEFINIOWANY PONIŻEJ) PODLEGA NINIEJSZEJ LICENCJI PUBLICZNEJ CREATIVE COMMONS ("CCPL" LUB "LICENCJA"). UTWÓR PODLEGA OCHRONIE PRAWA AUTORSKIEGO LUB INNYCH STOSOWNYCH PRZEPISÓW PRAWA. KORZYSTANIE Z UTWORU W SPOSÓB INNY NIŻ DOZWOLONY NA PODSTAWIE NINIEJSZEJ LICENCJI LUB PRZEPISÓW PRAWA JEST ZABRONIONE. WYKONANIE JAKIEGOKOLWIEK UPRAWNIENIA DO UTWORU OKREŚLONEGO W NINIEJSZEJ LICENCJI OZNACZA PRZYJĘCIE I ZGODĘ NA ZWIĄZANIE POSTANOWIENIAMI NINIEJSZEJ LICENCJI. 1. Definicje a."Utwór zależny" oznacza opracowanie Utworu lub Utworu i innych istniejących wcześniej utworów lub przedmiotów praw pokrewnych, z wyłączeniem materiałów stanowiących Zbiór. Dla uniknięcia wątpliwości, jeżeli Utwór jest utworem muzycznym, artystycznym wykonaniem lub fonogramem, synchronizacja Utworu w czasie z obrazem ruchomym ("synchronizacja") stanowi Utwór Zależny w rozumieniu niniejszej Licencji. b."Zbiór" oznacza zbiór, antologię, wybór lub bazę danych spełniającą cechy utworu, nawet jeżeli zawierają nie chronione materiały, o ile przyjęty w nich dobór, układ lub zestawienie ma twórczy charakter. -

Arduino Nano

Arduino Nano Arduino Nano Front Arduino Nano Rear Overview The Arduino Nano is a small, complete, and breadboard-friendly board based on the ATmega328 (Arduino Nano 3.0) or ATmega168 (Arduino Nano 2.x). It has more or less the same functionality of the Arduino Duemilanove, but in a different package. It lacks only a DC power jack, and works with a Mini-B USB cable instead of a standard one. The Nano was designed and is being produced by Gravitech. Schematic and Design Arduino Nano 3.0 (ATmega328): schematic, Eagle files. Arduino Nano 2.3 (ATmega168): manual (pdf), Eagle files. Note: since the free version of Eagle does not handle more than 2 layers, and this version of the Nano is 4 layers, it is published here unrouted, so users can open and use it in the free version of Eagle. Specifications: Microcontroller Atmel ATmega168 or ATmega328 Operating Voltage (logic 5 V level) Input Voltage 7-12 V (recommended) Input Voltage (limits) 6-20 V Digital I/O Pins 14 (of which 6 provide PWM output) Analog Input Pins 8 DC Current per I/O Pin 40 mA 16 KB (ATmega168) or 32 KB (ATmega328) of which 2 KB used by Flash Memory bootloader SRAM 1 KB (ATmega168) or 2 KB (ATmega328) EEPROM 512 bytes (ATmega168) or 1 KB (ATmega328) Clock Speed 16 MHz Dimensions 0.73" x 1.70" Power: The Arduino Nano can be powered via the Mini-B USB connection, 6-20V unregulated external power supply (pin 30), or 5V regulated external power supply (pin 27). -

EE 4504 Computer Organization Overview

Overview Historically, the limiting factor in a computer’s performance has been memory access time – Memory speed has been slow compared to the speed of the processor EE 4504 – A process could be bottlenecked by the memory Computer Organization system’s inability to “keep up” with the processor Our goal in this section is to study the development of an effective memory Section 3 organization that supports the processing Computer Memory power of the CPU – General memory organization and performance – “Internal” memory components and their use – “External” memory components and their use Reading: Text, chapters 4 and 5 EE 4504 Section 3 1 EE 4504 Section 3 2 1 Terminology Capacity: the amount of information that Access time: can be contained in a memory unit -- – For RAM, the time to address the unit and usually in terms of words or bytes perform the transfer Word: the natural unit of organization in – For non-random access memory, the time to position the R/W head over the desired location the memory, typically the number of bits used to represent a number Memory cycle time: Access time plus any other time required before a second access Addressable unit: the fundamental data can be started element size that can be addressed in the memory -- typically either the word size or Access technique: how are memory individual bytes contents accessed – Random access: Unit of transfer: The number of data » Each location has a unique physical address elements transferred at a time -- usually » Locations can be accessed in any order and bits in main