Combinational Logic Design Ratioed Logic One Method to Reduce The

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Hybrid Memristor–CMOS Implementation of Combinational Logic Based on X-MRL †

electronics Article Hybrid Memristor–CMOS Implementation of Combinational Logic Based on X-MRL † Khaled Alhaj Ali 1,* , Mostafa Rizk 1,2,3 , Amer Baghdadi 1 , Jean-Philippe Diguet 4 and Jalal Jomaah 3 1 IMT Atlantique, Lab-STICC CNRS, UMR, 29238 Brest, France; [email protected] (M.R.); [email protected] (A.B.) 2 Lebanese International University, School of Engineering, Block F 146404 Mazraa, Beirut 146404, Lebanon 3 Faculty of Sciences, Lebanese University, Beirut 6573, Lebanon; [email protected] 4 IRL CROSSING CNRS, Adelaide 5005, Australia; [email protected] * Correspondence: [email protected] † This paper is an extended version of our paper published in IEEE International Conference on Electronics, Circuits and Systems (ICECS) , 27–29 November 2019, as Ali, K.A.; Rizk, M.; Baghdadi, A.; Diguet, J.P.; Jomaah, J. “MRL Crossbar-Based Full Adder Design”. Abstract: A great deal of effort has recently been devoted to extending the usage of memristor technology from memory to computing. Memristor-based logic design is an emerging concept that targets efficient computing systems. Several logic families have evolved, each with different attributes. Memristor Ratioed Logic (MRL) has been recently introduced as a hybrid memristor–CMOS logic family. MRL requires an efficient design strategy that takes into consideration the implementation phase. This paper presents a novel MRL-based crossbar design: X-MRL. The proposed structure combines the density and scalability attributes of memristive crossbar arrays and the opportunity of their implementation at the top of CMOS layer. The evaluation of the proposed approach is performed through the design of an X-MRL-based full adder. -

Three-Dimensional Integrated Circuit Design: EDA, Design And

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to http://www.springer.com/series/7236 Yuan Xie · Jason Cong · Sachin Sapatnekar Editors Three-Dimensional Integrated Circuit Design EDA, Design and Microarchitectures 123 Editors Yuan Xie Jason Cong Department of Computer Science and Department of Computer Science Engineering University of California, Los Angeles Pennsylvania State University [email protected] [email protected] Sachin Sapatnekar Department of Electrical and Computer Engineering University of Minnesota [email protected] ISBN 978-1-4419-0783-7 e-ISBN 978-1-4419-0784-4 DOI 10.1007/978-1-4419-0784-4 Springer New York Dordrecht Heidelberg London Library of Congress Control Number: 2009939282 © Springer Science+Business Media, LLC 2010 All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights. Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) Foreword We live in a time of great change. -

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

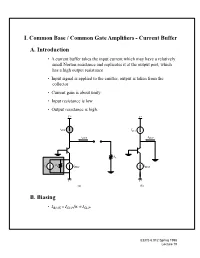

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

Precision Current Sources and Sinks Using Voltage References

Application Report SNOAA46–June 2020 Precision Current Sources and Sinks Using Voltage References Marcoo Zamora ABSTRACT Current sources and sinks are common circuits for many applications such as LED drivers and sensor biasing. Popular current references like the LM134 and REF200 are designed to make this choice easier by requiring minimal external components to cover a broad range of applications. However, sometimes the requirements of the project may demand a little more than what these devices can provide or set constraints that make them inconvenient to implement. For these cases, with a voltage reference like the TL431 and a few external components, one can create a simple current bias with high performance that is flexible to fit meet the application requirements. Current sources and sinks have been covered extensively in other Texas Instruments application notes such as SBOA046 and SLYC147, but this application note will cover other common current sources that haven't been previously discussed. Contents 1 Precision Voltage References.............................................................................................. 1 2 Current Sink with Voltage References .................................................................................... 2 3 Current Source with Voltage References................................................................................. 4 4 References ................................................................................................................... 6 List of Figures 1 Current -

LDMOS for Improved Performance

> Submitted to IEEE Transactions on Electron Devices < Final MS # 8011B 1 Extended-p+ Stepped Gate (ESG) LDMOS for Improved Performance M. Jagadesh Kumar, Senior Member, IEEE and Radhakrishnan Sithanandam Abstract—In this paper, we propose a new Extended-p+ Stepped Gate (ESG) thin film SOI LDMOS with an extended-p+ region beneath the source and a stepped gate structure in the drift region of the LDMOS. The hole current generated due to impact ionization is now collected from an n+p+ junction instead of an n+p junction thus delaying the parasitic BJT action. The stepped gate structure enhances RESURF in the drift region, and minimizes the gate-drain capacitance. Based on two- dimensional simulation results, we show that the ESG LDMOS exhibits approximately 63% improvement in breakdown voltage, 38% improvement in on-resistance, 11% improvement in peak transconductance, 18% improvement in switching speed and 63% reduction in gate-drain charge density compared with the conventional LDMOS with a field plate. Index Terms—LDMOS, silicon on insulator (SOI), breakdown voltage, transconductance, on- resistance, gate charge I. INTRODUCTION ATERALLY double diffused metal oxide semiconductor (LDMOS) on SOI substrate is a promising Ltechnology for RF power amplifiers and wireless applications [1-5]. In the recent past, developing high voltage thin film LDMOS has gained importance due to the possibility of its integration with low power CMOS devices and heterogeneous microsystems [6]. But realization of high voltage devices in thin film SOI is challenging because floating body effects affect the breakdown characteristics. Often, body contacts are included to remove the floating body effects in RF devices [7]. -

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS Outline • NMOS inverter with resistor pull-up –The inverter • NMOS inverter with current-source pull-up • Complementary MOS (CMOS) inverter • Static analysis of CMOS inverter Reading Assignment: Howe and Sodini; Chapter 5, Section 5.4 6.012 Spring 2007 Lecture 12 1 1. NMOS inverter with resistor pull-up: Dynamics •CL pull-down limited by current through transistor – [shall study this issue in detail with CMOS] •CL pull-up limited by resistor (tPLH ≈ RCL) • Pull-up slowest VDD VDD R R VOUT: VOUT: HI LO LO HI V : VIN: IN C LO HI CL HI LO L pull-down pull-up 6.012 Spring 2007 Lecture 12 2 1. NMOS inverter with resistor pull-up: Inverter design issues Noise margins ↑⇒|Av| ↑⇒ •R ↑⇒|RCL| ↑⇒ slow switching •gm ↑⇒|W| ↑⇒ big transistor – (slow switching at input) Trade-off between speed and noise margin. During pull-up we need: • High current for fast switching • But also high incremental resistance for high noise margin. ⇒ use current source as pull-up 6.012 Spring 2007 Lecture 12 3 2. NMOS inverter with current-source pull-up I—V characteristics of current source: iSUP + 1 ISUP r i oc vSUP SUP _ vSUP Equivalent circuit models : iSUP + ISUP r r vSUP oc oc _ large-signal model small-signal model • High current throughout voltage range vSUP > 0 •iSUP = 0 for vSUP ≤ 0 •iSUP = ISUP + vSUP/ roc for vSUP > 0 • High small-signal resistance roc. 6.012 Spring 2007 Lecture 12 4 NMOS inverter with current-source pull-up Static Characteristics VDD iSUP VOUT VIN CL Inverter characteristics : iD = V 4 3 VIN VGS I + DD SUP roc 2 1 = vOUT vDS VDD (a) VOUT 1 2 3 4 VIN (b) High roc ⇒ high noise margins 6.012 Spring 2007 Lecture 12 5 PMOS as current-source pull-up I—V characteristics of PMOS: + S + VSG _ VSD G B − _ + IDp 5 V + D − V + G − V − D − ID(VSG,VSD) (a) = VSG 3.5 V 300 V = V + V = V − 1 V 250 (triode SD SG Tp SG region) V = 3 V 200 SG − IDp (µA) (saturation region) 150 = VSG 25 100 = 0, 0.5, VSG 1 V (cutoff region) V = 2 V 50 SG = VSG 1.5 V 12345 VSD (V) (b) Note: enhancement-mode PMOS has VTp <0. -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

Transistor Current Source

PY 452 Advanced Physics Laboratory Hans Hallen Electronics Labs One electronics project should be completed. If you do not know what an op-amp is, do either lab 2 or lab 3. A written report is due, and should include a discussion of the circuit with inserted equations and plots as appropriate to substantiate the words and show that the measurements were taken. The report should not consist of the numbered items below and short answers, but should be one coherent discussion that addresses most of the issues brought out in the numbered items below. This is not an electronics course. Familiarity with electronics concepts such as input and output impedance, noise sources and where they matter, etc. are important in the lab AND SHOULD APPEAR IN THE REPORT. The objective of this exercise is to gain familiarity with these concepts. Electronics Lab #1 Transistor Current Source Task: Build and test a transistor current source, , +V with your choice of current (but don't exceed the transistor, power supply, or R ratings). R1 Rload You may wish to try more than one current. (1) Explain your choice of R1, R2, and Rsense. VCE (a) In particular, use the 0.6 V drop of VBE - rule for current flow to calculate I in R2 VBE Rsense terms of Rsense, and the Ic/Ib rule to estimate Ib hence the values of R1&R2. (2) Try your source over a wide range of Rload values, plot Iload vs. Rload and interpret. You may find it instructive to look at VBE and VCE with a floating (neither side grounded) multimeter. -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

Current Source & Source Transformation Notes

EE301 – CURRENT SOURCES / SOURCE CONVERSION Learning Objectives a. Analyze a circuit consisting of a current source, voltage source and resistors b. Convert a current source and a resister into an equivalent circuit consisting of a voltage source and a resistor c. Evaluate a circuit that contains several current sources in parallel Ideal sources An ideal source is an active element that provides a specified voltage or current that is completely independent of other circuit elements. DC Voltage DC Current Source Source Constant Current Sources The voltage across the current source (Vs) is dependent on how other components are connected to it. Additionally, the current source voltage polarity does not have to follow the current source’s arrow! 1 Example: Determine VS in the circuit shown below. Solution: 2 Example: Determine VS in the circuit shown above, but with R2 replaced by a 6 k resistor. Solution: 1 8/31/2016 EE301 – CURRENT SOURCES / SOURCE CONVERSION 3 Example: Determine I1 and I2 in the circuit shown below. Solution: 4 Example: Determine I1 and VS in the circuit shown below. Solution: Practical voltage sources A real or practical source supplies its rated voltage when its terminals are not connected to a load (open- circuited) but its voltage drops off as the current it supplies increases. We can model a practical voltage source using an ideal source Vs in series with an internal resistance Rs. Practical current source A practical current source supplies its rated current when its terminals are short-circuited but its current drops off as the load resistance increases. We can model a practical current source using an ideal current source in parallel with an internal resistance Rs. -

Physical Structure of CMOS Integrated Circuits

Physical Structure of CMOS Integrated Circuits Dae Hyun Kim EECS Washington State University References • John P. Uyemura, “Introduction to VLSI Circuits and Systems,” 2002. – Chapter 3 • Neil H. Weste and David M. Harris, “CMOS VLSI Design: A Circuits and Systems Perspective,” 2011. – Chapter 1 Goal • Understand the physical structure of CMOS integrated circuits (ICs) Logical vs. Physical • Logical structure • Physical structure Source: http://www.vlsi-expert.com/2014/11/cmos-layout-design.html Integrated Circuit Layers • Semiconductor – Transistors (active elements) • Conductor – Metal (interconnect) • Wire • Via • Insulator – Separators Integrated Circuit Layers • Silicon substrate, insulator, and two wires (3D view) Substrate • Side view Metal 1 layer Insulator Substrate • Top view Integrated Circuit Layers • Two metal layers separated by insulator (side view) Metal 2 layer Via 12 (connecting M1 and M2) Insulator Metal 1 layer Insulator Substrate • Top view Connected Not connected Integrated Circuit Layers Integrated Circuit Layers • Signal transfer speed is affected by the interconnect resistance and capacitance. – Resistance ↑ => Signal delay ↑ – Capacitance ↑ => Signal delay ↑ Integrated Circuit Layers • Resistance – = = = Direction of • : sheet resistance (constant) current flows ∙ ∙ • : resistivity (= , : conductivity) 1 – Material property (constant) – Unit: • : thickess (constant) Ω ∙ • : width (variable) • : length (variable) Cross-sectional area = • Example ∙ – : 17. , : 0.13 , : , : 1000 • = 17.1