AMD SP5100 Databook 44409 Rev

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

AMD Opteron™ 4000 Series Platform Quick Reference Guide

AMD Opteron™ 4000 Series Platform Quick Reference Guide The AMD Opteron™ 4100 Series processor, the world’s lowest power per core processor1, sets the foundation for cloud workloads and affordability for mainstream infrastructure servers with prices starting at $992. AMD Opteron™ 4100 Series Processor END USER BENEFITS Outstanding Performance-Per-Watt > Designed from the ground up to handle demanding server workloads at the lowest available energy draw, beating the competition by as much as 40% (per/core).1 Business Value > The world’s first 1P and 2P capable processor at sub $100 pricing.2 Easy to Purchase and Operate > Scalable solutions with feature, component and platform consistency. PRODUCT FEATURES New AMD-P 2.0 Power Savings Features: > Ultra-low power platforms provide power efficiency beyond just the processor, 3 SOUNDBITE for both 1P and 2P server configurations. THE WORLD’S LOWEST POWER PER CORE SERVER PROCESSOR1 > APML (Advanced Platform Management Link)4 provides an interface for processor and systems management monitoring and controlling of system resources such as platform power Quick Features consumption via p-state limits and CPU thermals to closely monitor power and cooling. AMD-P 2.0: > Link Width PowerCap which changes all 16-bit links to 8-bit links5 can help power conscious Ultra-low power platform > customers improve performance-per-watt. > Advanced Platform Management Link (APML)4 > AMD CoolSpeed Technology reduces p-states when a temperature limit is reached to allow a > Link Width PowerCap server to operate if the processor’s thermal environment exceeds safe operational limits. > AMD CoolSpeed Technology > When C1E5,6 is enabled, the cores, southbridge and memory controller enter a sleep state that > C1E6 can equate to significant power savings in the datacenter depending on system configuration. -

AMD's Early Processor Lines, up to the Hammer Family (Families K8

AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) Dezső Sima October 2018 (Ver. 1.1) Sima Dezső, 2018 AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) • 1. Introduction to AMD’s processor families • 2. AMD’s 32-bit x86 families • 3. Migration of 32-bit ISAs and microarchitectures to 64-bit • 4. Overview of AMD’s K8 – K10.5 (Hammer-based) families • 5. The K8 (Hammer) family • 6. The K10 Barcelona family • 7. The K10.5 Shanghai family • 8. The K10.5 Istambul family • 9. The K10.5-based Magny-Course/Lisbon family • 10. References 1. Introduction to AMD’s processor families 1. Introduction to AMD’s processor families (1) 1. Introduction to AMD’s processor families AMD’s early x86 processor history [1] AMD’s own processors Second sourced processors 1. Introduction to AMD’s processor families (2) Evolution of AMD’s early processors [2] 1. Introduction to AMD’s processor families (3) Historical remarks 1) Beyond x86 processors AMD also designed and marketed two embedded processor families; • the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and • the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95). In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm’s K5 effort, in order to focus on x86 processors [3]. 2) Initially, AMD designed the Am386/486 processors that were clones of Intel’s processors. -

SMBIOS Specification

1 2 Document Identifier: DSP0134 3 Date: 2019-10-31 4 Version: 3.4.0a 5 System Management BIOS (SMBIOS) Reference 6 Specification Information for Work-in-Progress version: IMPORTANT: This document is not a standard. It does not necessarily reflect the views of the DMTF or its members. Because this document is a Work in Progress, this document may still change, perhaps profoundly and without notice. This document is available for public review and comment until superseded. Provide any comments through the DMTF Feedback Portal: http://www.dmtf.org/standards/feedback 7 Supersedes: 3.3.0 8 Document Class: Normative 9 Document Status: Work in Progress 10 Document Language: en-US 11 System Management BIOS (SMBIOS) Reference Specification DSP0134 12 Copyright Notice 13 Copyright © 2000, 2002, 2004–2019 DMTF. All rights reserved. 14 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 15 management and interoperability. Members and non-members may reproduce DMTF specifications and 16 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 17 time, the particular version and release date should always be noted. 18 Implementation of certain elements of this standard or proposed standard may be subject to third party 19 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 20 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 21 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 22 inaccurate identification or disclosure of such rights, owners or claimants. -

Six-Core AMD Opteron™ Processor with AMD

AMD最新テクノロジーアップデート -HPCへの取り組み- 日本AMD株式会社 マーケティング&ビジネス開発本部 エンタープライズプロダクトマーケティング部 部長 山野 洋幸 AMD’s HPC Product Portfolio Energy efficient CPU and discrete GPU processors focused on addressing the most demanding HPC workloads Multi-core x86 Processors • Outstanding Performance • Superior Scalability • Enhanced Power Efficiency Professional Graphics • 3D Accelerators For Visualization • See More and Do More with Your Data ATI Stream Computing • GPU Optimized For Computation • Massive Data-parallel Processing • High Performance Per Watt 2 | AMD HPC Product Portfolio Update @ SC’09 | November 30, 2009 For more information be sure to visit AMD at SC’09 booth #1417 AMD’s HPC Product Portfolio Energy efficient CPU and discrete GPU processors focused on addressing the most demanding HPC workloads Multi-core x86 Processors • Outstanding Performance • Superior Scalability • Enhanced Power Efficiency Professional Graphics • 3D Accelerators For Visualization • See More and Do More with Your Data ATI Stream Computing • GPU Optimized For Computation • Massive Data-parallel Processing • High Performance Per Watt 3 | AMD HPC Product Portfolio Update @ SC’09 | November 30, 2009 For more information be sure to visit AMD at SC’09 booth #1417 Planned Server Platform Roadmap 2006 2007 2008 2009 2010 2011 “Maranello” Socket G34 with AMD SR56x0 and SP5100 Magny-Cours New Architecture Six-Core AMD Opteron™ Processor with AMD way Chipset - Socket F(1207) with AMD SR56x0 and SP5100 Shanghai/Istanbul Platform 2/4 Enterprise Enterprise “Socket F (1207)” Socket F(1207) -

Lista Sockets.Xlsx

Data de Processadores Socket Número de pinos lançamento compatíveis Socket 0 168 1989 486 DX 486 DX 486 DX2 Socket 1 169 ND 486 SX 486 SX2 486 DX 486 DX2 486 SX Socket 2 238 ND 486 SX2 Pentium Overdrive 486 DX 486 DX2 486 DX4 486 SX Socket 3 237 ND 486 SX2 Pentium Overdrive 5x86 Socket 4 273 março de 1993 Pentium-60 e Pentium-66 Pentium-75 até o Pentium- Socket 5 320 março de 1994 120 486 DX 486 DX2 486 DX4 Socket 6 235 nunca lançado 486 SX 486 SX2 Pentium Overdrive 5x86 Socket 463 463 1994 Nx586 Pentium-75 até o Pentium- 200 Pentium MMX K5 Socket 7 321 junho de 1995 K6 6x86 6x86MX MII Slot 1 Pentium II SC242 Pentium III (Cartucho) 242 maio de 1997 Celeron SEPP (Cartucho) K6-2 Socket Super 7 321 maio de 1998 K6-III Celeron (Socket 370) Pentium III FC-PGA Socket 370 370 agosto de 1998 Cyrix III C3 Slot A 242 junho de 1999 Athlon (Cartucho) Socket 462 Athlon (Socket 462) Socket A Athlon XP 453 junho de 2000 Athlon MP Duron Sempron (Socket 462) Socket 423 423 novembro de 2000 Pentium 4 (Socket 423) PGA423 Socket 478 Pentium 4 (Socket 478) mPGA478B Celeron (Socket 478) 478 agosto de 2001 Celeron D (Socket 478) Pentium 4 Extreme Edition (Socket 478) Athlon 64 (Socket 754) Socket 754 754 setembro de 2003 Sempron (Socket 754) Socket 940 940 setembro de 2003 Athlon 64 FX (Socket 940) Athlon 64 (Socket 939) Athlon 64 FX (Socket 939) Socket 939 939 junho de 2004 Athlon 64 X2 (Socket 939) Sempron (Socket 939) LGA775 Pentium 4 (LGA775) Pentium 4 Extreme Edition Socket T (LGA775) Pentium D Pentium Extreme Edition Celeron D (LGA 775) 775 agosto de -

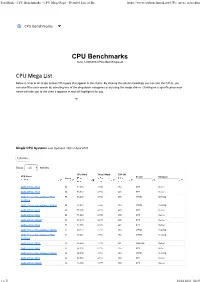

Passmark - CPU Benchmarks - CPU Mega Page - Detailed List of Be

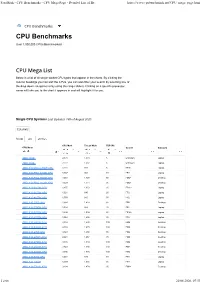

PassMark - CPU Benchmarks - CPU Mega Page - Detailed List of Be... https://www.cpubenchmark.net/CPU_mega_page.html CPU Benchmarks Over 1,000,000 CPUs Benchmarked Below is a list of all single socket CPU types that appear in the charts. By clicking the column headings you can sort the CPUs, you can also filter your search by selecting one of the drop down categories or by using the range sliders. Clicking on a specific processor name will take you to the chart it appears in and will highlight it for you. Single CPU Systems Last Updated: 19th of August 2020 CPU Mark Thread Mark TDP (W) CPU Name Socket Category - - - ▲ AMD 3015e 2,678 1,408 6 Unknown Laptop AMD 3020e 2,727 1,507 6 Unknown Laptop AMD A10 Micro-6700T APU 1,291 703 5 FT3b Laptop AMD A10 PRO-7350B APU 1,857 941 19 FP3 Laptop AMD A10 PRO-7800B APU 3,003 1,428 65 FM2+ Desktop AMD A10 PRO-7850B APU 3,329 1,571 95 FM2+ Desktop AMD A10-4600M APU 1,855 1,059 35 FS1r2 Laptop AMD A10-4655M APU 1,621 895 25 FP2 Laptop AMD A10-4657M APU 1,759 940 35 FP2 Laptop AMD A10-5700 APU 2,664 1,428 65 FM2 Desktop AMD A10-5745M APU 1,524 888 25 FP2 Laptop AMD A10-5750M APU 1,896 1,094 35 FS1r2 Laptop AMD A10-5757M APU 1,963 1,206 35 FP2 Laptop AMD A10-5800B APU 3,014 1,599 100 FM2 Desktop AMD A10-5800K APU 2,910 1,479 100 FM2 Desktop AMD A10-6700 APU 3,123 1,650 65 FM2 Desktop AMD A10-6700T APU 2,224 1,267 45 FM2 Desktop AMD A10-6790K APU 3,095 1,634 100 FM2 Desktop AMD A10-6800B APU 2,543 1,398 100 FM2 Desktop AMD A10-6800K APU 3,096 1,585 100 FM2 Desktop AMD A10-7300 APU 1,664 839 19 FP3 Laptop AMD A10-7400P 1,969 1,055 35 FP3 Laptop AMD A10-7700K APU 3,234 1,474 95 FM2+ Desktop 1 z 66 20.08.2020, 07:53 PassMark - CPU Benchmarks - CPU Mega Page - Detailed List of Be.. -

SMBIOS) Reference 6 Specification

1 2 Document Identifier: DSP0134 3 Date: 2018-04-26 4 Version: 3.2.0 5 System Management BIOS (SMBIOS) Reference 6 Specification 7 Supersedes: 3.1.1 8 Document Class: Normative 9 Document Status: Published 10 Document Language: en-US 11 System Management BIOS (SMBIOS) Reference Specification DSP0134 12 Copyright Notice 13 Copyright © 2000, 2002, 2004–2016 Distributed Management Task Force, Inc. (DMTF). All rights 14 reserved. 15 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 16 management and interoperability. Members and non-members may reproduce DMTF specifications and 17 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 18 time, the particular version and release date should always be noted. 19 Implementation of certain elements of this standard or proposed standard may be subject to third party 20 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 21 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 22 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 23 inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to 24 any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, 25 disclose, or identify any such third party patent rights, or for such party’s reliance on the standard or 26 incorporation thereof in its product, protocols or testing procedures. -

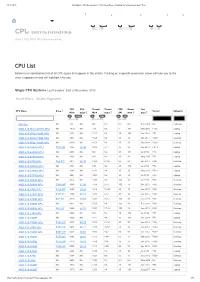

Passmark - CPU Benchmarks - CPU Mega Page - Detailed List of Be

PassMark - CPU Benchmarks - CPU Mega Page - Detailed List of Be... https://www.cpubenchmark.net/CPU_mega_page.html CPU Benchmarks Over 1,000,000 CPUs Benchmarked Below is a list of all single socket CPU types that appear in the charts. By clicking the column headings you can sort the CPUs, you can also filter your search by selecting one of the drop down categories or by using the range sliders. Clicking on a specific processor name will take you to the chart it appears in and will highlight it for you. AD Single CPU Systems Last Updated: 13th of April 2021 CPU Mark Thread Mark TDP (W) CPU Name Socket Category Cores - - - ▼ AMD EPYC 7763 64 87,686 2,639 280 SP3 Server AMD EPYC 7713 64 86,512 2,752 225 SP3 Server AMD Ryzen Threadripper PRO 64 85,520 2,655 280 sTRX4 Desktop 3995WX AMD Ryzen Threadripper 3990X 64 80,972 2,555 280 sTRX4 Desktop AMD EPYC 7643 48 77,101 2,713 225 SP3 Server AMD EPYC 7702 64 71,929 2,099 200 SP3 Server AMD EPYC 7702P 64 68,213 2,210 200 SP3 Server AMD EPYC 7742 64 67,185 2,376 225 SP3 Server AMD Ryzen Threadripper 3970X 32 64,217 2,712 280 sTRX4 Desktop AMD Ryzen Threadripper PRO 32 63,442 2,665 280 sTRX4 Desktop 3975WX AMD EPYC 7R32 48 58,556 1,737 NA Unknown Server AMD EPYC 7542 32 56,310 2,216 225 SP3 Server AMD Ryzen Threadripper 3960X 24 54,890 2,682 280 sTRX4 Desktop AMD EPYC 7502 32 53,591 2,116 180 SP3 Server AMD EPYC 7502P 32 46,180 1,777 180 SP3 Server 1 z 71 14.04.2021, 08:39 PassMark - CPU Benchmarks - CPU Mega Page - Detailed List of Be.. -

AMD Opteron™ 4000 Series Platform Quick Reference Guide

AMD Opteron™ 4000 Series Platform Quick Reference Guide The world’s lowest power x86 cloud processor1 just got more efficient AMD Opteron™ 4200 Series Processor END USER BENEFITS > Efficiently scales performance/watt based on the innovative Designed for enterprise workloads while still delivering a modular design and aggressive power capabilities performance punch > New power saving features, like TDP Power Cap, put the > A 33% increase in core count packs in plenty of processing customer in control of more aspects of power efficiency than performance into a smaller, more efficient, 8-core design while ever before on AMD Opteron™ processor-based servers 4,5 maintaining very aggressive power/thermal ranges > Up to 8 cores and more processing throughput7 helps your > Power per core that shatters the 5W/core mark, a new record cloud easily scale within the most fluid and spiky processing 1 for an enterprise-class x86 processor environments, easily responding to the elastic needs of clouds > New power management capabilities allow for larger parts of the processor to be almost completely powered off Bringing unparalleled efficiency to your processing, power and when not being used, dramatically reducing idle core power financial budgets consumption by up to 37% over today’s AMD Opteron™ 4100 > The lowest enterprise-class power per core with up to 8 cores KEY FEATURES Series processors and allowing active cores to run at a higher in only 35W of power, shattering the previous record1 >>New>‘Bulldozer’-core>Architecture — drives more core frequency6 -

Title (Arial Bold Italic 20Pt)

CONSUMERIZATION, CLOUD, CONVERGENCE. AMD 2012 Financial Analyst Day February 2, 2012 AMD Product and Technology Roadmaps AMD 2012 Desktop Graphics Roadmap 2011: Codename “Northern Islands” 2012: Codename “Southern Islands” AMD Radeon™ 6990 GPU AMD Radeon™ 7000 Series GPU Ultra Enthusiast Graphics Card Enthusiast AMD Radeon™ 6900 Series GPUs AMD Radeon™ 7900 Series GPU Codename: “Tahiti” AMD Radeon™ 6800 Series GPUs AMD Radeon™ 7000 Series GPU Codename: “Pitcairn” Performance AMD Radeon™ 6700 Series GPUs AMD Radeon™ 7000 Series GPU Codename: “Cape Verde” AMD Radeon™ 6600 Series GPUs Mainstream AMD Radeon™ 6500 Series GPUs AMD Radeon™ 6450 GPU Value AMD roadmaps are subject to change without notice 2 | 2012 Financial Analyst Day | February 2, 2012 | Consumerization, Cloud, Convergence. | Confidential AMD 2012 Notebook Graphics Roadmap 2011: Codename “Vancouver” 2012: Codename “London” AMD Radeon™ 6900M Series GPUs AMD Radeon™ 7000M Series GPUs GCN Architecture Series Enthusiast AMD Radeon™ 6800M Series GPUs AMD Radeon™ 6700M Series GPUs Performance AMD Radeon™ 6600M Series GPUs AMD Radeon™ 7600M Series GPUs Terascale II Architecture Series AMD Radeon™ 6500M Series GPUs AMD Radeon™ 7500M Series GPUs Terascale II Architecture Series Mainstream AMD Radeon™ 6400M Series GPUs AMD Radeon™ 7400M Series GPUs Terascale II Architecture Series AMD Radeon™ 6300M Series GPUs Value AMD roadmaps are subject to change without notice 3 | 2012 Financial Analyst Day | February 2, 2012 | Consumerization, Cloud, Convergence. | Confidential AMD 2012-2013 Desktop -

CPU Benchmarks - CPU Mega Page - Detailed List of Benchmarked Cpus

29.11.2019 PassMark - CPU Benchmarks - CPU Mega Page - Detailed List of Benchmarked CPUs 1 2 3 4 5 1 1 40000 1 4000 1 400 2 3 4 5 1 40000 1 4000 1 400 CPU Benchmarks Over 1,000,000 CPUs Benchmarked CPU List Below is an alphabetical list of all CPU types that appear in the charts. Clicking on a specific processor name will take you to the chart it appears in and will highlight it for you. Single CPU Systems Last Updated: 29th of November 2019 Reset Filters Enable Pagination CPU CPU Thread Thread TDP Power Test CPU Name Price 1 Socket Category Mark Value 2 Mark Value 3 (W) Perf. 4 Date 5 1 40000 1 4000 1 400 686 Gen NA 288 NA NA NA NA NA Feb 2009 NA Unknown AMD A10 Micro-6700T APU NA 1970 NA 778 NA 5 394 May 2015 FT3b Laptop AMD A10 PRO-7350B APU NA 3152 NA 1012 NA 19 165 Jun 2014 FP3 Laptop AMD A10 PRO-7800B APU NA 4997 NA 1559 NA 65 76 Oct 2014 FM2+ Desktop AMD A10 PRO-7850B APU NA 5380 NA 1601 NA 95 56 Nov 2014 FM2+ Desktop AMD A10-4600M APU $109.95 3115 28.34 1005 9.14 35 89 Apr 2012 FS1r2 Laptop AMD A10-4655M APU NA 2605 NA 861 NA 25 104 Jul 2012 FP2 Laptop AMD A10-4657M APU NA 2906 NA 887 NA 35 83 May 2013 FP2 Laptop AMD A10-5700 APU $64.50* 4214 65.35 1358 21.06 65 64 Jun 2012 FM2 Desktop AMD A10-5745M APU NA 2764 NA 913 NA 25 110 Jul 2013 FP2 Laptop AMD A10-5750M APU NA 3340 NA 1108 NA 35 95 May 2013 FS1r2 Laptop AMD A10-5757M APU NA 3084 NA 1063 NA 35 88 Jul 2013 FP2 Laptop AMD A10-5800B APU NA 4614 NA 1489 NA 100 46 Jul 2013 FM2 Desktop AMD A10-5800K APU $149.99* 4649 31.00 1458 9.72 100 46 Oct 2012 FM2 Desktop AMD A10-6700 APU -

The World's First 16-Core X86 Processor, Delivering a Rich Mix Of

AMD OPTERON ™ 6000 SERIES EMBEDDED PLATFORM: The world’s first 16-core x86 processor, delivering a rich mix of performance, scalability and efficiency for today’s highly threaded computing environments MULTITHREADED PERFORMANCE, SCALABLE, Technical applications like military command and control systems WITH PLATFORM LONGEVITY and medical imaging can take advantage of the innovative design ™ The AMD Opteron 6300 Series Embedded processor is a 16-core of the Flex FP that brings 256-bit floating point processing to the x86 processor, delivering a rich mix of performance, scalability and mainstream with more throughput for both 128-bit and 256-bit efficiency for today’s highly threaded embedded environments such technical applications. In addition, the FMAC units in the Flex FP as networking, storage and medical imaging systems. These high help boost computational horsepower, driving more performance by performance scalable applications benefit from the modular design executing FMA4 instructions and offer up to 140% more GFLOPs 1 that offer from 60-100% more cores than competition and improved in 128-bit mode and up to 20% more in 256-bit mode compared to 2 performance than AMD’s current products. similarly-price competitive processors.4 AVX and SSE instructions can also be performed in one cycle on the two different Flex FP The AMD Opteron 6300 Series Embedded processor delivers pipelines. With up to eight 256-bit Flex FP units, which can also act the highest number of x86 CPU cores for challenging embedded as 16 128-bit FPUs, the AMD Opteron 6300 Series Embedded enterprise workloads yet still delivers a scalable punch in a processor is capable of delivering up to 332.8 GFLOPs per 2P node.5 given system power budget and provides robust configurations in a platform that leverages previous versions of Core network routers and storage appliances require high AMD Opteron 6000 Series Embedded processors.