A Graphene/Polycrystalline Silicon Photodiode and Its Integration in a Photodiode–Oxide–Semiconductor Field Effect Transistor

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Photodiode and LIGHT EMITTING DIODE

Photodiode and LIGHT EMITTING DIODE Presentation by JASWANT KUMAR ROLL NO.-12 rd IT(3 SEM.) 1 About LEDs (1/2) • A light emitting diode (LED) is essentially a PN junction opto- semiconductor that emits a monochromatic (single color) light when operated in a forward biased direction. • LEDs convert electrical energy into light energy. LED SYMBOL 2 ABOUT LEDS (2/2) • The most important part of a light emitting diode (LED) is the semi-conductor chip located in the center of the bulb as shown at the right. • The chip has two regions separated by a junction. • The junction acts as a barrier to the flow of electrons between the p and the n regions. 3 LED CIRCUIT • In electronics, the basic LED circuit is an electric power circuit used to power a light-emitting diode or LED. The simplest such circuit consists of a voltage source and two components connect in series: a current-limiting resistor (sometimes called the ballast resistor), and an LED. Optionally, a switch may be introduced to open and close the circuit. The switch may be replaced with another component or circuit to form a continuity tester. 4 HOW DOES A LED WORK? • Each time an electron recombines with a positive charge, electric potential energy is converted into electromagnetic energy. • For each recombination of a negative and a positive charge, a quantum of electromagnetic energy is emitted in the form of a photon of light with a frequency characteristic of the semi- conductor material. 5 Mechanism behind photon emission in LEDs? MechanismMechanism isis “injection“injection Electroluminescence”.Electroluminescence”. -

Integrated High-Speed, High-Sensitivity Photodiodes and Optoelectronic Integrated Circuits

Sensors and Materials, Vol. 13, No. 4 (2001) 189-206 MYUTokyo S &M0442 Integrated High-Speed, High-Sensitivity Photodiodes and Optoelectronic Integrated Circuits Horst Zimmermann Institut fiirElektrische Mess- und Schaltungstechnik, Technische Universitat Wien, Gusshausstrasse, A-1040 Wien, Austria (Received February 28, 2000; accepted February3, 2001) Key words: integrated circuits, integrated optoelectronics, optical receivers, optoelectronic de vices, PIN photodiode, double photodiode, silicon A review of the properties of photodiodes available through the use of standard silicon technologies is presented and some examples of how to improve monolithically integrated photodiodes are shown. The application of these photodiodes in optoelectronic integrated circuits (OEICs) is described. An innovative double photodiode requiring no process modificationsin complementary metal-oxide sem!conductor (CMOS) and bipolar CMOS (BiCMOS) technologies achieves a bandwidth in excess of 360 MHzand data rates exceeding 622 Mb/s. Furthermore, a new PIN photodiode requiring only one additional mask for the integration in a CMOS process is capable of handling a data rate of 1.1 Gb/s. Antireflection coating improves the quantum efficiencyof integrated photodiodes to values of more than 90%. Integrated optical receivers for data communication achieve a high bandwidth and a high sensitivity. Furthermore, an OEIC for application in optical storage systems is introduced. Author's e-mail address: [email protected] 189 l 90 Sensors and Materials, Vol. 13, No. 4 (2001) 1. Introduction Photons with an energy larger than the band gap generate electron-hole pairs in semiconductors. This photogeneration G obeys an exponential law: aP,0 G( x) = -- exp( -ax), Ahv (1) where xis the penetration depth coordinate, P0 is the nonreflectedportion of the incident optical power, A is the light-sensitive area of a photodiode, hv is the energy of the photon, and a is the wavelength-dependent absorption coefficient. -

Leds As Single-Photon Avalanche Photodiodes by Jonathan Newport, American University

LEDs as Single-Photon Avalanche Photodiodes by Jonathan Newport, American University Lab Objectives: Use a photon detector to illustrate properties of random counting experiments. Use limiting probability distributions to perform statistical analysis on a physical system. Plot histograms. Condition a detector’s signal for further electronic processing. Use a breadboard, power supply and oscilloscope to construct a circuit and make measurements. Learn about semiconductor device physics. Reading: Taylor 3.2 – The Square-Root Rule for a Counting Experiment pp. 48-49 Taylor 5.1-5.3 – Histograms and the Normal Distribution pp. 121-135 Taylor Ch. 11 – The Poisson Distribution pp. 245-254 Taylor Problem 5.6 – The Exponential Distribution p. 155 Experiment #1: Lighting an LED A Light-Emitting Diode is a non-linear circuit element that can produce a controlled amount of light. The AND113R datasheet shows that the luminous intensity is proportional to the current flowing through the LED. As illustrated in the IV curve shown below, the current flowing through the diode is in turn proportional to the voltage across the diode. Diodes behave like a one-way valve for current. When the voltage on the Anode is more positive than the voltage on the Cathode, then the diode is said to be in Forward Bias. As the voltage across the diode increases, the current through the diode increases dramatically. The heat generated by this current can easily destroy the device. It is therefore wise to install a current-limiting resistor in series with the diode to prevent thermal runaway. When the voltage on the Cathode is more positive than the voltage on the Anode, the diode is said to be in Reverse Bias. -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

Bipolar Junction Transistor As a Detector for Measuring in Diagnostic X-Ray Beams

2013 International Nuclear Atlantic Conference - INAC 2013 Recife, PE, Brazil, November 24-29, 2013 ASSOCIAÇÃO BRASILEIRA DE ENERGIA NUCLEAR - ABEN ISBN: 978-85-99141-05-2 BIPOLAR JUNCTION TRANSISTOR AS A DETECTOR FOR MEASURING IN DIAGNOSTIC X-RAY BEAMS Francisco A. Cavalcanti1,2, David S. Monte1,2, Aline N. Alves1,2, Fábio R. Barros2, Marcus A. P. Santos2, and Luiz A. P. Santos1,2 1 Departamento de Energia Nuclear Universidade Federal de Pernambuco Av. Prof. Luiz Freire, 1000 50740-540 Recife, PE [email protected] 2 Centro Regional de Ciências Nucleares do Nordeste (CRCN-NE / CNEN) Av. Prof. Luiz Freire, 1 50740-540 Recife, PE [email protected] ABSTRACT Photodiode and phototransistor are the most frequently used devices for measuring ionizing radiation in medical applications. The cited devices have the operating principle well known, however the bipolar junction transistor (BJT) is not a typical device used as a detector for measuring some physical quantities for diagnostic radiation. In fact, a photodiode, for example, has an area about 10 mm square and a BJT has an area which can be more than 10 thousands times smaller. The purpose of this paper is to bring a new technique to estimate some physical quantities or parameters in diagnostic radiation; for example, peak kilovoltage (kVp), deep dose measurements. The methodology for each type of evaluation depends on the energy range of the radiation and the physical quantity or parameter to be measured. Actually, some characteristics of the incident radiation under the device can be correlated with the readout signal, which is a function of the electrical currents in the electrodes of the BJT: Collector, Base and Emitter. -

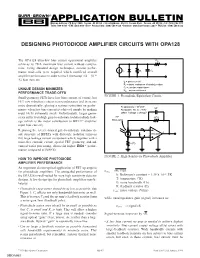

Designing Photodiode Amplifier Circuits with Opa128

® DESIGNING PHOTODIODE AMPLIFIER CIRCUITS WITH OPA128 The OPA128 ultra-low bias current operational amplifier RS achieves its 75fA maximum bias current without compro- mise. Using standard design techniques, serious perfor- I R C mance trade-offs were required which sacrificed overall P J J amplifier performance in order to reach femtoamp (fA = 10–15 A) bias currents. IP = photocurrent RJ = shunt resistance of diode junction CJ = junction capacitance UNIQUE DESIGN MINIMIZES R = series resistance PERFORMANCE TRADE-OFFS S FIGURE 1. Photodiode Equivalent Circuit. Small-geometry FETs have low bias current, of course, but FET size reduction reduces transconductance and increases noise dramatically, placing a serious restriction on perfor- Responsivity ≈ 109V/W 5pF mance when low bias current is achieved simply by making Bandwidth: DC to ≈ 30Hz input FETs extremely small. Unfortunately, larger geom- Offset Voltage ≈ ±485µV etries suffer from high gate-to-substrate isolation diode leak- HP 109Ω age (which is the major contribution to BIFET® amplifier 5082-4204 input bias current). Replacing the reverse-biased gate-to-substrate isolation di- 2 6 OPA128LM ode structure of BlFETs with dielectric isolation removes 3 this large leakage current component which, together with a 8 noise-free cascode circuit, special FET geometry, and ad- 109Ω vanced wafer processing, allows far higher Difet ® perfor- mance compared to BIFETs. FIGURE 2. High-Sensitivity Photodiode Amplifier. HOW TO IMPROVE PHOTODIODE AMPLIFIER PERFORMANCE An important electro-optical application of FET op amps is √ for photodiode amplifiers. The unequaled performance of eOUT = 4k TBR the OPA128 is well-suited for very high sensitivity detector k: Boltzman’s constant = 1.38 x 10–23 J/K ° designs. -

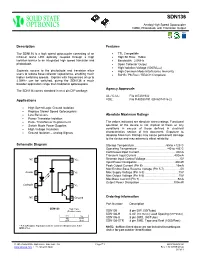

SDN136 Analog High Speed Optocoupler 1Mbd, Photodiode with Transistor Output

SDN136 Analog High Speed Optocoupler 1MBd, Photodiode with Transistor Output Description Features The SDN136 is a high speed optocoupler consisting of an TTL Compatible infrared GaAs LED optically coupled through a high High Bit Rate: 1Mb/s isolation barrier to an integrated high speed transistor and Bandwidth: 2.0MHz photodiode. Open Collector Output High Isolation Voltage (5000VRMS) Separate access to the photodiode and transistor allow High Common Mode Interference Immunity users to reduce base-collector capacitance, enabling much RoHS / Pb-Free / REACH Compliant higher switching speeds. Signals with frequencies of up to 2.0MHz can be switched, giving the SDN136 a much broader application range than traditional optocouplers. Agency Approvals The SDN136 comes standard in an 8 pin DIP package. UL / C-UL: File # E201932 Applications VDE: File # 40035191 (EN 60747-5-2) High Speed Logic Ground Isolation Replace Slower Speed Optocouplers Absolute Maximum Ratings Line Receivers Power Transistor Isolation Pulse Transformer Replacement The values indicated are absolute stress ratings. Functional Switch Mode Power Supplies operation of the device is not implied at these or any High Voltage Insulation conditions in excess of those defined in electrical Ground Isolation – Analog Signals characteristics section of this document. Exposure to absolute Maximum Ratings may cause permanent damage to the device and may adversely affect reliability. Schematic Diagram Storage Temperature …………………………..-55 to +125°C Operating Temperature …………………………-40 -

MOS Caps II; Mosfets I

6.012 - Microelectronic Devices and Circuits Lecture 10 - MOS Caps II; MOSFETs I - Outline G cS vGS + SiO2 – • Review - MOS Capacitor (= vGB) The "Delta-Depletion Approximation" n+ (n-MOS example) p-Si Flat-band voltage: VFB ≡ vGB such that φ(0) = φp-Si: VFB = φp-Si – φm Threshold voltage: VT ≡ vGB such B 1/2 * that φ(0) = – φp-Si: VT = VFB – 2φp-Si + [2εSi qNA|2φp-Si| ] /Cox * * Inversion layer sheet charge density: qN = – Cox [vGC – VT] • Charge stores - qG(vGB) from below VFB to above VT Gate Charge: qG(vGB) from below VFB to above VT Gate Capacitance: Cgb(VGB) Sub-threshold charge: qN(vGB) below VT • 3-Terminal MOS Capacitors - Bias between B and C Impact is on VT(vBC): |2φp-Si| → (|2φp-Si| - vBC) • MOS Field Effect Transistors - Basics of model Gradual Channel Model: electrostatics problem normal to channel drift problem in the plane of the channel Clif Fonstad, 10/15/09 Lecture 10 - Slide 1 G CS vGS + SiO2 – (= vGB) The n-MOS capacitor n+ Right: Basic device p-Si with vBC = 0 B Below: One-dimensional structure for depletion approximation analysis* vGB + – SiO 2 p-Si G B x -tox 0 * Note: We can't forget the n+ region is there; we Clif Fonstad, 10/15/09 will need electrons, and they will come from there. Lecture 10 - Slide 2 MOS Capacitors: Where do the electrons in the inversion layer come from? Diffusion from the p-type substrate? If we relied on diffusion of minority carrier electrons from the p-type substrate it would take a long time to build up the inversion layer charge. -

Photovoltaic Couplers for MOSFET Drive for Relays

Photocoupler Application Notes Basic Electrical Characteristics and Application Circuit Design of Photovoltaic Couplers for MOSFET Drive for Relays Outline: Photovoltaic-output photocouplers(photovoltaic couplers), which incorporate a photodiode array as an output device, are commonly used in combination with a discrete MOSFET(s) to form a semiconductor relay. This application note discusses the electrical characteristics and application circuits of photovoltaic-output photocouplers. ©2019 1 Rev. 1.0 2019-04-25 Toshiba Electronic Devices & Storage Corporation Photocoupler Application Notes Table of Contents 1. What is a photovoltaic-output photocoupler? ............................................................ 3 1.1 Structure of a photovoltaic-output photocoupler .................................................... 3 1.2 Principle of operation of a photovoltaic-output photocoupler .................................... 3 1.3 Basic usage of photovoltaic-output photocouplers .................................................. 4 1.4 Advantages of PV+MOSFET combinations ............................................................. 5 1.5 Types of photovoltaic-output photocouplers .......................................................... 7 2. Major electrical characteristics and behavior of photovoltaic-output photocouplers ........ 8 2.1 VOC-IF characteristics .......................................................................................... 9 2.2 VOC-Ta characteristic ........................................................................................ -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Power MOSFET Basics by Vrej Barkhordarian, International Rectifier, El Segundo, Ca

Power MOSFET Basics By Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Breakdown Voltage......................................... 5 On-resistance.................................................. 6 Transconductance............................................ 6 Threshold Voltage........................................... 7 Diode Forward Voltage.................................. 7 Power Dissipation........................................... 7 Dynamic Characteristics................................ 8 Gate Charge.................................................... 10 dV/dt Capability............................................... 11 www.irf.com Power MOSFET Basics Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Discrete power MOSFETs Source Field Gate Gate Drain employ semiconductor Contact Oxide Oxide Metallization Contact processing techniques that are similar to those of today's VLSI circuits, although the device geometry, voltage and current n* Drain levels are significantly different n* Source t from the design used in VLSI ox devices. The metal oxide semiconductor field effect p-Substrate transistor (MOSFET) is based on the original field-effect Channel l transistor introduced in the 70s. Figure 1 shows the device schematic, transfer (a) characteristics and device symbol for a MOSFET. The ID invention of the power MOSFET was partly driven by the limitations of bipolar power junction transistors (BJTs) which, until recently, was the device of choice in power electronics applications. 0 0 V V Although it is not possible to T GS define absolutely the operating (b) boundaries of a power device, we will loosely refer to the I power device as any device D that can switch at least 1A. D The bipolar power transistor is a current controlled device. A SB (Channel or Substrate) large base drive current as G high as one-fifth of the collector current is required to S keep the device in the ON (c) state. Figure 1. Power MOSFET (a) Schematic, (b) Transfer Characteristics, (c) Also, higher reverse base drive Device Symbol. -

(PPS) • CMOS Photodiode Active Pixel Sensor (APS) • Photoga

Lecture Notes 4 CMOS Image Sensors CMOS Passive Pixel Sensor (PPS) • Basic operation ◦ Charge to output voltage transfer function ◦ Readout speed ◦ CMOS Photodiode Active Pixel Sensor (APS) • Basic operation ◦ Charge to output voltage transfer function ◦ Readout speed ◦ Photogate and Pinned Diode APS • Multiplexed APS • EE 392B: CMOS Image Sensors 4-1 Introduction CMOS image sensors are fabricated in \standard" CMOS technologies • Their main advantage over CCDs is the ability to integrate analog and • digital circuits with the sensor Less chips used in imaging system ◦ Lower power dissipation ◦ Faster readout speeds ◦ More programmability ◦ New functionalities (high dynamic range, biometric, etc) ◦ But they generally have lower perofrmance than CCDs: • Standard CMOS technologies are not optimized for imaging ◦ More circuits result in more noise and fixed pattern noise ◦ In this lecture notes we discuss various CMOS imager architectures • In the following lecture notes we discuss fabrication and layout issues • EE 392B: CMOS Image Sensors 4-2 CMOS Image Sensor Architecture Word Pixel: Row Decoder Photodetector & Readout treansistors Bit Column Amplifiers/Caps Output Column Mux Readout performed by transferring one row at a time to the column • storage capacitors, then reading out the row, one (or more) pixel at a time, using the column decoder and multiplexer In many CMOS image sensor architectures, row integration times are • staggerred by the row/column readout time (scrolling shutter) EE 392B: CMOS Image Sensors 4-3 CMOS Image Sensor