AN-500: Depletion-Mode Power Mosfets and Applications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Imperial College London Department of Physics Graphene Field Effect

Imperial College London Department of Physics Graphene Field Effect Transistors arXiv:2010.10382v2 [cond-mat.mes-hall] 20 Jul 2021 By Mohamed Warda and Khodr Badih 20 July 2021 Abstract The past decade has seen rapid growth in the research area of graphene and its application to novel electronics. With Moore's law beginning to plateau, the need for post-silicon technology in industry is becoming more apparent. Moreover, exist- ing technologies are insufficient for implementing terahertz detectors and receivers, which are required for a number of applications including medical imaging and secu- rity scanning. Graphene is considered to be a key potential candidate for replacing silicon in existing CMOS technology as well as realizing field effect transistors for terahertz detection, due to its remarkable electronic properties, with observed elec- tronic mobilities reaching up to 2 × 105 cm2 V−1 s−1 in suspended graphene sam- ples. This report reviews the physics and electronic properties of graphene in the context of graphene transistor implementations. Common techniques used to syn- thesize graphene, such as mechanical exfoliation, chemical vapor deposition, and epitaxial growth are reviewed and compared. One of the challenges associated with realizing graphene transistors is that graphene is semimetallic, with a zero bandgap, which is troublesome in the context of digital electronics applications. Thus, the report also reviews different ways of opening a bandgap in graphene by using bi- layer graphene and graphene nanoribbons. The basic operation of a conventional field effect transistor is explained and key figures of merit used in the literature are extracted. Finally, a review of some examples of state-of-the-art graphene field effect transistors is presented, with particular focus on monolayer graphene, bilayer graphene, and graphene nanoribbons. -

Run Capacitor Info-98582

Run Cap Quiz-98582_Layout 1 4/16/15 10:26 AM Page 1 ® Run Capacitor Info WHAT IS A CAPACITOR? Very simply, a capacitor is a device that stores and discharges electrons. While you may hear capacitors referred to by a variety of names (condenser, run, start, oil, etc.) all capacitors are comprised of two or more metallic plates separated by an insulating material called a dielectric. PLATE 1 PLATE 2 A very simple capacitor can be made with two plates separated by a dielectric, in this PLATE 1 PLATE 2 case air, and connected to a source of DC current, a battery. Electrons will flow away from plate 1 and collect on plate 2, leaving it with an abundance of electrons, or a “charge”. Since current from a battery only flows one way, the capacitor plate will stay BATTERY + – charged this way unless something causes current flow. If we were to short across the plates with a screwdriver, the resulting spark would indicate the electrons “jumping” from plate 2 to plate 1 in an attempt to equalize. As soon as the screwdriver is removed, plate 2 will again collect a PLATE 1 PLATE 2 charge. + BATTERY – Now let’s connect our simple capacitor to a source of AC current and in series with the windings of an electric motor. Since AC current alternates, first one PLATE 1 PLATE 2 MOTOR plate, then the other would be charged and discharged in turn. First plate 1 is charged, then as the current reverses, a rush of electrons flow from plate 1 to plate 2 through the motor windings. -

Using Rctime to Measure Resistance

Basic Express Application Note Using RCtime to Measure Resistance Introduction One common use for I/O pins is to measure the analog value of a variable resistance. Although a built-in ADC (Analog to Digital Converter) is perhaps the easiest way to do this, it is also possible to use a digital I/O pin. This can be useful in cases where you don't have enough ADC channels, or if a particular processor doesn't have ADC capability. Procedure RCtime BasicX provides a special procedure called RCtime for this purpose. RCtime measures the time it takes for a pin to change state to a defined value. By connecting a fixed capacitor and a variable resistor in an RC circuit, you can use an I/O pin to measure the value of the variable resistor, which might be a device such as a potentiometer or thermistor. There are two common ways to wire an RCtime system. The first is to tie the variable resistor to ground. Figure 1 shows this configuration. The advantage here is less chance of damage from static electricity: Figure 1 Figure 2 The second configuration is shown in Figure 2. Here we use the opposite connection, where the capacitor C is tied to ground and the variable resistor RV is tied to 5 volts: In both circuits resistor R1 is there to protect the BasicX chip's output driver from driving too much current when charging the capacitor. To take a sample, the capacitor is first discharged by taking the pin to the correct state. In the case of Figure 1, the pin needs to be taken high (+5 V) to produce essentially 0 volts across the capacitor, which causes it to discharge. -

Memristor-The Future of Artificial Intelligence L.Kavinmathi, C.Gayathri, K.Kumutha Priya

International Journal of Scientific & Engineering Research, Volume 5, Issue 4, April-2014 358 ISSN 2229-5518 Memristor-The Future of Artificial Intelligence L.kavinmathi, C.Gayathri, K.Kumutha priya Abstract- Due to increasing demand on miniaturization and low power consumption, Memristor came into existence. Our design exploration is Reconfigurable Threshold Logic Gates based Programmable Analog Circuits using Memristor. Thus a variety of linearly separable and non- linearly separable logic functions such as AND, OR, NAND, NOR, XOR, XNOR have been realized using Threshold logic gate using Memristor. The functionality can be changed between these operations just by varying the resistance of the Memristor. Based on this Reconfigurable TLG, various Programmable Analog circuits can be built using Memristor. As an example of our approach, we have built Programmable analog Gain amplifier demonstrating Memristor-based programming of Threshold, Gain and Frequency. As our idea consisting of Programmable circuit design, in which low voltages are applied to Memristor during their operation as analog circuit element and high voltages are used to program the Memristor’s states. In these circuits the role of memristor is played by Memristor Emulator developed by us using FPGA. Reconfigurable is the option we are providing with the present system, so that the resistance ranges are varied by preprogram too. Index Terms— Memristor, TLG-threshold logic gates, Programmable Analog Circuits, FPGA-field programmable gate array, MTL- memristor threshold logic, CTL-capacitor Threshold logic, LUT- look up table. —————————— ( —————————— 1 INTRODUCTION CCORDING to Chua’s [founder of Memristor] definition, 9444163588. E-mail: [email protected] the internal state of an ideal Memristor depends on the • L.kavinmathi is currently pursuing bachelors degree program in electronics A and communication engineering in tagore engineering college under Anna integral of the voltage or current over time. -

Lab 1: the Bipolar Junction Transistor (BJT): DC Characterization

Lab 1: The Bipolar Junction Transistor (BJT): DC Characterization Electronics II Contents Introduction 2 Day 1: BJT DC Characterization 2 Background . 2 BJT Operation Regions . 2 (i) Saturation Region . 4 (ii) Active Region . 4 (iii) Cutoff Region . 5 Part 1: Diode-Like Behavior of BJT Junctions, and BJT Type 6 Experiment . 6 Creating Your Own File . 6 Report..................................................... 8 Part 2: BJT IC vs. VCE Characteristic Curves - Point by Point Plotting 8 Prelab . 8 Experiment . 8 Creating Your Own File . 8 Parameter Sweep . 9 Report..................................................... 10 Part 3: The Current Mirror 11 Experiment . 12 Simulation . 12 Checkout . 12 Report..................................................... 13 1 ELEC 3509 Electronics II Lab 1 Introduction When designing a circuit, it is important to know the properties of the devices that you will be using. This lab will look at obtaining important device parameters from a BJT. Although many of these can be obtained from the data sheet, data sheets may not always include the information we want. Even if they do, it is also useful to perform our own tests and compare the results. This process is called device characterization. In addition, the tests you will be performing will help you get some experience working with your tools so you don't waste time fumbling around with them in future labs. In Day 1, you will be looking at the DC characteristics of your transistor. This will give you an idea of what the I-V curves look like, and how you would measure them. You will also have to build and test a current mirror, which should give you an idea of how they work and where their limitations are. -

VOLTAGE REGULATORS 1. Zener Controlled Transistor Voltage Regulator

VOLTAGE REGULATORS A voltage regulator is a voltage stabilizer that is designed to automatically stabilize a constant voltage level. A voltage regulator circuit is also used to change or stabilize the voltage level according to the necessity of the circuit. Thus, a voltage regulator is used for two reasons:- 1. To regulate or vary the output voltage of the circuit. 2. To keep the output voltage constant at the desired value in-spite of variations in the supply voltage or in the load current. To know more on the basics of this subject, you may also refer Regulated Power Supply. Voltage regulators find their applications in computers, alternators, power generator plants where the circuit is used to control the output of the plant. Voltage regulators may be classified as electromechanical or electronic. It can also be classified as AC regulators or DC regulators. We have already explained about IC Voltage Regulators. Electronic Voltage Regulator All electronic voltage regulators will have a stable voltage reference source which is provided by the reverse breakdown voltage operating diode called zener diode. The main reason to use a voltage regulator is to maintain a constant dc output voltage. It also blocks the ac ripple voltage that cannot be blocked by the filter. A good voltage regulator may also include additional circuits for protection like short circuits, current limiting circuit, thermal shutdown, and over voltage protection. Electronic voltage regulators are designed by any of the three or a combination of any of the three regulators given below. 1. Zener Controlled Transistor Voltage Regulator A zener controlled voltage regulator is used when the efficiency of a regulated power supply becomes very low due to high current. -

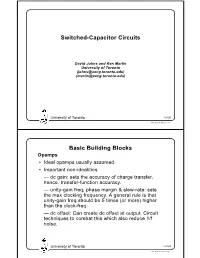

Switched-Capacitor Circuits

Switched-Capacitor Circuits David Johns and Ken Martin University of Toronto ([email protected]) ([email protected]) University of Toronto 1 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Opamps • Ideal opamps usually assumed. • Important non-idealities — dc gain: sets the accuracy of charge transfer, hence, transfer-function accuracy. — unity-gain freq, phase margin & slew-rate: sets the max clocking frequency. A general rule is that unity-gain freq should be 5 times (or more) higher than the clock-freq. — dc offset: Can create dc offset at output. Circuit techniques to combat this which also reduce 1/f noise. University of Toronto 2 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Double-Poly Capacitors metal C1 metal poly1 Cp1 thin oxide bottom plate C1 poly2 Cp2 thick oxide C p1 Cp2 (substrate - ac ground) cross-section view equivalent circuit • Substantial parasitics with large bottom plate capacitance (20 percent of C1) • Also, metal-metal capacitors are used but have even larger parasitic capacitances. University of Toronto 3 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Switches I I Symbol n-channel v1 v2 v1 v2 I transmission I I gate v1 v p-channel v 2 1 v2 I • Mosfet switches are good switches. — off-resistance near G: range — on-resistance in 100: to 5k: range (depends on transistor sizing) • However, have non-linear parasitic capacitances. University of Toronto 4 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Non-Overlapping Clocks I1 T Von I I1 Voff n – 2 n – 1 n n + 1 tTe delay 1 I fs { --- delay V 2 T on I Voff 2 n – 32e n – 12e n + 12e tTe • Non-overlapping clocks — both clocks are never on at same time • Needed to ensure charge is not inadvertently lost. -

Kirchhoff's Laws in Dynamic Circuits

Kirchhoff’s Laws in Dynamic Circuits Dynamic circuits are circuits that contain capacitors and inductors. Later we will learn to analyze some dynamic circuits by writing and solving differential equations. In these notes, we consider some simpler examples that can be solved using only Kirchhoff’s laws and the element equations of the capacitor and the inductor. Example 1: Consider this circuit Additionally, we are given the following representations of the voltage source voltage and one of the resistor voltages: ⎧⎧10 V fortt<< 0 2 V for 0 vvs ==⎨⎨and 1 −5t ⎩⎩20 V forte>+ 0 8 4 V fort> 0 We wish to express the capacitor current, i 2 , as a function of time, t. Plan: First, apply Kirchhoff’s voltage law (KVL) to the loop consisting of the source, resistor R1 and the capacitor to determine the capacitor voltage, v 2 , as a function of time, t. Next, use the element equation of the capacitor to determine the capacitor current as a function of time, t. Solution: Apply Kirchhoff’s voltage law (KVL) to the loop consisting of the source, resistor R1 and the capacitor to write ⎧ 8 V fort < 0 vvv12+−=ss0 ⇒ v2 =−= vv 1⎨ −5t ⎩16− 8et V for> 0 Use the element equation of the capacitor to write ⎧ 0 A fort < 0 dv22 dv ⎪ ⎧ 0 A fort < 0 iC2 ==0.025 =⎨⎨d −5t =−5t dt dt ⎪0.025() 16−> 8et for 0 ⎩1et A for> 0 ⎩ dt 1 Example 2: Consider this circuit where the resistor currents are given by ⎧⎧0.8 A fortt<< 0 0 A for 0 ii13==⎨⎨−−22ttand ⎩⎩0.8et−> 0.8 A for 0 −0.8 e A fort> 0 Express the inductor voltage, v 2 , as a function of time, t. -

Analysis Guide for Electronics/Electrical Product Designers

WHITE PAPER Analysis Guide for Electronics/Electrical Product Designers inspiration SUMMARY In this paper we outline the key design performance issues facing electronics and electrical product manufacturers and identify the ben- efits of using SolidWorks® Simulation software for electronics and electrical product design. The paper outlines the types of analyses that SolidWorks Simulation software can perform and proves why these analyses are critical to electrical and electronic product engineering. Introduction Analysis and simulation software has become an indispensable tool for the development, certification, and success of electronics and electrical products. In addition to having to meet federal requirements, such as standards regulating electromagnetic compatibility (EMC) and product safety, electronics and electri- cal products manufacturers must meet various industry standards, such as the Bellcore standard for telecommunications equipment and standards governing the reliability of printed circuit boards (e.g., all PCBs must be able to withstand 21 pounds of load in the center). Combined with customer and market demand for smaller, more compact, and lighter products, these requirements create competitive pressures that make flawless, reliable development of electronics and electrical products an absolute necessity. FIGURE 1: THE USE OF CFD MAKES IT POSSIBLE TO ELIMINATE EXPENSIVE PHYS- IcaL PROTOTYpeS, AND FIND SERIOUS FLAWS MUCH eaRLIER IN THE deSIGN PROCESS. Today’s electronics/electrical product manufacturers use analysis software to simulate and assess the performance of a variety of product designs, including consumer electronics, appliances, sophisticated instrumentation, electronics components, printed circuit boards, RF equipment, motors, drives, electrical con- trols, micro electromechanical systems (MEMS), optical networking equipment, electronics packaging, and semiconductors. Analysis software enables engi- neers to simulate design performance and identify and address potential design problems before prototyping and production. -

What Is an SMPS and How Does It Generate Harmonics?

MIRUS FREQUENTLY ASKED QUESTIONS FAQ’s___ International Inc. 6805 Invader Cres., Unit #12, Mississauga, Ontario, Canada L5T 2K6 Harmonic Mitigating Transformers <Back to Questions> 4. What is an SMPS and how does it generate harmonics? The Switch-mode Power Supply (SMPS) is found in most power electronics today. Its reduced size and weight, better energy efficiency and lower cost make it far superior to the power supply technology it replaced. Electronic devices need power supplies to convert the 120VAC receptacle voltage to the low voltage DC levels Rectifier Lls that they require. Older generation power supplies used Bridge large and heavy 60 Hz step-down transformers to i convert the AC input voltage to lower values before ac Smoothing Switch-mode rectification. The SMPS avoids the heavy 60 Hz step- vac Capacitor dc-to-dc Cf converter down transformer by directly rectifying the 120VAC Load using an input diode bridge (Figure 4-1). The rectified voltage is then converted to lower voltages by much smaller and lighter switch-mode dc-to-dc converters using tiny transformers that operate at very high Figure 4-1: Typical circuit diagram of Switch-mode Power frequency. Consequently the SMPS is very small and Supply light. The SMPS is not without its downside, however. The operation of the diode bridge and accompanying smoothing capacitor is very non-linear in nature. That is, it draws current in non-sinusoidal pulses at the peak of the voltage Voltage waveform (see Figure 4-2). This non-sinusoidal current waveform is very rich in harmonic currents. Because the SMPS has become the standard computer power supply, they are found in large quantities in commercial buildings. -

EE 462: Laboratory # 4 DC Power Supply Circuits Using Diodes (Lab 3 Report Due at Beginning of the Period) (Pre-Lab4 and Lab-4 D

EE 462: Laboratory # 4 DC Power Supply Circuits Using Diodes by Drs. A.V. Radun and K.D. Donohue (2/14/07) Department of Electrical and Computer Engineering University of Kentucky Lexington, KY 40506 Updated by Stephen Maloney (2/12/08) (Lab 3 report due at beginning of the period) (Pre-lab4 and Lab-4 Datasheet due at the end of the period) I. Instructional Objectives Design and construct circuits that transform sinusoidal (AC) voltages into constant (DC) voltages. Design and construct a voltage regulator based on the characteristics of the Zener diode. Evaluate the performance of simple rectifier and regulator circuits. See Horenstein 4.3 and 4.4 II. Background Electric power transmits best over long distances at high voltages. Since P = I V, a larger voltage implies a smaller current for the same transmitted power. And smaller currents allow for the use of smaller wires with less loss. The high voltages used for power transmission must be reduced to be compatible with the needs of most consumer and industrial equipment. This is done with transformers that only operate with AC (DC does not pass through a transformer). However, most electronic devices powered by a home outlet require DC (constant) voltages. Therefore, the device must have a power supply that converts AC voltages into a DC (constant) voltage. The terminology "DC" is somewhat ambiguous. DC can mean the voltage or current always has the same polarity but changes with time (pulsating DC), or it can mean a constant value. In this lab assignment DC will refer to a constant voltage or current. -

Advantages of Using PMOS-Type Low-Dropout Linear Regulators in Battery Applications by Brian M

Power Management Texas Instruments Incorporated Advantages of using PMOS-type low-dropout linear regulators in battery applications By Brian M. King Applications Specialist Introduction Figure 1. Components of a typical The proliferation of battery-powered equipment has linear regulator increased the demand for low-dropout linear regulators (LDOs). LDOs are advantageous in these applications because they offer inexpensive, reliable solutions and require few components or little board area. The circuit model for a typical LDO consists of a pass element, sam- Pass pling network, voltage reference, error amplifier, and Element externally connected capacitors at the input and output of the device. Figure 1 shows the circuit blocks of a typical + Reference + + – Error linear regulator. The pass element is arguably the most Amplifier important part of the LDO in battery applications. The Sampling V V technology used for the pass element can increase the IN Network OUT useful life of the battery. The pass element can be either a bipolar transistor or a – – MOSFET. The general difference between these is how the pass element is driven. A bipolar pass element is a current-driven device, whereas the MOSFET is a voltage- driven device. In addition, the pass element can be either an N-type (NPN or NMOS) or a P-type (PNP or PMOS) device. N-type devices require a positive drive signal with respect to the output, while P-type devices are driven from a negative signal with respect to the input. Generating a positive drive signal becomes difficult at low input voltages. PMOS pass elements much more attractive than PNP pass As a result, LDOs that operate from low input voltages elements.