Imperial College London

Department of Physics

Graphene Field Effect Transistors

By Mohamed Warda and Khodr Badih

20 July 2021

Abstract

The past decade has seen rapid growth in the research area of graphene and its application to novel electronics. With Moore’s law beginning to plateau, the need for post-silicon technology in industry is becoming more apparent. Moreover, existing technologies are insufficient for implementing terahertz detectors and receivers, which are required for a number of applications including medical imaging and security scanning. Graphene is considered to be a key potential candidate for replacing silicon in existing CMOS technology as well as realizing field effect transistors for terahertz detection, due to its remarkable electronic properties, with observed electronic mobilities reaching up to 2 × 105 cm2 V−1 s−1 in suspended graphene samples. This report reviews the physics and electronic properties of graphene in the context of graphene transistor implementations. Common techniques used to synthesize graphene, such as mechanical exfoliation, chemical vapor deposition, and epitaxial growth are reviewed and compared. One of the challenges associated with realizing graphene transistors is that graphene is semimetallic, with a zero bandgap, which is troublesome in the context of digital electronics applications. Thus, the report also reviews different ways of opening a bandgap in graphene by using bilayer graphene and graphene nanoribbons. The basic operation of a conventional field effect transistor is explained and key figures of merit used in the literature are extracted. Finally, a review of some examples of state-of-the-art graphene field effect transistors is presented, with particular focus on monolayer graphene, bilayer graphene, and graphene nanoribbons.

Contents

- Acronyms and Constants

- i

- 1 Introduction

- 1

13

1.1 Motivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.2 Layout of Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

- 2 Graphene

- 5

- 6

- 2.1 Crystallography and Band Structure . . . . . . . . . . . . . . . . . . . .

2.2 Physical Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3 Synthesis Techniques . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.4 Related Structures and Bandgap Engineering . . . . . . . . . . . . . . . .

2.4.1 Bilayer Graphene . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.4.2 Graphene Nanoribbons . . . . . . . . . . . . . . . . . . . . . . . .

14 17 20 21 23

- 3 Conventional CMOS Technology

- 27

- 4 State-of-the-Art Graphene FETs

- 32

33 35 36

4.1 Monolayer Graphene FETs . . . . . . . . . . . . . . . . . . . . . . . . . . 4.2 Bilayer Graphene FETs . . . . . . . . . . . . . . . . . . . . . . . . . . . 4.3 Graphene Nanoribbon FETs . . . . . . . . . . . . . . . . . . . . . . . . .

- 5 Conclusion and Future Perspectives

- 38

40 46

References Appendix

Acronyms and Constants Acronyms

CMOS Complementary metal oxide semiconductor CNT CVD

Carbon nanotube Chemical vapor deposition

HEMT High electron mobility transistor FET GNR RF

Field effect transistor Graphene nanoribbon Radio Frequency

- STM

- Scanning tunneling microscopy

i

Constants

√

i

The imaginary unit, −1

ce

The speed of light in vacuum, 3.00 × 10−8 m s−1 The elementary charge, 1.60 × 10−19 C h The Planck constant, 6.63 × 10−34 Js ~ The reduced Planck constant,

h2π

ii

1 INTRODUCTION

1 Introduction

1.1 Motivation

Graphene is a two dimensional sheet of carbon atoms arranged in a honeycomb lattice. Since its discovery in 2004 by Geim and Novoselov, for which they shared the Nobel prize in 2010 [23], graphene has captured the interests of scientists and engineers alike. Due to its two-dimensional nature, graphene possesses a myriad of novel electronic, mechanical, thermal, and optical properties that make it a potential candidate for several applications including flexible electronics, touch screens, biological and chemical sensing, drug delivery, and transistors [22, 64, 45, 62, 16]. Indeed, the application of graphene to electronics is now a burgeoning research area, and has come along way since its genesis in 2004.

The transistor is a key building block of virtually all modern electronic devices. The first transistor was invented in 1947 by Shockley, Bardeen, and Brattain at Bell Labs, and represented a revolutionary advancement in the development of electronic devices in the latter half of the 20th century. Different types of transistors, including bipolar junction transistors (BJTs) and field effect transistors (FETs) were invented in the 20th century – but the most commonly used transistor in modern electronics is the metal oxide semiconductor field effect transistor (MOSFET), which was invented by Atalla and Kahng in 1959 at Bell Labs. Complementary metal oxide semiconductor (CMOS) technology uses MOSFETs made primarily of silicon, and is the most widely used technology for realizing electronics today [53, 55].

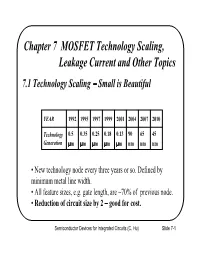

Since its inception, physicists and engineers have downscaled the size of the MOSFET transistor while maintaining its performance, which has been the driving force behind the incredible speed at which technology has progressed over the past few decades. In more concrete terms, this is described by Moore’s law. Moore’s law is the observation that the number of transistors on an integrated circuit (and, in turn, computer processing power) doubles every two years at the same cost as a result of downscaling the size of the MOSFET transistor [41, 24, 42]. Figure 1 depicts the number of transistors on computer chips as a function of time, from 1965 to 2015, which can be seen to roughly vary according to Moore’s law. As of 2019, the number of transistors on commercially available microprocessors can reach up to 39.54 billion [1], and Samsung and TSMC have been fabricating 10 nm and 7 nm MOSFETs [2, 3].

1

1 INTRODUCTION

Figure 1: A graphical illustration of Moore’s law from 1965 to 2015. The vertical axis, showing the transistor count, is logarithmic. It is evident that, to a good approximation, the number of transistors on a computer chip has doubled every two years, for the past five decades [24].

Recently, however, it has been observed that Moore’s law is beginning to reach a plateau, as the miniaturization of transistors continues, and is predicted to end around 2025 [4]. Moreover, the International Technology Roadmap for Semiconductors predicts that after the year 2021, downscaling transistors will no longer be economically viable [5]. This is primarily because at small scales, undesirable short-channel effects such as drain induced barrier lowering, velocity saturization, impact ionization, and other quantum mechanical phenomena begin to manifest, degrading MOSFET performance [31]. As such, physicists and engineers are considering alternative avenues and technologies for extending Moore’s law in a post-silicon world. Among the chief novel materials that provide a way of achieving this goal is graphene [22].

The remarkable electronic properties exhibited by graphene, including its extraordi-

2

1 INTRODUCTION narily high mobility and its ambipolar field effect behavior, make it a promising candidate for carrying electric current in FETs and could in principle outperform existing siliconbased technologies [64, 22]. Since 2007, efforts have been made toward incorporating graphene into existing MOSFET technology [6]. These graphene-based FETs have a number of important potential engineering applications, including sensors [16, 19] and high frequency terahertz detectors [29]. The latter is of particular importance in engineering due to the so-called “terahertz gap” – a region in the electromagnetic spectrum extending roughly from 0.1 THz to 10 THz for which existing generation/detection technologies are inadequate. Terahertz technology has a number of potential applications including medical imaging, security scanning, and as a tool in molecular biology research [29, 17, 59, 62]. However, there exist economic and physical challenges and bottlenecks associated with realizing graphene FETs that are suitable for the aforementioned applications. This report provides a review of the physics of graphene and its electronic properties as relevant in the context of field effect transistors as well as a state-of-the-art review of different graphene FET implementations.

1.2 Layout of Report

The remainder of this report is split up into four main sections. In section 2, a brief historical overview of graphene is presented, followed by a review of the physics of graphene with particular emphasis on its crystallography and electronic band structure. Relevant electronic properties, such as the high mobility of graphene and its ambipolar field effect behavior, are described. Different methods of synthesizing graphene are presented and compared in terms of their scalability, cost, and the quality of graphene production. Finally, the topic of bandgap engineering in graphene is discussed, using bilayer graphene and graphene nanoribbons as examples.

In section 3, the principle of operation of the conventional MOSFET transistor is discussed, and an overview of basic MOSFET device physics is presented. The MOSFET transistor is modelled as a three terminal device, and relevant current-voltage characteristics are highlighted. Key figures of merit that are commonly found in the literature are extracted from the model, and are used in section 4 to compare different graphene FET implementations.

In section 4, a state-of-the-art review of graphene FETs is presented, with particular

3

1 INTRODUCTION focus on monolayer graphene FETs, bilayer graphene FETs, and graphene nanoribbon FETs. Different implementations in the literature are compared using the figures of merit presented in section 3, and the challenges associated with improving the performance of graphene FETs are identified and discussed.

Finally, in section 5, the key ideas pertaining to the state-of-the-art graphene FETs presented in section 4 are summarized, and an assessment of the current state of graphene FET research within the wider context of modern industrial applications is presented.

4

2 GRAPHENE

2 Graphene

Graphene is a single atom-thick planar allotrope of carbon. It is closely related to graphite, which is another allotrope of carbon [7, 22]. The structure of three dimensional graphite, which may be thought of as a layered stack of graphene sheets held together by van der Waals forces, was determined and studied in 1916 through the use of powder diffraction [27]. The difference in the structure of two dimensional graphene and three dimensional graphite is shown in Fig. 2

Figure 2: A diagram illustrating the difference between graphite (a) and graphene (b). Graphite is made of several layers of graphene sheet stacked on top of one another and held together via weak van der Waals forces [50].

The theory of monolayer graphite, or graphene, was not developed until 1947 when

Wallace studied the electronic band structure of graphene in order to gain some understanding of the electronic properties of three dimensional graphite by extrapolating the electronic properties of graphene [60]. Despite efforts to study the physics of graphene, physicists had long ruled out its existence as a two dimensional crystal in a free state due to the Mermin-–Wagner theorem and the Landau–Peierls arguments concerning thermal fluctations at nonzero temperatures which lead to thermodynamically unstable two dimensional crystals [7, 64].

In 2004, at the University of Manchester, Geim and Novoselov demonstrated the first experimental evidence of the existence of graphene by exfoliating crystalline graphite using scotch tape and transferring the graphene layers onto a thin silicon dioxide over silicon [43, 23]– a technique now referred to as mechanical exfoliation. Soon after, the anomalous quantum Hall effect was observed in graphene and reported by Geim and Novoselov as well as Kim and Zhang at Columbia University [44, 46]. The observation of the anomalous quantum Hall effect provided experimental evidence for the interesting

5

2 GRAPHENE relativistic behavior of electrons in graphene – in particular, it was shown that electrons in graphene may be viewed as massless charged fermions [44]. As shall be explained in this section, the relativistic behavior of electrons in graphene gives rise to its extraordinary electronic properties.

2.1 Crystallography and Band Structure

Graphene has a honeycomb lattice of carbon atoms separated by an interatomic distance

ꢀ

a ≈ 1.42 A [7]. Figure 3 shows a scanning tunnelling microscopy (STM) image of graphene that depicts its honeycomb network of carbon atoms. Figure 4 shows a sketch of the honeycomb lattice of graphene and highlights the different environments of neighboring carbon atoms in its lattice.

Figure 3: An STM image of graphene on the substrate Ir(111) that shows its honeycomb structure [25].

6

2 GRAPHENE

Figure 4: (a) The honeycomb lattice, with the primitive lattice vectors a1 and a2 that span the lattice in real space. Different carbon atoms corresponding to filled and unfilled circles are not equivalent in crystallographic terms, so the honeycomb lattice is not a Bravais lattice. (b) Shows how this problem can be overcome by defining the shaded region to be a unit cell containing two distinguishable carbon atoms. The two atoms may be thought of as atoms from two different interpenetrating sublattices, labelled A and B [7].

As shown in Fig. 4, different atoms in the lattice are not equivalent, making the honeycomb lattice a non-Bravais lattice. These two inequivalent sublattices, labelled A and B, may be thought of as interpentrating sublattices that form a triangular Bravais lattice with two atoms per unit cell and two primitive lattice vectors a1 and a2 [7]. With reference to the coordinate system defined by the right-handed orthonormal set of vectors (ˆe1, ˆe2, ˆe3) is such that ˆe1 and ˆe2 lie in the plane of graphene, with ˆe3 pointing in a direction perpendicular to the plane. The primitive lattice vectors are given by

√

a0

(ˆe1 − 3ˆe2) = (ˆe1 − 3ˆe2)

- √

- √

3a

a1 =

(1)

- 2

- 2

and

√

a0

(ˆe1 + 3ˆe2) = (ˆe1 + 3ˆe2),

- √

- √

3a

a2 =

(2)

- 2

- 2

√

where ka1,2k = a0 = 3a ≈ 2.46 A is the lattice constant. The primitive reciprocal lattice

ꢀ

vectors, b1 and b2, are related to a1 and a2 [55] by

- ꢀ

- ꢁ

a2 × ˆe3

2π

a0

ˆe2

√

- b1 = 2π

- =

ˆe1 −

(3)

a1 · (a2 × ˆe3)

3

7

2 GRAPHENE and

- ꢀ

- ꢁ

ˆe3 × a1

2π

a0

ˆe2

√

- b2 = 2π

- =

ˆe1 +

.

(4)

a1 · (a2 × ˆe3)

3

Figure 5: The reciprocal lattice of graphene (in k space). The shaded region is the first Brillouin zone, which is a Wigner–Seitz cell of the reciprocal lattice. By convention, Γ denotes the point k = 0. The points M and M0, as well as K and K0, are inequivalent.

Equivalent points are separated in k space by b1 and b2. The corners of the first

Brillouin zone, namely, the six points labelled K and K0, are collectively referred to as

Dirac points [7].

Figure 5 shows the first Brillouin zone for graphene in reciprocal space. The center of the first Brillioin zone is labelled as Γ by convention and corresponds to the origin k = 0, where k = (kx, ky) is the wave vector associated with electronic states in the lattice, with kx and ky representing the wavenumbers along ˆe1 and ˆe2, respectively. The first Brillouin zone is hexagonal and has six points labelled K and K0, collectively referred to as Dirac points. Points with the same label are considered to be equivalent and are separated by a primitive reciprocal lattice vector (b1 or b2). The novel electronic properties of graphene hinge on the excitations around these six Dirac points, as shall be explained in this section. It is worth however, showing first the full band structure of graphene computed from first principle calculations. We use VASP to find the full band structure of Graphene. The results are presented in the graph below, The interesting feature of the above band structure as we shall see below is the crossing at

8

2 GRAPHENE

Figure 6: Full Band structure of Graphene calculated using ab initio methods. Here we use VASP to find the Band structure.

point K. This crossing is responsible for many of the interesting properties of graphene. Although the ab initio method susccsfully provides the full band structure with great detail, to understand the physics governing graphene, it is useful to zoom in at point K and describe the dispersion using a simplified version. An isolated carbon atom in an excited state has four electrons in its outer shell. Using spectroscopic notation, this corresponds to one 2s electron and one electron per 2p orbital (2px, 2py, and 2pz). In graphene, the 2s, 2px, and 2py states mix to form three sp2 hybrid orbitals for each carbon atom separated by 120◦. The electronic sp2 hybrid states participate in three strong covalent σ bonds between each carbon atoms and neighboring carbon atoms in the graphene lattice, leading to the geometry of the lattice shown in Fig. 4. Electrons in 2pz orbitals are located above and below the plane of graphene, participating in weaker π bonds [28]. These electrons will henceforth be referred to as π electrons. This is illustrated in Fig. 6.

9

2 GRAPHENE

Figure 7: A sketch illustrating the different carbon-carbon bonds present in graphene. The electronic states that give rise to the electronic properties of graphene those in the

2pz orbital lobes, labelled π on the diagram [28].

The sp2 electrons participating in strong σ bonds lead to the high strength and other novel mechanical properties of graphene but play no role in the low energy excitations which govern the electronic properties thereof that are relevant in the context of graphene electronics [22]. On the other hand, the π electrons are highly mobile and play a crucial role in the context of the electronic properties of graphene. For this reason, the band structure of graphene as presented and analyzed in the literature only takes into account π electrons, which will be assumed in the remainder of this report.

By applying the tight binding model [7], it can be shown (derived in the appendix) that the analytical expression for the energy dispersion relation of π electrons is

ꢀ0 ± t f(k)

ꢀ

(±)(k) =

,

(5)

1 ± s f(k)

where ꢀ = ꢀ(±)(k) is the energy, ꢀ0 is a parameter that sets the zero of the dispersion relation, t is a tight binding hopping parameter, s is an overlap parameter, + and − denote the valence and conduction bands respectively, and f is a function defined by

vuu

- !

- !