(PPS) • CMOS Photodiode Active Pixel Sensor (APS) • Photoga

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Photodiode and LIGHT EMITTING DIODE

Photodiode and LIGHT EMITTING DIODE Presentation by JASWANT KUMAR ROLL NO.-12 rd IT(3 SEM.) 1 About LEDs (1/2) • A light emitting diode (LED) is essentially a PN junction opto- semiconductor that emits a monochromatic (single color) light when operated in a forward biased direction. • LEDs convert electrical energy into light energy. LED SYMBOL 2 ABOUT LEDS (2/2) • The most important part of a light emitting diode (LED) is the semi-conductor chip located in the center of the bulb as shown at the right. • The chip has two regions separated by a junction. • The junction acts as a barrier to the flow of electrons between the p and the n regions. 3 LED CIRCUIT • In electronics, the basic LED circuit is an electric power circuit used to power a light-emitting diode or LED. The simplest such circuit consists of a voltage source and two components connect in series: a current-limiting resistor (sometimes called the ballast resistor), and an LED. Optionally, a switch may be introduced to open and close the circuit. The switch may be replaced with another component or circuit to form a continuity tester. 4 HOW DOES A LED WORK? • Each time an electron recombines with a positive charge, electric potential energy is converted into electromagnetic energy. • For each recombination of a negative and a positive charge, a quantum of electromagnetic energy is emitted in the form of a photon of light with a frequency characteristic of the semi- conductor material. 5 Mechanism behind photon emission in LEDs? MechanismMechanism isis “injection“injection Electroluminescence”.Electroluminescence”. -

Integrated High-Speed, High-Sensitivity Photodiodes and Optoelectronic Integrated Circuits

Sensors and Materials, Vol. 13, No. 4 (2001) 189-206 MYUTokyo S &M0442 Integrated High-Speed, High-Sensitivity Photodiodes and Optoelectronic Integrated Circuits Horst Zimmermann Institut fiirElektrische Mess- und Schaltungstechnik, Technische Universitat Wien, Gusshausstrasse, A-1040 Wien, Austria (Received February 28, 2000; accepted February3, 2001) Key words: integrated circuits, integrated optoelectronics, optical receivers, optoelectronic de vices, PIN photodiode, double photodiode, silicon A review of the properties of photodiodes available through the use of standard silicon technologies is presented and some examples of how to improve monolithically integrated photodiodes are shown. The application of these photodiodes in optoelectronic integrated circuits (OEICs) is described. An innovative double photodiode requiring no process modificationsin complementary metal-oxide sem!conductor (CMOS) and bipolar CMOS (BiCMOS) technologies achieves a bandwidth in excess of 360 MHzand data rates exceeding 622 Mb/s. Furthermore, a new PIN photodiode requiring only one additional mask for the integration in a CMOS process is capable of handling a data rate of 1.1 Gb/s. Antireflection coating improves the quantum efficiencyof integrated photodiodes to values of more than 90%. Integrated optical receivers for data communication achieve a high bandwidth and a high sensitivity. Furthermore, an OEIC for application in optical storage systems is introduced. Author's e-mail address: [email protected] 189 l 90 Sensors and Materials, Vol. 13, No. 4 (2001) 1. Introduction Photons with an energy larger than the band gap generate electron-hole pairs in semiconductors. This photogeneration G obeys an exponential law: aP,0 G( x) = -- exp( -ax), Ahv (1) where xis the penetration depth coordinate, P0 is the nonreflectedportion of the incident optical power, A is the light-sensitive area of a photodiode, hv is the energy of the photon, and a is the wavelength-dependent absorption coefficient. -

The Effective Application of Digital Printing Techniques for Fine Artists in the South African Context

The effective application of digital printing techniques for fine artists in the South African context. a Dissertation BY Susan Louise Giloi (NH Dip: Photography) Submitted in partial compliance with the requirements for the Degree Magister Technologiae in Photography in the Department of Photography, Faculty of Art and Design. PORT ELIZABETH TECHNIKON November 1999 PROMOTERS Prof. N.P.L. Allen M.F.A. D.Phil. Laur Tech Mr S.C. Strooh N Dip: Photography DEDICATION To my family who gave me the opportunity to do this. To Prof. Nicholas Allen and Mr. Steven Strooh for their help and inspiration. ii ACKNOWLEDGEMENTS My thanks to all the individuals and companies that helped me. Ashley Bowers, Tone Graphics Billy Whitehair, Printing Products Bonny Lhotka Bruce Cadle, Port Elizabeth Technikon Carol Van Zyl, Vaal Triangle Technikon Cleone Cull, Port Elizabeth Technikon Colleen Bate, Digital Imaging and Publishing Dean Johnstone, Square One Dianna Wall, Museum Africa Dorothy Krause Edwin Taylor, Beith Digital Eileen Fritsch, Big Picture Magazine Ethna Frankenfeld, Port Elizabeth Technikon Eugene Pienaar, Port Elizabeth Technikon Gavin Van Rensburg, Kemtek Geoff Black, Cyber Distributors Glen Meyer, Port Elizabeth Technikon Hank Van Der Water, Xerox E.C. Ian de Vega, Port Elizabeth Technikon Ian Marley, Vaal Triangle Technikon Ian White, John Cook University Inge Economou, Port Elizabeth Technikon Isabel Lubbe, Vaal Triangle Technikon Isabel Smit, Yeltech Jenny Ord, Port Elizabeth Technikon John Clarke, JFC Clarke Studio John Otsuki, Capitol Color Keith Solomon, First Graphics Laraine Bekker, Port Elizabteh Technikon Lisle Nel, Port Elizabeth Technikon Magda Bosch, Port Elizabteh Technikon Mary Duker, Port Elizabeth Technikon Mike Swanepoel, Port Elizabeth Technikon Nick Hand, Nexus Nolan Weight, Stonehouse Graphics Peter Thome, Agfa SA Robin Mowatt, QMS Ronald Henry, Omni Graphics Ros Streak, City Graphics Russell Williams, Teltron Steve Majewski Thinus Mathee, Vaal Triangle Technikon iii Tilla Jordaan, Xerox SA Tony Davidson, Outdoor Advertising Association of S.A. -

Leds As Single-Photon Avalanche Photodiodes by Jonathan Newport, American University

LEDs as Single-Photon Avalanche Photodiodes by Jonathan Newport, American University Lab Objectives: Use a photon detector to illustrate properties of random counting experiments. Use limiting probability distributions to perform statistical analysis on a physical system. Plot histograms. Condition a detector’s signal for further electronic processing. Use a breadboard, power supply and oscilloscope to construct a circuit and make measurements. Learn about semiconductor device physics. Reading: Taylor 3.2 – The Square-Root Rule for a Counting Experiment pp. 48-49 Taylor 5.1-5.3 – Histograms and the Normal Distribution pp. 121-135 Taylor Ch. 11 – The Poisson Distribution pp. 245-254 Taylor Problem 5.6 – The Exponential Distribution p. 155 Experiment #1: Lighting an LED A Light-Emitting Diode is a non-linear circuit element that can produce a controlled amount of light. The AND113R datasheet shows that the luminous intensity is proportional to the current flowing through the LED. As illustrated in the IV curve shown below, the current flowing through the diode is in turn proportional to the voltage across the diode. Diodes behave like a one-way valve for current. When the voltage on the Anode is more positive than the voltage on the Cathode, then the diode is said to be in Forward Bias. As the voltage across the diode increases, the current through the diode increases dramatically. The heat generated by this current can easily destroy the device. It is therefore wise to install a current-limiting resistor in series with the diode to prevent thermal runaway. When the voltage on the Cathode is more positive than the voltage on the Anode, the diode is said to be in Reverse Bias. -

Flat-Panel Imaging Arrays for Digital Radiography

Outline Flat-Panel Imaging Arrays • Market and clinical challenges for digital radiography for Digital Radiography • Passive pixel amorphous silicon imaging arrays • Active pixel amorphous silicon imaging arrays Timothy Tredwell, Jeff Chang, Jackson Lai, Greg Heiler, Mark Shafer, John Yorkston Carestream Health, Inc., Rochester, NY 14615, USA • Active pixel LTPS imaging arrays Jin Jang, Jae Won Choi, Jae Ik Kim, Seung Hyun Park, Jun Hyuk Cheon, Sauabh Saxena, Won Kyu Lee • Silicon-on-glass circuits for future active pixel imaging Advanced Display Research Center, Kyung Hee University, Seoul, Korea arrays Arokia Nathan London Center for Nanotechnology, University College, London Eric Mozdy, Carlo Kosik Williams, Jeffery Cites, Chuan Che Wang Corning Incorporated, Sullivan Park, Corning, NY 14831, USA 2 DR: “Digital” Radiography DR: 1 step acquisition with electrical “scanning” “Flat panel” and CCD based technology (introduced ~1995) (Courtesy Imaging Dynamics Corp.) 3 4 Two-Dimensional Projection Radiography The Market Outlook for DR: Rapid Growth World’s Population is Aging • Still most common exam • >1.5 x 10 9 exams per year • Chest imaging most common 1999 2050 Procedural Volume Trends • An aging population: 2,500 • By 2050, over 25% of the population in North America, Europe, China 2,000 Nuc Med and Australia will be over 60 ULtrasound • For every 1 time a 20-year-old visits a doctor … 1,500 MR …a 60-year-old visits a doctor 26 times 1,000 CT Digital X-ray • Rising incomes in Asia and Latin America will accelerate demand Procedures (Ms) Procedures 500 Analog x-ray • Emerging economies could go direct to digital - • Cost must be low – significant market opportunity 2001 2002 2003 2004 2005 2006 2007 2008 5 Source: WHO, World Bank 6 Anatomical Noise Anatomical Noise in Projection Radiography 3-Dim 2-Dim &KHVW5DGLRJUDSK 0DPPRJUDSK\ • 3 dim. -

Invention of Digital Photograph

Invention of Digital photograph Digital photography uses cameras containing arrays of electronic photodetectors to capture images focused by a lens, as opposed to an exposure on photographic film. The captured images are digitized and stored as a computer file ready for further digital processing, viewing, electronic publishing, or digital printing. Until the advent of such technology, photographs were made by exposing light sensitive photographic film and paper, which was processed in liquid chemical solutions to develop and stabilize the image. Digital photographs are typically created solely by computer-based photoelectric and mechanical techniques, without wet bath chemical processing. The first consumer digital cameras were marketed in the late 1990s.[1] Professionals gravitated to digital slowly, and were won over when their professional work required using digital files to fulfill the demands of employers and/or clients, for faster turn- around than conventional methods would allow.[2] Starting around 2000, digital cameras were incorporated in cell phones and in the following years, cell phone cameras became widespread, particularly due to their connectivity to social media websites and email. Since 2010, the digital point-and-shoot and DSLR formats have also seen competition from the mirrorless digital camera format, which typically provides better image quality than the point-and-shoot or cell phone formats but comes in a smaller size and shape than the typical DSLR. Many mirrorless cameras accept interchangeable lenses and have advanced features through an electronic viewfinder, which replaces the through-the-lens finder image of the SLR format. While digital photography has only relatively recently become mainstream, the late 20th century saw many small developments leading to its creation. -

A High Full Well Capacity CMOS Image Sensor for Space Applications

sensors Article A High Full Well Capacity CMOS Image Sensor for Space Applications Woo-Tae Kim 1 , Cheonwi Park 1, Hyunkeun Lee 1 , Ilseop Lee 2 and Byung-Geun Lee 1,* 1 School of Electrical Engineering and Computer Science, Gwangju Institute of Science and Technology, Gwangju 61005, Korea; [email protected] (W.-T.K.); [email protected] (C.P.); [email protected] (H.L.) 2 Korea Aerospace Research Institute, Daejeon 34133, Korea; [email protected] * Correspondence: [email protected]; Tel.: +82-62-715-3231 Received: 24 January 2019; Accepted: 26 March 2019; Published: 28 March 2019 Abstract: This paper presents a high full well capacity (FWC) CMOS image sensor (CIS) for space applications. The proposed pixel design effectively increases the FWC without inducing overflow of photo-generated charge in a limited pixel area. An MOS capacitor is integrated in a pixel and accumulated charges in a photodiode are transferred to the in-pixel capacitor multiple times depending on the maximum incident light intensity. In addition, the modulation transfer function (MTF) and radiation damage effect on the pixel, which are especially important for space applications, are studied and analyzed through fabrication of the CIS. The CIS was fabricated using a 0.11 µm 1-poly 4-metal CIS process to demonstrate the proposed techniques and pixel design. A measured FWC of 103,448 electrons and MTF improvement of 300% are achieved with 6.5 µm pixel pitch. Keywords: CMOS image sensors; wide dynamic range; multiple charge transfer; space applications; radiation damage effects 1. Introduction Imaging devices are essential components in the space environment for a range of applications including earth observation, star trackers on satellites, lander and rover cameras [1]. -

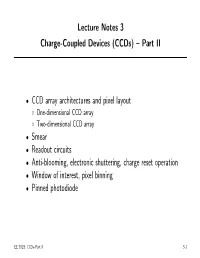

Lecture Notes 3 Charge-Coupled Devices (Ccds) – Part II • CCD

Lecture Notes 3 Charge-Coupled Devices (CCDs) { Part II • CCD array architectures and pixel layout ◦ One-dimensional CCD array ◦ Two-dimensional CCD array • Smear • Readout circuits • Anti-blooming, electronic shuttering, charge reset operation • Window of interest, pixel binning • Pinned photodiode EE 392B: CCDs{Part II 3-1 One-Dimensional (Linear) CCD Operation A. Theuwissen, \Solid State Imaging with Charge-Coupled Devices," Kluwer (1995) EE 392B: CCDs{Part II 3-2 • A line of photodiodes or photogates is used for photodetection • After integration, charge from the entire row is transferred in parallel to the horizontal CCD (HCCD) through transfer gates • New integration period begins while charge packets are transferred through the HCCD (serial transfer) to the output readout circuit (to be discussed later) • The scene can be mechanically scanned at a speed commensurate with the pixel size in the vertical direction to obtain 2D imaging • Applications: scanners, scan-and-print photocopiers, fax machines, barcode readers, silver halide film digitization, DNA sequencing • Advantages: low cost (small chip size) EE 392B: CCDs{Part II 3-3 Two-Dimensional (Area) CCD • Frame transfer CCD (FT-CCD) ◦ Full frame CCD • Interline transfer CCD (IL-CCD) • Frame-interline transfer CCD (FIT-CCD) • Time-delay-and-integration CCD (TDI-CCD) EE 392B: CCDs{Part II 3-4 Frame Transfer CCD Light−sensitive CCD array Frame−store CCD array Amplifier Output Horizontal CCD Integration Vertical shift Operation Vertical shift Horizotal shift Time EE 392B: CCDs{Part II 3-5 Pixel Layout { FT-CCD D. N. Nichols, W. Chang, B. C. Burkey, E. G. Stevens, E. A. Trabka, D. -

Digital and Advanced Imaging Equipment

CHAPTER 9 Digital and Advanced Imaging Equipment KEY TERMS active matrix array direct-to-digital radiographic systems photostimulated luminescence amorphous dual-energy x-ray absorptiometry picture archiving and communication analog-to-digital converter F-center system aspect ratio fill factor preprocessing cinefluorography frame rate postprocessing computed radiography image contrast refresh rate detective quantum efficiency image enhancement special procedures laboratory Digital Imaging and Communications image management and specular reflection in Medicine group communication system teleradiology digital fluoroscopy image restoration thin-film transistor digital radiography interpolation window level digital subtraction angiography liquid crystal display window width digital x-ray radiogrammetry Nyquist frequency OBJECTIVES At the completion of this chapter the reader should be able to do the following: • Describe the basic methods of obtaining digital cathode-ray tube cameras, videotape and videodisc radiographs recorders, and cinefluorographic equipment and discuss • State the advantages and disadvantages of digital the quality control procedures for each radiography versus conventional film/screen • Describe the various types of electronic display devices radiography and discuss the applicable quality control procedures • Discuss the quality control procedures for evaluating • Explain the basic image archiving and management digital radiographic systems networks and discuss the applicable quality control • Describe the basic methods -

Bipolar Junction Transistor As a Detector for Measuring in Diagnostic X-Ray Beams

2013 International Nuclear Atlantic Conference - INAC 2013 Recife, PE, Brazil, November 24-29, 2013 ASSOCIAÇÃO BRASILEIRA DE ENERGIA NUCLEAR - ABEN ISBN: 978-85-99141-05-2 BIPOLAR JUNCTION TRANSISTOR AS A DETECTOR FOR MEASURING IN DIAGNOSTIC X-RAY BEAMS Francisco A. Cavalcanti1,2, David S. Monte1,2, Aline N. Alves1,2, Fábio R. Barros2, Marcus A. P. Santos2, and Luiz A. P. Santos1,2 1 Departamento de Energia Nuclear Universidade Federal de Pernambuco Av. Prof. Luiz Freire, 1000 50740-540 Recife, PE [email protected] 2 Centro Regional de Ciências Nucleares do Nordeste (CRCN-NE / CNEN) Av. Prof. Luiz Freire, 1 50740-540 Recife, PE [email protected] ABSTRACT Photodiode and phototransistor are the most frequently used devices for measuring ionizing radiation in medical applications. The cited devices have the operating principle well known, however the bipolar junction transistor (BJT) is not a typical device used as a detector for measuring some physical quantities for diagnostic radiation. In fact, a photodiode, for example, has an area about 10 mm square and a BJT has an area which can be more than 10 thousands times smaller. The purpose of this paper is to bring a new technique to estimate some physical quantities or parameters in diagnostic radiation; for example, peak kilovoltage (kVp), deep dose measurements. The methodology for each type of evaluation depends on the energy range of the radiation and the physical quantity or parameter to be measured. Actually, some characteristics of the incident radiation under the device can be correlated with the readout signal, which is a function of the electrical currents in the electrodes of the BJT: Collector, Base and Emitter. -

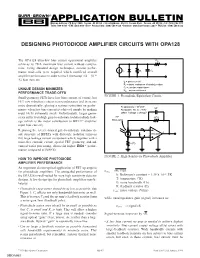

Designing Photodiode Amplifier Circuits with Opa128

® DESIGNING PHOTODIODE AMPLIFIER CIRCUITS WITH OPA128 The OPA128 ultra-low bias current operational amplifier RS achieves its 75fA maximum bias current without compro- mise. Using standard design techniques, serious perfor- I R C mance trade-offs were required which sacrificed overall P J J amplifier performance in order to reach femtoamp (fA = 10–15 A) bias currents. IP = photocurrent RJ = shunt resistance of diode junction CJ = junction capacitance UNIQUE DESIGN MINIMIZES R = series resistance PERFORMANCE TRADE-OFFS S FIGURE 1. Photodiode Equivalent Circuit. Small-geometry FETs have low bias current, of course, but FET size reduction reduces transconductance and increases noise dramatically, placing a serious restriction on perfor- Responsivity ≈ 109V/W 5pF mance when low bias current is achieved simply by making Bandwidth: DC to ≈ 30Hz input FETs extremely small. Unfortunately, larger geom- Offset Voltage ≈ ±485µV etries suffer from high gate-to-substrate isolation diode leak- HP 109Ω age (which is the major contribution to BIFET® amplifier 5082-4204 input bias current). Replacing the reverse-biased gate-to-substrate isolation di- 2 6 OPA128LM ode structure of BlFETs with dielectric isolation removes 3 this large leakage current component which, together with a 8 noise-free cascode circuit, special FET geometry, and ad- 109Ω vanced wafer processing, allows far higher Difet ® perfor- mance compared to BIFETs. FIGURE 2. High-Sensitivity Photodiode Amplifier. HOW TO IMPROVE PHOTODIODE AMPLIFIER PERFORMANCE An important electro-optical application of FET op amps is √ for photodiode amplifiers. The unequaled performance of eOUT = 4k TBR the OPA128 is well-suited for very high sensitivity detector k: Boltzman’s constant = 1.38 x 10–23 J/K ° designs. -

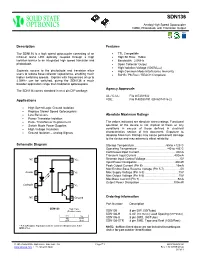

SDN136 Analog High Speed Optocoupler 1Mbd, Photodiode with Transistor Output

SDN136 Analog High Speed Optocoupler 1MBd, Photodiode with Transistor Output Description Features The SDN136 is a high speed optocoupler consisting of an TTL Compatible infrared GaAs LED optically coupled through a high High Bit Rate: 1Mb/s isolation barrier to an integrated high speed transistor and Bandwidth: 2.0MHz photodiode. Open Collector Output High Isolation Voltage (5000VRMS) Separate access to the photodiode and transistor allow High Common Mode Interference Immunity users to reduce base-collector capacitance, enabling much RoHS / Pb-Free / REACH Compliant higher switching speeds. Signals with frequencies of up to 2.0MHz can be switched, giving the SDN136 a much broader application range than traditional optocouplers. Agency Approvals The SDN136 comes standard in an 8 pin DIP package. UL / C-UL: File # E201932 Applications VDE: File # 40035191 (EN 60747-5-2) High Speed Logic Ground Isolation Replace Slower Speed Optocouplers Absolute Maximum Ratings Line Receivers Power Transistor Isolation Pulse Transformer Replacement The values indicated are absolute stress ratings. Functional Switch Mode Power Supplies operation of the device is not implied at these or any High Voltage Insulation conditions in excess of those defined in electrical Ground Isolation – Analog Signals characteristics section of this document. Exposure to absolute Maximum Ratings may cause permanent damage to the device and may adversely affect reliability. Schematic Diagram Storage Temperature …………………………..-55 to +125°C Operating Temperature …………………………-40