Adder (electronics)

Top View

- Comparative Analysis of Different Types of Full Adder Circuits

- Lecture 12 Binary Adder-Subtractor.Pdf

- 15-740/18-740 Computer Architecture Lecture 4: ISA Tradeoffs

- High-Speed VLSI Arithmetic Units: Adders and Multipliers

- Power Efficient CMOS Full Adders with Reduced Transistor Count

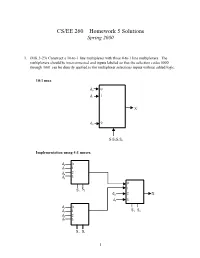

- Multiplexer-Based Design of Adders/Subtractors and Logic

- Arithmetic Logic UNIT

- Adder and Subtractor Circuits

- FPGA Implementation of a High Speed Multistage Pipelined Adder Based CORDIC Structure for Large Operand Word Lengths ISSN 2047-3338

- Design and Analysis of GDI Based Full Adder Circuit for Low Power Applications

- 74LS283 4-Bit Binary Adder with Fast Carry

- Dynamic 16-Bit Carry- Lookahead Adder/Subtractor Jason Bosko John Choi Paul Verheggen

- COMBINATIONAL CIRCUITS I (Adders, Decoders, Multiplexers)

- Binary Adder X Y X + Y (Binary Sum) • Binary Addition 0 + 0 = 0 – Single Bit Addition 0 + 1 = 1 1 + 0 = 1 1 + 1 = 10 (Binary, I.E

- Systems I: Computer Organization and Architecture

- CMOS Binary Full Adder

- A Carry Save Adder Design