Integrated Circuit and System Design. Power and Timing Modeling

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Oriented Conferences Four Solutions

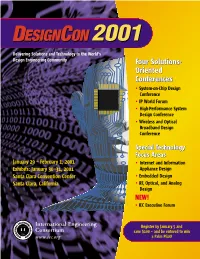

Delivering Solutions and Technology to the World’s Design Engineering Community Four Solutions- Oriented Conferences • System-on-Chip Design Conference • IP World Forum • High-Performance System Design Conference • Wireless and Optical Broadband Design Conference Special Technology Focus Areas January 29 – February 1, 2001 • Internet and Information Exhibits: January 30–31, 2001 Appliance Design Santa Clara Convention Center • Embedded Design Santa Clara, California • RF, Optical, and Analog Design NEW! • IEC Executive Forum International Engineering Register by January 5 and Consortium save $100 – and be entered to win www.iec.org a Palm Pilot! Practical Design Solutions Practical design-engineering solutions presented by practicing engineers—The DesignCon reputation of excellence has been built largely by the practical nature of its sessions. Design engineers hand selected by our team of professionals provide you with the best electronic design and silicon-solutions information available in the industry. DesignCon provides attendees with DesignCon has an established reputation for the high design solutions from peers and professionals. quality of its papers and its expert-level speakers from Silicon Valley and around the world. Each year more than 100 industry pioneers bring to light the design-engineering solutions that are on the leading edge of technology. This elite group of design engineers presents unique case studies, technology innovations, practical techniques, design tips, and application overviews. Who Should Attend Any professionals who need to stay on top of current information regarding design-engineering theories, The most complete educational experience techniques, and application strategies should attend this in the industry conference. DesignCon attracts engineers and allied The four conference options of DesignCon 2001 provide a professionals from all levels and disciplines. -

Table of Contents 2006 IEEE Symposium on VLSI Technology

13eds02.qxd 3/6/06 8:36 AM Page 1 IEEE E D S ELECTRONELECTRON DEVICESDEVICES SOCIETYSOCIETY Newsletter APRIL 2006 Vol. 13, No. 2 ISSN:1074 1879 Editor-in-Chief: Ninoslav D. Stojadinovic 2006 IEEE Symposium Table of Contents on VLSI Technology Upcoming Technical Meetings .......................1 • 2006 VLSI • 2006 ASMC • 2006 IITC • 2006 UGIM Outgoing Message from the 2004-5 EDS President...................................3 Society News.........................................................9 • December 2005 AdCom Meeting Summary • Message from the EDS Newsletter Editor-in-Chief • EDS Educational Activities Committee Report • EDS Nanotechnology Committee Report • EDS Photovoltaic Devices Committee Report • 2005 EDS J.J. Ebers Award Winner • 2006 EDS J.J. Ebers Award Call for Nominations • 2005 EDS Distinguished Service Award Winner • 2006 Charles Stark Draper Prize Hilton Hawaiian Village, Honolulu, Hawaii • 23 EDS Members Elected to the IEEE The 26th Annual IEEE Symposium on VLSI Technology will Grade of Fellow be held June 13-15, 2006, at the Hilton Hawaiian Village in • 2005 Class of EDS Fellows Honored at IEDM Honolulu, Hawaii. The VLSI Technology Symposium is joint- ly sponsored by the IEEE Electron Devices Society (EDS) and • EDS Members Named Winners of the Japan Society of Applied Physics (JSAP). 2006 IEEE Technical Field Awards The VLSI Symposium is well recognized as one of the • EDS Regions 1-3 & 7 Chapters Meeting Summary premiere conferences on semiconductor technology, and research results presented at the conference represent a • 2005 EDS Chapter of the Year Award broad spectrum of VLSI technology topics, including: • EDS Members Recently Elected • New concepts and breakthroughs in VLSI devices and to IEEE Senior Member Grade processes. -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

Selective GUIDE to LITERATURE CAN INTEGRATED CIRCUITS

Engineering Literature Guides, Number 18 SELEcTivE GUIDE To LITERATURE CAN INTEGRATED CIRCUITS Compiled 1~y: Nestor L. 0sorio Northern Illinois University Libraries American Society for Engineering Education 1818 N Street, NW, Suite 600 Washington, DC 20036 Copyright (c) 1994 by American Society for Engineering Education 1818 N. Street, N.W., Suite 600 Washington, DC 20036-2479 International Standard Book Number: 0-87823-122-6 Library of Congress Catalog Card Number: Manufactured in the United States of America Beth L. Brin, Series Co-editor Science-Engineering Library University of Arizona Tucson, AZ 85721-001 Godlind Johnson, Series Co-editor Engineering Library SUNY-Stony Brook Stony Brook, NY 11794-2225 ASEE is not responsible for statements made or opinions expressed in this publication. TABLE OF CONTENTS Introduction... ....................................... ..................... .. ..... ............................ .. .. ......1 Bibliographies and Literature Guides . .. .. .. .2 Printed and Electronic Indexes and Abstracts . .3 Encyclopedias. : . .. ..6 Dictionaries . .. .. .. .7 Handbooks and Tables . .. .. .. .. .. .. .8 Directories: Product Information, Trade Catalogs . .. .. .. .10 Standards and Specifications . .. .13 Major Periodicals . .. .. .. .14 Major Proceedings . .. .. : . .. .. 17 Important Books . .. .. .19 Major. Integrated Circuit Manufacturers . .. .. ..20 Appendix: Selected Information Services . .. .. .. ..23 ~I INTRODUCTION ver the last 25 years significant changes have been 0 generated in industry by the -

基于 Arm ® Cortex® -M 的 微控制器产品方案介绍

基于 Arm® Cortex® -M 的 微控制器产品方案介绍 Wei Wang September 2018 | APF-TRD-T3275 Company External – NXP, the NXP logo, and NXP secure connections for a smarter world are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2018 NXP B.V. Agenda • 通用市场新产品概览 • 专用市场新产品概览 • 跨界处理器 • 一站式开发工具和方案 • 参考设计和方案 • 物联网开发平台 • i.MX RT • Kinetis, DSC, S08 • LPC • 无线连接 – JN/QN/KW PUBLIC 1 关注 NXP 官方公众号和 MCU 技术公众号 NXP客栈 恩智浦MCU加油站 PUBLIC 2 HOME ETHERNET GATEWAY SWITCH Cloud Infrastructure NXP Cloud Software Platform built on top of leading cloud partners (e.g. Azure, AWS, GCP, Alibaba, Baidu, etc.) WIRELESS INDUSTRIAL ROUTER CONTROLLER Customer Solution App App App Provisioning & Authentication Middleware Data Analytics RTOS, Linux, Android … Services foundation NXP SW Platform Machine Learning PUBLIC 3 面向 AI-IOT 的可扩展处理器平台 M4 – A53 – A72 4K HEVC M4 - A53 128 GFLOPS GPU 4K HDR - Dolby A7 64GFLOPS GPU LX2160 CSI - LCD LS 2088 16xA72 M4 – A35 LS1046 280 GFlops 4K i.MX 8 8xA72 100 Gbps 28GFLOPS GPU LS1043 i.MX 8M 128 GFlops 40 Gbps i.MX 8X LS 1012 4xA72 58 GFlops i.MX 6UL/ULL/ULZ 4xA53 20 Gbps i.MX RT i.MX 7ULP 50 GFlops Performance 1xA53 10 Gbps 12 GFlops M4 + Connectivity 2 Gbps Secure Boot Crypto accel K4 LPC QN, JN M7 @ 600 MHz QSPI Secure Boot Multimedia Acceleration Networking Acceleration Integration PUBLIC 4 可扩展的嵌入式 AI-IOT “云管端”平台 Voice Gesture Active Object Personal / Home Multi-stream Multi-camera Augmented Processing Control Recognition Property Environment Camera Observation Reality & 360 view Low-end Edge Compute -

IC Start-Ups 1987 : the Next Generation, 1986

Start-up Company Datapoints 1957-1967 17 Started 13 Acquired 2 Closed 12% Closed 1957 1 1958 0 1959 1 1960 0 1961 4 1962 2 1963 2 1964 1 1965 0 1966 3 1967 3 1968-1976 54 Started 20 Acquired 19 Closed 35% Closed 1968 13 1969 10 1970 4 1971 6 1972 9 1973 2 1974 5 1975 2 1976 3 1977-1987 157 Companies Started 11 Companies Closed 7 Companies Acquired/Merged 1977 3 1978 7 1979 4 1980 7 1981 15 1982 10 1983 35 1984 28 1985 24 1986 9 1987 15 •May 1988 Total Companies 157 Company Profiles 139 Closed Companies 11 1985 ABM (Inactive) San Jose, CA GaAs Opto 1982 Array Devices San Diego, CA ASICs 1983 Hyundai (Closed) Santa Clara, CA Memory 1983 Iridian (Closed) Chatsworth, CA GaAs PETs 1983 Laserpath (Closed) Sunyyvale, CA ASICs 1985 Sahni (Closed) Sunnyvale, CA ASICs 1981 Telmos (Chapter 11) Sunnyvale, CA ASIC, linear, opto 1983 Texet (Closed) Allen, Texas Discrete 1980 Trilogy (Closed) Cupertino, Ca Waferscale integration 1984 Wafer Teen (Closed) California Logic 1981 Zytrex (Closed) Sunnyvale, CA CMOS memory, logic Acquired Companies 7 1982 CMA (Merged) Milpitas, CA ASICs 1984 mteg. Power (Acq) Scotland Linear 1981 Panatech (Acquired) Santa Clara, CA ASICs 1981 Sig. Processor (Acq) Utan DSP 1984 Silicon Macro (Acq) San Jose, CA CMOS Memory 1963 Vatic (Merged) Mesa, Arizona ASICs 1983 Visic (Acquired) San Jose, CA Memory May 1988 Total Companies 157 Semiconductor Companies Formed in 1987 (15) Aspen Semiconductor San Jose, CA BCL Memory, ASICs Chartered Semiconductor Singapore Foundry Conductus Palo Alto, CA Superconductivity Cree Research North Carolina Silicon Carbide Discrete G-2 Milpitas, CA Micros Genesis Microchip Canada ASICs GL Micro Devices Santa Clara, CA CMOS products Graphics Communication Japan Micros Hualon Micro-Electronics Taiwan Linear, micros, ASICs Linear Integ. -

Arm Holdings: Ip Licensing to Internet of Things

SMU-19-0015 ARM HOLDINGS: IP LICENSING TO INTERNET OF THINGS Innovation is about encouragement, investment, and meeting the needs of the customer. -Jamie Urquhart, Co-founder ARM Holdings In the summer of 2016, Jamie Urquhart, co-founder of ARM Holdings plc (ARM) was enjoying his breakfast in a tiny village on the outskirts of Cambridge, UK. As he waited for his piping hot coffee to cool, the news on ARM caught his attention. ‘ARM shares have rallied 63% ahead of Softbank takeover’ informed the report. Old recollections trickled through his mind –building the ARM architecture over long days, reminiscences of business trips to Japan, and fascinating memories of establishing a hugely successful company from scratch. ARM had started its journey in 1990 with a team of 12 co-founders. Over the years, the company had grown to become a leader in semiconductor Intellectual Property (IP) development. At the heart of ARM’s offering was its microprocessor architecture and its IP licensing business model, paired alongside strategic partnerships with semi-conductor and original equipment manufacturing (OEM) firms. ARM had also developed an eco-system of partner organisations which helped accelerate the adoption of its IP. 2016 had brought in a wave of changes for ARM. Just weeks after UK had voted to leave the European Union, Softbank, a Japanese conglomerate had expressed its desire to acquire ARM. Masayoshi Son, Chairman and Chief Executive of Softbank, had told reporters in London that the deal would highlight his confidence in the British economy. He had made an offer of US$31.69 billion to ARM, betting that the company would help Softbank become a leader in the Internet of Things (IoT).1 At the time, ARM was UK’s largest technology firm, and Softbank’s takeover of ARM would be the largest acquisition of a European technology business. -

Company Vendor ID (Decimal Format) (AVL) Ditest Fahrzeugdiagnose Gmbh 4621 @Pos.Com 3765 0XF8 Limited 10737 1MORE INC

Vendor ID Company (Decimal Format) (AVL) DiTEST Fahrzeugdiagnose GmbH 4621 @pos.com 3765 0XF8 Limited 10737 1MORE INC. 12048 360fly, Inc. 11161 3C TEK CORP. 9397 3D Imaging & Simulations Corp. (3DISC) 11190 3D Systems Corporation 10632 3DRUDDER 11770 3eYamaichi Electronics Co., Ltd. 8709 3M Cogent, Inc. 7717 3M Scott 8463 3T B.V. 11721 4iiii Innovations Inc. 10009 4Links Limited 10728 4MOD Technology 10244 64seconds, Inc. 12215 77 Elektronika Kft. 11175 89 North, Inc. 12070 Shenzhen 8Bitdo Tech Co., Ltd. 11720 90meter Solutions, Inc. 12086 A‐FOUR TECH CO., LTD. 2522 A‐One Co., Ltd. 10116 A‐Tec Subsystem, Inc. 2164 A‐VEKT K.K. 11459 A. Eberle GmbH & Co. KG 6910 a.tron3d GmbH 9965 A&T Corporation 11849 Aaronia AG 12146 abatec group AG 10371 ABB India Limited 11250 ABILITY ENTERPRISE CO., LTD. 5145 Abionic SA 12412 AbleNet Inc. 8262 Ableton AG 10626 ABOV Semiconductor Co., Ltd. 6697 Absolute USA 10972 AcBel Polytech Inc. 12335 Access Network Technology Limited 10568 ACCUCOMM, INC. 10219 Accumetrics Associates, Inc. 10392 Accusys, Inc. 5055 Ace Karaoke Corp. 8799 ACELLA 8758 Acer, Inc. 1282 Aces Electronics Co., Ltd. 7347 Aclima Inc. 10273 ACON, Advanced‐Connectek, Inc. 1314 Acoustic Arc Technology Holding Limited 12353 ACR Braendli & Voegeli AG 11152 Acromag Inc. 9855 Acroname Inc. 9471 Action Industries (M) SDN BHD 11715 Action Star Technology Co., Ltd. 2101 Actions Microelectronics Co., Ltd. 7649 Actions Semiconductor Co., Ltd. 4310 Active Mind Technology 10505 Qorvo, Inc 11744 Activision 5168 Acute Technology Inc. 10876 Adam Tech 5437 Adapt‐IP Company 10990 Adaptertek Technology Co., Ltd. 11329 ADATA Technology Co., Ltd. -

ACORN RISC MACHINE Jitendra Marathe ARM Is a Reduced

SRJIS / BIMONTHLY/JITENDRA MARATHE. (581-585) ACORN RISC MACHINE Jitendra Marathe ARM is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by ARM Holdings. It was named the Advanced RISC Machine and, before that, the Acorn RISC Machine. The ARM architecture is the most widely used 32-bit instruction set architecture in numbers produced. Originally conceived by Acorn Computers for use in its personal computers, the first ARM-based products were the co-processor modules for the BBC series of computers. Features and applications: In 2005 about 98% of the more than one billion mobile phones sold each year used at least one ARM processor. As of 2009 ARM processors accounted for approximately 90% of all embedded 32-bit RISC processors and were used extensively in consumer electronics, including personal digital assistants (PDAs), tablets, mobile phones, digital media and music players, hand-held game consoles, calculators and computer peripherals such as hard drives and routers. Licensees: The ARM architecture is licensable. Companies that are current or former ARM licensees include Alcatel-Lucent, Apple Inc., AppliedMicro, Atmel, Broadcom, Cirrus Logic, CSR_plc, Digital Equipment Corporation, Ember, Energy Micro, Freescale, Intel (through DEC), LG, Marvell Technology Group, Microsemi, Microsoft, NEC, Nintendo, Nuvoton, Nvidia, Sony, NXP (formerly Philips Semiconductor), Oki, ON Semiconductor, Psion, Qualcomm, Renesas, Samsung, Sharp, Silicon Labs, STMicroelectronics, Symbios Logic, Texas Instruments, VLSI Technology, Yamaha, Fuzhou Rockchip, and ZiiLABS. In addition to the abstract architecture, ARM offers several microprocessor core designs, including the ARM7, ARM9, ARM11, Cortex- A8, Cortex-A9, and Cortex-A15. Companies often license these designs from ARM to manufacture and integrate into their own system on a chip (SoC) with other components like RAM, GPUs, or radio basebands (for mobile phones). -

Survey on Low Cost Integrated Circuit Design

Special Issue - 2015 International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 ISNCESR-2015 Conference Proceedings Survey on Low Cost Integrated Circuit Design Jitendra Jugele Kanaklata Verma ECE ME (VLSI) ECE ME (VLSI) SSCET, Bhilai, India SSCET, Bhilai, India Sourabh Jain M.TECH (VLSI) JAIN University(Banglore) Abstract- The growing market of mobile, battery-powered ICs have two main advantages: electronic systems (e.g. cellular phones, PDA etc.) demand the design of micro electronics circuits with low power dissipation. 1. Cost. More generally, as size, density and complexity of the chips 2. Performance. continue to increase, the difficulty in providing cooling might Cost is low because the chips, with all their components, are either add significant cost or limit the functionality of the printed as a unit by VLSI technology like photolithography computing systems which make use of those integrated circuits. rather than being constructed one component like transistor at The paper presents study of low cost integrated circuit and its a time. Furthermore, packaged Integrated Circuits use much applications. An integrated circuit is a set of electronic circuits less material than discrete circuits. on one small plate ("chip") of semiconductor material normally silicon and germanium in rare cases. This may be made smaller Performance is much better because the Integrated circuits than a discrete circuit made from independent components. ICs components switch quickly and consume less power have two main advantages of performance and cost. Integrated (compared to their counterparts) as a result of the close circuits are used in virtually all electronic equipments today and proximity and small size of the components have revolutionized the world of electronics. -

DOT/FAA/AR-95/31 ___Design, Test, and Certification Issues For

DOT/FAA/AR-95/31 Design, Test, and Certification Office of Aviation Research Issues for Complex Integrated Washington, D.C. 20591 Circuits August 1996 Final Report This document is available to the U.S. public through the National Technical Information Service, Springfield, Virginia 22161. U.S. Department of Transportation Federal Aviation Administration Technical Report Documentation Page 1. Report No. 2. Government Accession No. 3. Recipient's Catalog No. DOT/FAA/AR-95/31 5. Report Date 4. Title and Subtitle August 1996 DESIGN, TEST, AND CERTIFICATION ISSUES FOR COMPLEX INTEGRATED CIRCUITS 6. Performing Organization Code 7. Author(s) 8. Performing Organization Report No. L. Harrison and B. Landell 9. Performing Organization Name and Address 10. Work Unit No. (TRAIS) Galaxy Scientific Corporation 2500 English Creek Avenue Building 11 11. Contract or Grant No. Egg Harbor Township, NJ 08234-5562 DTFA03-89-C-00043 12. Sponsoring Agency Name and Address 13. Type of Report and Period Covered U.S. Department of Transportation Final Report Office of Aviation Research Washington, D.C. 20591 14. Sponsoring Agency Code AAR-421 15. Supplementary Notes Peter J. Saraceni. William J. Hughes Technical Center Program Manager, (609) 485-5577, Fax x 4005, [email protected] 16 Abstract This report provides an overview of complex integrated circuit technology, focusing particularly upon application specific integrated circuits. This report is intended to assist FAA certification engineers in making safety assessments of new technologies. It examines complex integrated circuit technology, focusing on three fields: design, test, and certification.. It provides the reader with the background and a basic understanding of the fundamentals of these fields. -

University of Cincinnati

UNIVERSITY OF CINCINNATI November 20 , 20 02 I, Vikram Arora , hereby submit this as part of the requirements for the degree of: Master of Science in: Computer Engineering It is entitled: “An Efficient Built-In Self-Diagnostic Method for Non-Traditional Faults of Embedded Memory Arrays” Approved by: Dr. Wen-Ben Jone Dr. Ranga Vemuri Dr. Harold Carter An Efficient Built-In Self-Diagnostic Method for Non-Traditional Faults of Embedded Memory Arrays A thesis submitted to the Division of Research and Advanced Studies of the University of Cincinnati in partial fulfillment of the requirements for the degree of Master of Science in the Department of Electrical and Computer Engineering and Computer Science of the College of Engineering November 2002 by Vikram Arora B.E.(E.E.), University of Madras, India, June 2000 Thesis Advisor and Committee Chair: Dr. Wen-Ben Jone To my dearest parents Abstract With improvements in VLSI technology, more and more components are fabricated onto a single chip. The importance of system on chip (SoC) is growing rapidly in this era. It is estimated that the percentage of chip area occupied by embedded memory arrays on a SoC will rise to as high as 94% in the next decade. Even worse, memory arrays are more vulnerable to fabrication defects due to the higher packing density of transistors. If some cells of the embedded memory arrays on a SoC are defective, it is not economical to throw the chip away. The solution to this problem lies in designing an intelligent piece of built-in hardware which tests, diagnoses, and repairs the faulty cells of embedded memory arrays.