Oriented Conferences Four Solutions

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Organising Committees

DATE 2005 Executive Committee GENERAL CHAIR PROGRAMME CHAIR Nobert Wehn Luca Benini Kaiserslautern U, DE DEIS – Bologna U, IT VICE CHAIR & PAST PROG. CHAIR VICE PROGRAMME CHAIR Georges Gielen Donatella Sciuto KU Leuven, BE Politecnico di Milano, IT FINANCE CHAIR PAST GENERAL CHAIR Rudy Lauwereins Joan Figueras IMEC, Leuven, BE UP Catalunya, Barcelona, ES DESIGNERS’ FORUM DESIGNERS’ FORUM Menno Lindwer Christoph Heer Philips, Eindhoven, NL Infineon, Munich, DE SPECIAL SESSIONS & DATE REP AT DAC FRIDAY WORKSHOPS Ahmed Jerraya Bashir Al-Hashimi TIMA, Grenoble, FR Southampton U, UK INTERACTIVE PRESENTATIONS ELECTRONIC REVIEW Eugenio Villar Wolfgang Mueller Cantabria U, ES Paderborn U, DE WEB MASTER AUDIO VISUAL Udo Kebschull Jaume Segura Heidelberg U, DE Illes Baleares U, ES TUTORIALS & MASTER COURSES FRINGE MEETINGS Enrico Macii Michel Renovell Politecnico di Torino, IT LIRMM, Montpellier, FR AUTOMOTIVE DAY BIOCHIPS DAY Juergen Bortolazzi Christian Paulus DaimlerChrysler, DE Infineon, Munich, DE PROCEEDINGS EXHIBITION PROGRAMME Christophe Bobda Juergen Haase Erlangen U, DE edacentrum, Hannover, DE UNIVERSITY BOOTH UNIVERSITY BOOTH & ICCAD Volker Schoeber REPRESENTATIVE edacentrum, Hannover, DE Wolfgang Rosenstiel Tuebingen U/FZI, DE AWARDS & DATE REP. AT ASPDAC PCB SYMPOSIUM Peter Marwedel Rainer Asfalg Dortmund U, DE Mentor Graphics, DE TRAVEL GRANTS COMMUNICATIONS Marta Rencz Bernard Courtois TU Budapest, HU TIMA, Grenoble, FR LOCAL ARRANGEMENTS PRESS LIASON Volker Dueppe Fred Santamaria Siemens, DE Infotest, Paris, FR ESF CHAIR & EDAA -

Important Notice Dear Customer, on 7 February 2017 The

Important notice Dear Customer, On 7 February 2017 the former NXP Standard Product business became a new company with the tradename Nexperia. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below. Instead of http://www.nxp.com, http://www.philips.com/ or http://www.semiconductors.philips.com/, use http://www.nexperia.com Instead of [email protected] or [email protected], use [email protected] (email) Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below: - © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved Should be replaced with: - © Nexperia B.V. (year). All rights reserved. If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via [email protected]). Thank you for your cooperation and understanding, Kind regards, Team Nexperia PMN27XPE 20 V, single P-channel Trench MOSFET 20 September 2012 Product data sheet 1. Product profile 1.1 General description P-channel enhancement mode Field-Effect Transistor (FET) in a small SOT457 (SC-74) Surface-Mounted Device (SMD) plastic package using Trench MOSFET technology. 1.2 Features and benefits • Fast switching • Trench MOSFET technology • 2 kV ESD protection 1.3 Applications • Relay driver • High-speed line driver • High-side loadswitch • Switching circuits 1.4 Quick reference data Table 1. -

Exhibition Report

Exhibition Report Japan Electronics and Information Technology Industries Association (JEITA) Contents Exhibition Outline 1 Exhibition Configuration 2 1. Scope of Exhibits 2 2. Conference 2 3. Number of Exhibitors and Booths 2 4. Suite Exhibits 2 5. Exhibitors 3 Conference Activities 4 1. Exhibitor Seminars 4 2. Keynote Speech 4 3. Special Event Stage 4 4. The 13th FPGA/PLD Design Conference 4 5. FPGA/PLD Design Conference User’s Presentations 4 6. IP(Intellectual Property) Flea Market in EDSFair 4 7. System Design Forum 2006 Conference 4 Other Events and Special Projects 5 1. Opening Ceremony 5 2. University Plaza 5 3. Venture Conpany Pavilion 5 4. EDAC Reception 5 5. Press 5 Number of Visitors 6 Results of Visitor Questionnaire 6-7 Exhibition Outline Name . Electronic Design and Solution Fair 2006 (EDSFair2006) Duration . Thursday, January 26 and Friday, January 27, 2006 (2 days) 10:00 a.m. to 6:00 p.m. Location . Pacifico Yokohama (Halls C-D hall and Annex Hall) 1-1-1 Minato Mirai, Nishi-ku, Yokohama 220-0012, Japan Admission. Exhibition: Free (registration required at show entrance) Conference: Fees charged for some sessions Sponsorship . Japan Electronics and Information Technology Industries Association (JEITA) Cooperation . Electronic Design Automation Consortium (EDAC) Support . Ministry of the Economy, Trade and Industry, Japan (METI) Embassy of the United States of America in Japan Distributors Association of Foreign Semiconductors (DAFS) City of Yokohama Assistance . Institute of Electronics, Information and Communication Engineers (IEICE) Information Processing Society of Japan (IPSJ) Japan Printed Circuit Association (JPCA) Spacial Assistance. Hewlett-Packard Japan, Ltd. Sun Microsystems K.K Management . -

Table of Contents 2006 IEEE Symposium on VLSI Technology

13eds02.qxd 3/6/06 8:36 AM Page 1 IEEE E D S ELECTRONELECTRON DEVICESDEVICES SOCIETYSOCIETY Newsletter APRIL 2006 Vol. 13, No. 2 ISSN:1074 1879 Editor-in-Chief: Ninoslav D. Stojadinovic 2006 IEEE Symposium Table of Contents on VLSI Technology Upcoming Technical Meetings .......................1 • 2006 VLSI • 2006 ASMC • 2006 IITC • 2006 UGIM Outgoing Message from the 2004-5 EDS President...................................3 Society News.........................................................9 • December 2005 AdCom Meeting Summary • Message from the EDS Newsletter Editor-in-Chief • EDS Educational Activities Committee Report • EDS Nanotechnology Committee Report • EDS Photovoltaic Devices Committee Report • 2005 EDS J.J. Ebers Award Winner • 2006 EDS J.J. Ebers Award Call for Nominations • 2005 EDS Distinguished Service Award Winner • 2006 Charles Stark Draper Prize Hilton Hawaiian Village, Honolulu, Hawaii • 23 EDS Members Elected to the IEEE The 26th Annual IEEE Symposium on VLSI Technology will Grade of Fellow be held June 13-15, 2006, at the Hilton Hawaiian Village in • 2005 Class of EDS Fellows Honored at IEDM Honolulu, Hawaii. The VLSI Technology Symposium is joint- ly sponsored by the IEEE Electron Devices Society (EDS) and • EDS Members Named Winners of the Japan Society of Applied Physics (JSAP). 2006 IEEE Technical Field Awards The VLSI Symposium is well recognized as one of the • EDS Regions 1-3 & 7 Chapters Meeting Summary premiere conferences on semiconductor technology, and research results presented at the conference represent a • 2005 EDS Chapter of the Year Award broad spectrum of VLSI technology topics, including: • EDS Members Recently Elected • New concepts and breakthroughs in VLSI devices and to IEEE Senior Member Grade processes. -

6800/68000 Cmos

Click Here to Request a Large Quantity Quote 6800/68000 CMOS Jameco Manufacturer Manufacturer Description Package Product Type Organization Family Application Price 1 Part # Part # 130366 Major Brands 00130366 420 PIECE DIODE REFILL PACKAGE $29.95 130374 Major Brands 00130374 560 Piece Transistor Kit Refill Package $54.95 130391 Major Brands 00130391 420 Piece 74LS Logic Series Refill Package $214.95 130403 Major Brands 00130403 300 PIECE CD4000 SERIES REFILL PACKAGE $74.95 130411 Major Brands 00130411 480 PIECE LINEAR SERIES REFILL PACKAGE $164.95 1542961 Vishay 1.5KE16CA TVS Diode 22.5V Clamp 66.7A Ipp Through Hole 1500W DO-201 $0.49 1.5KE 2303247 Major Brands 1.5KE8.2C TVS Diode 12.1V Clamp 125.6A Ipp DO-201 DO-201 $0.59 35924 Major Brands 1N1188 Diode 1N1188 400 VOLT 35 AMP SILICON RECTIFIER DO-5 Stud Rectifier $3.95 2197610 Kest Parts 1N1190A Diode 1N1190A Power Silicon Rectifier 40 Amp 600V DO-5 DO-5 Stud Rectifier $4.95 2197628 Kest Parts 1N1190RA Diode 1N1190RA 40A 600V Power Silicon Rectifier DO-5 Stud Rectifier $4.95 2287679 Major Brands 1N1202A 200V 12A Rectifier Stud Mount DO-203 DO-203 Stud Rectifier $1.95 35941 Major Brands 1N270 Diode 1N270 Germanium 1 Volt @ 200Ma DO-7 General $1.19 Purpose 2220533 Major Brands 1N34A Diode 1N34A General Purpose Germanium DO-7 General $1.95 Purpose 35975 Major Brands 1N4001 Diode 1N4001 50 Volt 1 Amp General Purpose Rectifier DO-41 Standard $0.09 76961 Major Brands 1N4002 Diode 1N4002 100 Volt 1A DO-41 package DO-41 Standard $0.09 76970 Major Brands 1N4003 Diode 1N4003 Rectifier 200 Volt -

152F580552eb358625881dd680

Products Catalog Index PART NO. MANUFACTURER DESCRIPTION URL PRICE Q65112A2615 OSRAM OPTO Q65112A2615 http://www.searchdatasheet.com/Q65112A2615-datasheet.html QUOTE SEMICONDUCTORS XR33053ID-F EXAR Transceiver 1Mbps 3.3V/5V http://www.searchdatasheet.com/XR33053ID-F-datasheet.html QUOTE 14-Pin SOIC N Tube Q65111A7362 OSRAM OPTO LED Uni-Color White 2-Pin http://www.searchdatasheet.com/Q65111A7362-datasheet.html QUOTE SEMICONDUCTORS SMD T/R EL-17-21UYC/S530-A2/TR8 EVERLIGHT EL-17-21UYC/S530-A2/TR8 http://www.searchdatasheet.com/EL-17-21UYC%2FS530-A2%2FTR8-datasheet.html QUOTE ELECTRONICS Q65112A2616 OSRAM OPTO Q65112A2616 http://www.searchdatasheet.com/Q65112A2616-datasheet.html QUOTE SEMICONDUCTORS Q65111A9950 OSRAM OPTO Q65111A9950 http://www.searchdatasheet.com/Q65111A9950-datasheet.html QUOTE SEMICONDUCTORS Q65112A2629 OSRAM OPTO Q65112A2629 http://www.searchdatasheet.com/Q65112A2629-datasheet.html QUOTE SEMICONDUCTORS Q65112A0819 OSRAM OPTO LED Uni-Color White 2-Pin http://www.searchdatasheet.com/Q65112A0819-datasheet.html QUOTE SEMICONDUCTORS CSMD EP Q65111A9208 OSRAM OPTO Q65111A9208 http://www.searchdatasheet.com/Q65111A9208-datasheet.html QUOTE SEMICONDUCTORS Q65111A8966 OSRAM OPTO Q65111A8966 http://www.searchdatasheet.com/Q65111A8966-datasheet.html QUOTE SEMICONDUCTORS RLR20C1201GMRE6 VISHAY Res Metal Film 1.2K Ohm http://www.searchdatasheet.com/RLR20C1201GMRE6-datasheet.html QUOTE 2% 0.5W(1/2W) ±100ppm/C 1% Epoxy AXL T/R EVMB Connect One Evaluation Master Kit with http://www.searchdatasheet.com/EVMB-datasheet.html QUOTE Semiconductors -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

28Th IEEE VLSI Test Symposium (VTS 2010) Santa Cruz, CA, April 19-21, 2010

28th IEEE VLSI Test Symposium (VTS 2010) Santa Cruz, CA, April 19-21, 2010 Preliminary Program (as of 3/25/10) Monday, 4/19/10 Plenary Session (9:00 – 11:00) Break (11:00 – 11:15) Sessions 1 (11:15 – 12:15) Session 1A: Delay & Performance Test 1 Moderator: M. Batek - Broadcom Fast Path Selection for Testing of Small Delay Defects Considering Path Correlations Z. He, T. Lv - Institute of Computing Technology, H. Li, X. Li - Chinese Academy of Sciences Identification of Critical Primitive Path Delay Faults without any Path Enumeration K. Christou, M. Michael, S. Neophytou - University of Cyprus Path Clustering for Adaptive Test T. Uezono, T. Takahashi - Tokyo Institute of Technology, M. Shintani , K. Hatayama - Semiconductor Technology Academic Research Center, K. Masu - Tokyo Institute of Technology, H. Ochi, T. Sato - Kyoto University Session 1B: Memory Test & Repair Moderator: P. Prinetto - Politecnico di Torino Automatic Generation of Memory Built-In Self-Repair Circuits in SOCs for Minimizing Test Time and Area Cost T. Tseng, C. Hou, J. Li - National Central University Bit Line Coupling Memory Tests for Single Cell Fails in SRAMs S. Irobi, Z. Al-ars, S. Hamdioui - Delft University of Technology Reducing Test Time and Area Overhead of an Embedded Memory Array Built-In Repair Analyzer with Optimal Repair Rate J. Chung, J. Park - The University of Texas at Austin, E. Byun, C. Woo - Samsung Electronics, J. Abraham - The University of Texas at Austin IP Session 1C: Innovative Practices in RF Test Organizer: R. Parekhji - Texas Instruments Moderator: TBA Test Time Reduction Using Parallel RF Test Techniques R. -

PLM Industry Summary Editor: Christine Bennett Vol

PLM Industry Summary Editor: Christine Bennett Vol. 11 No. 4 Friday 23 January 2009 Contents Acquisitions _______________________________________________________________________ 2 Autodesk Completes Acquisition of ALGOR, Inc. _____________________________________________2 Mentor Graphics Extends High Level Synthesis Leadership with Acquisition of Agility Design Solutions Inc. C Synthesis Suite ____________________________________________________________________3 Company News _____________________________________________________________________ 3 Anark Names Chris Garcia Senior Vice President, Business Development ___________________________3 Autodesk Manufacturing Community to Select 2008 Inventor of the Year Award Winner ______________4 Delcam Offers Free ArtCAM Demo Software for Artistic Users __________________________________5 DP signs Agreement with Italian Lathe Manufacturer GRAZIANO Tortona S.r.l. _____________________6 DP Technology Moves its Midwest Team to a Larger, New and Improved Site _______________________6 DP Technology Signs Agreement with Italian Machine-Tool Builder Salvadeo S.r.l. __________________7 Kalypso and Endeca Announce Partnership in Support of Engineering and PLM-Related Information Visibility Solutions ______________________________________________________________________7 New WorkXPlore 3D Website Allows Engineers to Download High Speed Collaborative CAD Viewer Free _____________________________________________________________________________________8 Si2’s Open Modeling Coalition Releases Document on Statistical -

Case M.8125 - JAC / NEXPERIA

EUROPEAN COMMISSION DG Competition Case M.8125 - JAC / NEXPERIA Only the English text is available and authentic. REGULATION (EC) No 139/2004 MERGER PROCEDURE Article 6(1)(b) NON-OPPOSITION Date: 12/10/2016 In electronic form on the EUR-Lex website under document number 32016M8125 EUROPEAN COMMISSION Brussels, 12.10.2016 C(2016) 6677 final PUBLIC VERSION SIMPLIFIED MERGER PROCEDURE To the notifying parties Dear Sirs, Subject: Case M.8125 - JAC / NEXPERIA Commission decision pursuant to Article 6(1)(b) of Council Regulation (EC) No 139/20041 and Article 57 of the Agreement on the European Economic Area2 1. On 13 September 2016, the European Commission received notification of a proposed concentration pursuant to Article 4 of the Merger Regulation by which the undertaking Beijing Jianguang Asset Management Co., Ltd. ("JAC", People's Republic of China), controlled by the China Investment Corporation (“CIC”, People's Republic of China), acquires within the meaning of Article 3(1)(b) of the Merger Regulation control of the standard products business unit (“Nexperia”) of NXP Semiconductors NV (“NXP”, the Netherlands) by way of purchase of shares.3 2. The business activities of the undertakings concerned are: − JAC is an investment management company which focuses its investments on mergers and acquisitions in the semiconductor industry. It is active in developing, manufacturing, and selling RF power transistors and bipolar based (power) diodes, thyristors and transistors. Its parent company, CIC, is a sovereign wealth fund of the People’s Republic of China, specialized in foreign exchange holdings. − Nexperia is active in the manufacturing and sale of semiconductors, in particular several types of logic integrated circuits ("ICs"), small signal transistors and diodes. -

General Specification

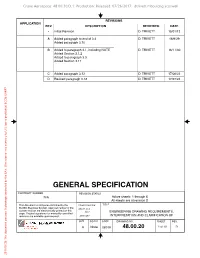

Crane Aerospace: 48.00.20,D,1: Production: Released: 07/26/2017: dtrivett mboulang scaswell REVISIONS APPLICATION REV DESCRIPTION REVIEWED DATE - Initial Revision D. TRIVETT 15/01/12 A Added paragraph to end of 3.4 D. TRIVETT 16/9/29 Added paragraph 3.10 B Added to paragraph 3.1, including NOTE D. TRIVETT 16/11/30 Added Section 3.1.2 Added to paragraph 3.3 Added Section 3.11 C Added paragraph 3.12 D. TRIVETT 17/06/22 D Revised paragragh 3.12 D. TRIVETT 17/07/24 GENERAL SPECIFICATION CONTRACT NUMBER REVISION STATUS N/A Active sheets: 1 through 6 All sheets are at revision D This document is computer-controlled by the TOLERANCES ARE: TITLE ELDEC Business System. Approval names for the LINEAR .XX = current revision are electronically printed on this .XXX = ENGINEERING DRAWING REQUIREMENTS, page. Original signatures for manually-controlled revisions are available upon request. ANGULAR = INTERPRETATION AND CLARIFICATION OF SIZE SCALE CAGE DRAWING NO. SHEET REV. A None 08748 48.00.20 1 of 10 D 2017/07/26 This document contains Technology controlled by the EAR. Diversion or use contrary to U.S. law is prohibited. ECCN: EAR99 Crane Aerospace: 48.00.20,D,1: Production: Released: 07/26/2017: dtrivett mboulang scaswell 1 SCOPE This specification establishes general and specific guidelines to aid in the interpretation and application of engineering drawings defining components, materials, or assemblies, whether purchased from suppliers or fabricated at Crane Aerospace & Electronics facilities. 1.1 Applicability This document applies to engineering drawings controlled by the Lynnwood site of Crane Aerospace & Electronics (CRANE), also referred to as ELDEC Corporation. -

Selective GUIDE to LITERATURE CAN INTEGRATED CIRCUITS

Engineering Literature Guides, Number 18 SELEcTivE GUIDE To LITERATURE CAN INTEGRATED CIRCUITS Compiled 1~y: Nestor L. 0sorio Northern Illinois University Libraries American Society for Engineering Education 1818 N Street, NW, Suite 600 Washington, DC 20036 Copyright (c) 1994 by American Society for Engineering Education 1818 N. Street, N.W., Suite 600 Washington, DC 20036-2479 International Standard Book Number: 0-87823-122-6 Library of Congress Catalog Card Number: Manufactured in the United States of America Beth L. Brin, Series Co-editor Science-Engineering Library University of Arizona Tucson, AZ 85721-001 Godlind Johnson, Series Co-editor Engineering Library SUNY-Stony Brook Stony Brook, NY 11794-2225 ASEE is not responsible for statements made or opinions expressed in this publication. TABLE OF CONTENTS Introduction... ....................................... ..................... .. ..... ............................ .. .. ......1 Bibliographies and Literature Guides . .. .. .. .2 Printed and Electronic Indexes and Abstracts . .3 Encyclopedias. : . .. ..6 Dictionaries . .. .. .. .7 Handbooks and Tables . .. .. .. .. .. .. .8 Directories: Product Information, Trade Catalogs . .. .. .. .10 Standards and Specifications . .. .13 Major Periodicals . .. .. .. .14 Major Proceedings . .. .. : . .. .. 17 Important Books . .. .. .19 Major. Integrated Circuit Manufacturers . .. .. ..20 Appendix: Selected Information Services . .. .. .. ..23 ~I INTRODUCTION ver the last 25 years significant changes have been 0 generated in industry by the