Pin Information for the Intel® Stratix®10 1ST110 Device Version: 2020-10-27

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

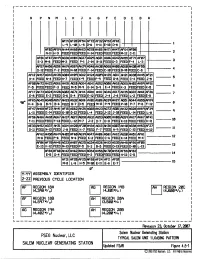

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

PPP Resources for Treasure Coast Businesses

PPP Resources for Treasure Coast Businesses Nine Practical Steps 1. Find the The Laws • H.R. 748 = CARES Act; PPP = Sections 1101, 1102 and 1106 • 1101, 1102 = PPP definition • 1106 = Loan Forgiveness • H.R. 266 = PPP & HCE Act • H.R. 7010 = PPPFA 2. See what the agencies say 3. Google PPP FAQ… 48 as of this writing 4. Keep up with Interim Final Rules CARES Act - PPP Interim Final Rules • Google: 3245-AH34, SBA unless otherwise noted Federal 3245-AH35, 3245-AH36, RIN Register Page Effective Date 1st 3245-AH34 20811 4/15/20 2nd 3245-AH35 20817 4/15/20 etc. 3rd 3245-AH36 21747 4/20/20 4th 3245-AH37 23450 4/28/20 Treasury #1 1505-AC67 23917 4/30/20 AND 5th 3245-AH38 26321 5/4/20 6th 3245-AH39 26324 5/4/20 1505-AC67, 1505-AC69, 7th 3245-AH40 27287 5/8/20 8th 3245-AH41 29845 5/19/20 9th 3245-AH42 29842 5/19/20 etc. 10th 3245-AH43 29847 5/19/20 11th 3245-AH44 30835 5/21/20 12th 3245-AH45 31357 5/26/20 13th 3245-AH46 33004 5/28/20 Treasury #2 1505-AC69 33004 5/28/20 14th 3245-AH47 33010 5/28/20 15th 3245-AH48 pending publication 16th 3245-AH49 17th 3245-AH50 5. UH -OH… “We’re from the IRS and we’re here to help” IRS Notice 2020-32 • PPP says loan forgiveness is tax exempt, but… • Expenses paid by loan forgiveness are NON-DEDUCTIBLE. • Was this the legislative intent? • Congress chose not to address this issue in PPPFA. -

Auction 14A Final Draft.Vp

OUR STAFF Stephen Album Paul Montz Director of Islamic & Early Indian Numismatics Director of World Coins Steve has been serving the Paul joined the staff in January numismatic community since 2011. He attended UC Davis 1960. In 1976 he began dealing from 1975-80, earning bachelor's nearly exclusively in Islamic and and master's degrees in Indian coins. He has authored Agricultural Science & several books including the Management and Agronomy, Catalogue of California Trade respectively. He began working Tokens, Volumes I & II in 1972 in the numismatic field in the and 1974 respectively. 1977 saw 1970's. In 1981, he founded the release of his complete rewrite of Marsden's Olde World Numismatics in Chico, CA, a business he Numismata Orientalia Illustrata, a guide to Islamic ran for 30 years, focusing on A-Z world coins, before and Oriental coins with values. In 1993 he published merging with Stephen Album Rare Coins. He has put A Checklist of Islamic Coins, which now in its second out price lists for many years and has been a fixture edition is the standard for collectors of Islamic coins. at major shows since the 1980's. Paul is a life Mr. Album is currently a senior fellow at the member of the American Numismatic Association Worcester College, Oxford, England, and in this and is a member of other organizations. He has been position has authored three of the ten volumes of the a contributing editor for the Standard Catalog of Sylloge of Islamic Coins in the Ashmolean (Museum) World Coins since 1998. Paul brings experience in beginning in 1999. -

Department of Defense General Services Administration

Friday April 25, 1997 Part XLV Department of Defense General Services Administration National Aeronautics and Space Administration Federal Acquisition Regulation; Semiannual Regulatory Agenda federal register 22581 VerDate 14-MAR-97 10:16 Apr 25, 1997 Jkt 173997 PO 00000 Frm 00001 Fmt 4717 Sfmt 4717 E:\FR\FM\ADV88.043 25ap43 22582 Federal Register / Vol. 62, No. 80 / Friday, April 25, 1997 / Unified Agenda DEPARTMENT OF DEFENSE/GENERAL SERVICES ADMINISTRATION NATIONAL AERONAUTICS AND SPACE ADMINISTRATION (FAR) FAR DEPARTMENT OF DEFENSE being developed by the Civilian Agency estimated and are not commitments to Acquisition Council and the Defense act on or by the dates shown. GENERAL SERVICES Acquisition Regulations Council in ADMINISTRATION compliance with Executive Order 12866 FOR FURTHER INFORMATION CONTACT: Ms. ``Regulatory Planning and Review.'' Beverly Fayson, FAR Secretariat, Room NATIONAL AERONAUTICS AND This agenda is being published to allow 4035, GS Building, Washington, DC SPACE ADMINISTRATION interested persons an opportunity to 20405, (202) 501-4755. participate in the rulemaking process. 48 CFR Ch. 1 SUPPLEMENTARY INFORMATION: DoD, GSA, The Federal Acquisition Regulation and NASA, under their several statutory Semiannual Regulatory Agenda (FAR) Secretariat has attempted to list authorities, jointly issue and maintain all regulations pending at the time of AGENCIES: Department of Defense (DoD), the FAR and prescribe the FAR system. General Services Administration (GSA), publication, except for minor and routine or repetitive actions; however, Revisions to the FAR are made through and National Aeronautics and Space periodic issuance of Federal Acquisition Administration (NASA). unanticipated requirements may result in the issuance of regulations that are Circulars (FACs). ACTION: Semiannual regulatory agenda. -

Growing Together Articulates a Number of Proposals That Can Help the Region Exploit Its Huge Untapped Potential for Regional Economic Integration

i Photo by Warren Field ii FOREWORD For the global economy, these are difficult times. The world is emerging from a crisis whose aftershocks continue to resonate – trapping some of the richest economies in recession and shaking the foundations of one of the world’s major currencies. Here at ESCAP, there are historical echoes. What is now the Economic and Social Commission for Asia and the Pacific was founded more than 60 years ago – also in the aftermath of a global crisis. The countries of Asia and the Pacific established their new Commission partly to assist them in rebuilding their economies as they came out of the yoke of colonialism and the Second World War. The newly established ECAFE, as ESCAP was called then, held a ministerial conference on regional economic cooperation in 1963 that resolved to set up the Asian Development Bank with the aim of assisting the countries in the region in rebuilding their economies. Fifty years later, the Asia-Pacific region is again at a crossroads, on this occasion seeking ways and means to sustain its dynamism in a dramatically changed global context in the aftermath of a global financial and economic crisis. An important change is the fact that, burdened by huge debts and global imbalances, the advanced economies of the West are no longer able to play the role of engines of growth for the Asia-Pacific region that they played in the past. Hence, the Asia-Pacific region has to look for new engines of growth. The secretariat of ESCAP has argued over the past few years that regional developmental challenges, such as poverty and wide disparities in social and physical infrastructure, can be turned into opportunities for sustaining growth in the future. -

1 EAPRS SCORING CODEBOOK Full P1

1 EAPRS SCORING CODEBOOK Full p1, Abbreviated p45, Mini p57 Full scoring Section A1-6 – Paved trails Item Description Scoring Aa13 Trail condition 1=poor 2=fair 3=excellent Aa15 Trail cleanliness 1=not at all 2=somewhat 3=mostly to extremely Saa11 Trail presence 0=no 1=yes Saa62 Trail length, trichotomized and weighted 1= 0-0.5 miles 3=0.6-1 mile 5=1.1-highest Aa14 Trail width 1=<2ft 2=2-5ft 3=>5ft Aa16 Trail flatness 1=significant incline/decline 2=some incline/decline 3=completely flat Aa17 Trail continuity 0=no 1=yes Aa18 Trail clear from obstruction 1=not at all 2=somewhat 3=mostly to extremely Aa19 Trail coverage/shade 1=poor 2=fair 3=excellent Aa110 Trail dividing-line stripe 0=no 1=yes Scorea1, paved Max score 44. Condition and cleanliness multiplied by length, then summed with trail existence width, flatness, continuity, clear, coverage, dividing line. and surface scoresa1=sum(((aa13+aa15)*(saa11*saa62),aa14,aa16,aa17,aa18,aa19,aa110) Aa22 Signage visibility 1=not at all 2=somewhat 2 3=mostly to extremely Aa23 Signage condition 1=poor 2=fair 3=excellent Aa24 Signage content - uses 0=no 1=yes Aa25 Signage content – warnings 0=no 1=yes Aa26 Signage content – distances 0=no 1=yes Aa27 Signage content – trail name 0=no 1=yes Aa28 Signage colorful 0=no 1=yes Aa29 Signage trail map 0=no 1=yes Aa210 Signage distance markings 0=no 1=yes Aa211 Signage convergence 0=no 1=yes Scorea2, paved Sum of above items. -

South Asia Subregional Economic Cooperation Tourism Development Plan

ASIAN DEVELOPMENT BANK AND SOUTH ASIA SUBREGIONAL ECONOMIC COOPERATION TOURISM WORKING GROUP TOURISM RESOURCE CONSULTANTS LTD, NEW ZEALAND IN ASSOCIATION WITH METCON CONSULTANTS PTE LTD, NEPAL December 2004 SOUTH ASIA SUBREGIONAL ECONOMIC COOPERATION Photo Credits: Les Clark Lisa Choegyal Department of Tourism, Bhutan Department of Tourism, India Nepal Tourism Board © 2005 Asian Development Bank All rights reserved. This book was prepared by staff and consultants of the Asian Development Bank (ADB). The analyses and assessments contained herein do not necessarily reflect the views of the Asian Dvelopment Bank, or its Board of Directors, or the governments its members represent. ADB does not guarantee the accuracy of the data included in this publication and accepts no responsibility for any consequences of their use. The term “country,” as used in the context of ADB, refers to a member of ADB and does not imply any view on the part of ADB as to the member’s sovereignty or independent status. Asian Development Bank 6 ADB Avenue, Mandaluyong City 1550 Metro Manila, Philippines Tel (63-2) 632-4444 Fax (63-2) 636-2444 www.adb.org Asian Development Bank. 2004. South Asia Subregional Economic Cooperation Tourism Development Plan Publication Stock No. 111304 ii ABBREVIATIONS ABBREVIATIONS ABTO — Association of Bhutan Tour Operators ACAP — Annapurna Conservation Area Project ADF — Asian Development Fund ACT — Association for Conservation and Tourism ADB — Asian Development Bank ASEAN — Association of South East Asian Nations APETIT — Asia Pacific -

Pub 2424 Fulltext 0.Pdf

ESCAP is the regional development arm of the United Nations and serves as the main economic and social development centre for the United Nations in Asia and the Pacific. Its mandate is to foster cooperation between its 53 members and 9 associate members. ESCAP provides the strategic link between global and country-level programmes and issues. It supports Governments of the region in consolidating regional positions and advocates regional approaches to meeting the region’s unique socio-economic challenges in a globalizing world. The ESCAP office is located in Bangkok, Thailand. Please visit our website at www.unescap.org for further information. The shaded areas of the map indicate ESCAP members and associate members. ECONOMIC AND SOCIAL COMMISSION FOR ASIA AND THE PACIFIC Priority Investment Needs for the Development of the Asian Highway Network United Nations New York, 2006 ST/ESCAP/2424 This publication was prepared under the direction of the Transport and Tourism Division of the Economic and Social Commission for Asia and the Pacific. Inputs related to priority investment needs and projects were provided by national experts and representatives of member countries at three subregional expert group meetings. The designations employed and the presentation of the material in this publication do not imply the expression of any opinion whatsoever on the part of the Secretariat of the United Nations concerning the legal status of any country, territory, city or area, or of its authorities, or the delineation of its frontiers or boundaries. This publication has been issued without formal editing. ii CONTENTS Page INTRODUCTION ................................................................................................................................... 1 I. STATUS OF THE ASIAN HIGHWAY NETWORK ................................................................. -

Natural Capital Approaches for Sustainable Development

Natural Capital Approaches for Sustainable Development Emily McKenzie Chief Adviser, Economics and Sustainability © Anton Vorauer / WWF Outline 1. Natural capital and the SDGs 2. The case of Myanmar 3. What tools are available? 4. Natural capital in business decisions 2 27-Jun-17 1 Natural Capital and the SDGs © BRANDON COLE/WWW.NATUREPL.COM 2 5 27-Jun-17 © Azote Images for Stockholm Resilience Centre 6 What is natural capital? Natural Capital is the stock of renewable and non-renewable natural resources, (e.g. plants, animals, air, water, soils, minerals) that combine to yield a flow of benefits to people Food, fuel, fiber Climate Pollination regulation Coastal Clean protection water Spiritual Fulfilment 7 27-Jun-17 8 Multiple forms of capital Financial capital Manufactured capital Intellectual Human capital capital Social and relationship capital Natural capital <IR> capitals framework 9 10 11 12 13 Millennium Ecosystem Assessment • 60% of ecosystem services are being degraded or used unsustainably • Degradation of ecosystem services causes significant harm to human well-being 14 27-Jun-17 © Christy Williams / WWF Sustainable Securing Sustainable, Standards for Safe, Resilient Development Freshwater Livable Cities the Private Coastal Planning Sector Communities Working together to account for nature’s values, toward shared outcomes THEORY OF CHANGE Robust evidence of Build and tell Create user-friendly conditions for success stories, approaches & tools success engage leaders Get information about natural capital into decisions Make decisions -

Plate Ah Triumph Tr6 Stationary Engine Components Ah5 Ah83 Ah85 Ah84 Ah25 Ah7 Ah26 Ah17 Ah39 Ah75 Ah76 Ah77 Ah40 Ah41 Ah38 Ah78

9 PLATE AH TRIUMPH TR6 STATIONARY ENGINE COMPONENTS AH5 AH83 AH85 AH84 AH25 AH7 AH26 AH17 AH39 AH75 AH76 AH77 AH40 AH41 AH38 AH78 AH36 AH4 AH79 AH9 AH82 AH80 AH73 AH81 AH1 AH13 AH35 AH34 AH32 AH31 AH74 AH15 AH33 AH21 AH72 AH18 AH19 AH14 AH20 AH6 AH11 AH43 AH16 AH22 AH24 AH42 AH69 AH23 AH66 AH48 AH12 AH49 AH50 AH49 AH62 AH63AH65 AH64 AH50 AH8 AH47 AH10 AH46 AH55 AH3 AH56 AH28 AH2 AH68 AH44 AH45 AH27 AH57 AH29 AH53 AH54 AH52 AH67 AH51 AH30 AH61 AH71 AH70 AH58 AH60 AH59 STATIONARY ENGINE COMPONENTS Plate No. Part No. Description No. Off Plate No. Part No. Description No. Off AH1 517611 ENGINE BLOCK ASSEMBLY, fitted up to comm. no. 1 CYLINDER HEAD ATTACHMENT STUDS—Continued CC/CP75000 CYLINDER HEAD ATTACHMENT STUDS, U.S.A., fitted 520880 ENGINE BLOCK ASSEMBLY, fitted from comm. no. 1 from engine no. CC66569 up to CC75000 CC/CP75000 up to CF/CR1 157231 Stud, shorter 12 UKC902 ENGINE BLOCK ASSEMBLY, fitted after comm. no. CF/CR1 1 156274 Stud, longer 2 HARDWARE, securing bearing caps to engine block CYLINDER HEAD ATTACHMENT STUDS, U.S.A., fitted AH2 HB1024 Bolt 8 after engine no. CC75000 AH3 WL210 Washer, lock 8 157231 Stud, shorter 12 CORE PLUGS 156274 Stud, longer 2 AH4 148353 Plug, core, rear of camshaft 1 146200 Stud, cylinder head attachment, non-U.S.A. markets, 14 AH5 144686 Plug, core, rear face and L.H. side of engine block 3 after engine no. CC/CP66569 AH6 144687 Plug, core, front face of block 1 157231 Stud, cylinder head attachment, non-U.S.A. -

I. Introduction to the Asian Highway in Centuries Past, Great Explorers Embarked by Land and Sea in Search of New Worlds And

I. Introduction to the Asian Highway In centuries past, great explorers embarked by land and sea in search of new worlds and riches. Like today, the purpose of travel was to explore new horizons, learn from different cultures, trade, or simply to secure food, shelter and means of subsistence for families and communities. They returned with tales of exotic lands, strange animals and fascinating customs of peoples living in these lands. Today’s modern explorers do not need to sit riveted to their chairs listening to the tales and marvelling at the richness of the cultures. The Asian Highway allows them to experience at first hand the accounts that were relayed by great explorers. In 1959, the Asian Highway project was conceived partially to resurrect those dreams, of trade and travel and to bring the world closer together. In doing so the Asian Highway promotes social progress and better standards of life in larger freedom as laid down in the preamble to the Charter of the United Nations. In the 1960s and 1970s, considerable progress was achieved in identifying a regional road network with active cooperation of member countries. In the late 1980s, the Asia-Pacific region as a whole emerged as a dynamic arena of economic growth. Demand increased for reliable and efficient road transport, which proved to be a versatile and cost-effective mode for moving large numbers of people and goods across borders. In 1992, the United Nations Economic and Social Commission for Asia and the Pacific (ESCAP) endorsed the Asian Land Transport Infrastructure Development (ALTID) project comprising of the Asian Highway and the Trans-Asian Railway network as well as facilitation of land transport.