Ampere® Altra Max™ 64-Bit Multi-Core Arm® Processor Features

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

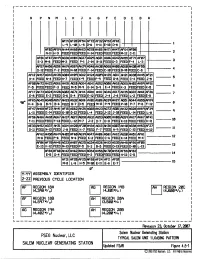

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

Office of Personnel Management (Opm)

Friday April 25, 1997 Part XXXVI Office of Personnel Management Semiannual Regulatory Agenda federal register 22499 VerDate 14-MAR-97 10:08 Apr 25, 1997 Jkt 173997 PO 00000 Frm 00001 Fmt 4717 Sfmt 4717 E:\FR\FM\ADV88.034 25ap34 22500 Federal Register / Vol. 62, No. 80 / Friday, April 25, 1997 / Unified Agenda OFFICE OF PERSONNEL MANAGEMENT (OPM) OPM OFFICE OF PERSONNEL SUMMARY: The following Office of binding obligation on the Office of MANAGEMENT Personnel Management (OPM) Personnel Management with regard to regulations are scheduled for any specific item on the agenda. 5 CFR Ch. I development or review from April 1, Additional regulatory action is not 1997, through March 31, 1998. This precluded. agenda carries out OPM's Semiannual Regulatory Agenda responsibilities to publish a semiannual FOR FURTHER INFORMATION CONTACT: AGENCY: Office of Personnel agenda under E.O. 12866 ``Regulatory Jacquline D. Carter, (202) 606-1973. Management. Planning and Review'' and the Regulatory Flexibility Act (5 U.S.C. Office of Personnel Management. ACTION: Semiannual regulatory agenda. chapter 6). This publication in the James B. King, Federal Register does not impose a Director. Prerule Stage Sequence Regulation Title Identifier Number Number 3646 Availability of Official Information ................................................................................................................................... 3206-AG92 Proposed Rule Stage Regulation Sequence Title Identifier Number Number 3647 Appointment of Noncitizens in the Excepted Service ................................................................................................... -

Information to Users

A quantitative figure-of-merit approach for optimization of an unmanned Mars Sample Return mission Item Type text; Thesis-Reproduction (electronic) Authors Preiss, Bruce Kenneth, 1964- Publisher The University of Arizona. Rights Copyright © is held by the author. Digital access to this material is made possible by the University Libraries, University of Arizona. Further transmission, reproduction or presentation (such as public display or performance) of protected items is prohibited except with permission of the author. Download date 06/10/2021 06:30:51 Link to Item http://hdl.handle.net/10150/278010 INFORMATION TO USERS This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer. The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction. In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion. Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book. -

Athens County Communities

51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 C GM JOHNSON C GM JOHNSON D HILL-BUCHTEL RD y R ODNR RD Sunda 33 W L O CARBON L A L U D O E H R A E B A K OLD A AR 278 DU SW O WATERWORKS HILL RD M C RD A P N K S RD BUCHTEL T-624A R D 13 T-622 D HOCKING COUNTY D KL 78 R Creek N A EY T N 31 E D O DR S T-35 O W HOCKING COUNTY R T N ILLIAMS ST ATHENS COUNTY W S H S U O Y J RD GLOUSTER CEMETERY O Sunday ATHENS COUNTY C J DEW T BUCHTEL UNITED H A 5 O EDWARDS ST CEMETERY S CEMETERY T-315 M 7 H K METHODIST CHURCH R 6 A O M C N I K D R W R R D E E M Y R AMO N D E O E I I CONNER M D o W D W E L E V n N P ST S O T-567 FRANK ST R T BESSEMER RDELM ST S L F d A B L ELM T B S A N T B T RD R K a W LOVE T T O A S y M V r E A S V ANKLI T R N T-675 I F S a 78 Y T-22 A T-1276 T SYCAMORE ST A R O A PINE ST EA T-1276 R n O D T L IETTA c L GROVER DOVER T P 685 h A WHITMORE T-22 S K GROVER ST T Nelsonville LID E AV EUC A D D FAIRVIEWSCOS V GROVE DR ST VERITY ST FR-3 u A V R D - York n COLLEGE ST RD L A O P E d E N I R DOVER VILLAGE OF GLOUSTER a G N CROSS ST y S R E E DR BUCHTEL MOUND R LAN Nelsonville - York H Buchtel MAYOR’S C R W O O D Park DIAMOND O AV r ST U V E Nelsonville Community OFFICE IO E E H T N Park C O D Y 33B BRICK RD R T-22A S R E C W ST D T K TWELFTH ST DR ST BUCK E E S YE WATERLOO r C B BUCHTEL e A D APARTMENTS N EARL ST OAK ST OAK MILL ST Wayne National Forest TRIMBLSYLVANIAE AV BROAD T-1305 U K PINE GROVE PINE H C e C ELIZABETH MT ST MARY DR B ST MARY OF RD T EMBRY ST GLOUSTER FORT ST FORT k ADAMS -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

BELLA COOLA to FOUR MILE TRAIL

BELLA COOLA to FOUR MILE TRAIL Trail Location & Engineering Design Project sponsored by Bella Coola General Hospital Central Coast Regional District & Union of BC Municipalities December 14, 2009 PO Box 216, Hagensborg, BC V0T 1H0 Tel:250-982-2515, [email protected] BC-4Mile Trail Layout Report -i- TABLE OF CONTENTS 1 INTRODUCTION 1 1.1 Layout & Survey Method 1 1.2 Trail Design Criteria 1 2 TRAIL LAYOUT & DESCRIPTION 1 2.1 Cut and Fill 2 2.2 Partial Fill 2 2.3 Overland Fill 3 2.4 Flush Surfacing 3 2.5 Detailed Description 4 2.6 Tatsquan Creek Crossing Options 5 2.6.1 Option A - Hwy 20 Sidewalk 5 2.6.2 Option A2 – Widened Sidewalk on Hwy Bridge 5 2.6.3 Option B – Parallel Footbridge 6 2.6.4 Option C – Downstream Footbridge 7 3 ENVIRONMENT 8 3.1 Fish 8 3.2 Wildlife 8 4 FIELD REVIEW 9 5 CONSTRUCTION 9 5.1 Trail Components 11 5.1.1 Asphalt 11 5.1.2 Crush Gravel 11 5.1.3 Sub-grade Ballast 11 5.1.4 Foot Bridges 11 5.1.5 Culverts 11 5.1.6 Benches 12 5.1.7 Guards 12 5.1.8 Trail Posts 12 5.2 Next Engineering Steps 12 6 TRAIL MAINTENANCE 12 BC-4Mile Trail Layout Report -ii- APPENDIX A – AIRPHOTO MAP OF TRAIL 13 APPENDIX B – SURVEY MAP OF TRAIL 13 APPENDIX C – ENGINEERED PLAN, PROFILE & CROSS SECTIONS 13 Acknowledgement A number of individuals contributed time and knowledge to this initial stage of locating the proposed trail and Frontier Resource Management Ltd is very grateful for this help. -

PPP Resources for Treasure Coast Businesses

PPP Resources for Treasure Coast Businesses Nine Practical Steps 1. Find the The Laws • H.R. 748 = CARES Act; PPP = Sections 1101, 1102 and 1106 • 1101, 1102 = PPP definition • 1106 = Loan Forgiveness • H.R. 266 = PPP & HCE Act • H.R. 7010 = PPPFA 2. See what the agencies say 3. Google PPP FAQ… 48 as of this writing 4. Keep up with Interim Final Rules CARES Act - PPP Interim Final Rules • Google: 3245-AH34, SBA unless otherwise noted Federal 3245-AH35, 3245-AH36, RIN Register Page Effective Date 1st 3245-AH34 20811 4/15/20 2nd 3245-AH35 20817 4/15/20 etc. 3rd 3245-AH36 21747 4/20/20 4th 3245-AH37 23450 4/28/20 Treasury #1 1505-AC67 23917 4/30/20 AND 5th 3245-AH38 26321 5/4/20 6th 3245-AH39 26324 5/4/20 1505-AC67, 1505-AC69, 7th 3245-AH40 27287 5/8/20 8th 3245-AH41 29845 5/19/20 9th 3245-AH42 29842 5/19/20 etc. 10th 3245-AH43 29847 5/19/20 11th 3245-AH44 30835 5/21/20 12th 3245-AH45 31357 5/26/20 13th 3245-AH46 33004 5/28/20 Treasury #2 1505-AC69 33004 5/28/20 14th 3245-AH47 33010 5/28/20 15th 3245-AH48 pending publication 16th 3245-AH49 17th 3245-AH50 5. UH -OH… “We’re from the IRS and we’re here to help” IRS Notice 2020-32 • PPP says loan forgiveness is tax exempt, but… • Expenses paid by loan forgiveness are NON-DEDUCTIBLE. • Was this the legislative intent? • Congress chose not to address this issue in PPPFA. -

Transport Sector Development Strategy (Financed by the ADB Technical Assistance Special Fund)

Technical Assistance Consultant’s Report Project Number: 4061002 November 2008 Armenia: Transport Sector Development Strategy (Financed by the ADB Technical Assistance Special Fund) This consultant’s report does not necessarily reflect the views of ADB or the Government concerned, and ADB and the Government cannot be held liable for its contents. (For project preparatory technical assistance: All the views expressed herein may not be incorporated into the proposed project’s design. Asian Development Bank TA 4973-ARM Ministry of Transport and Communication Republic of Armenia Armenia Transport Sector Development Strategy 2020 Final Report in association with Yerevan, November 2008 Armenia Transport StrategyGeorgia 2020 Georgia Bagratashen Bavra Gogavan AH 81 M 3 AH 82 Dilijian Gyumri Vanadzor Azerbaijan Gavar AH 82 AH 81 Ashtarak Armenia Sevana Lake YEREVAN AH 81 Artashat Turkey AH 82 Yeghegnadzor Capital Goris Airport Azerbaijan Body of Water Road Kapan AH 82 Railroad Agarak International Corridor City Border Point Iran Boundaries are not necessarily authoritative Kilometers 0 25 50 100 Abbreviations and Acronyms AADT annual average daily traffic HWTSK Harral Winner Thompson Sharp Klein ADB Asian Development Bank IATA International Air Transport Association ADR Agreement Concerning the International ICAO International Civil Aviation Organization Carriage of Dangerous Goods by Road IFI international financial institutions AEPLAC Armenian-European Policy and Legal IFRS International Financial Reporting Advice Centre Standards AETR European -

Information to Users

A quantitative figure-of-merit approach for optimization of an unmanned Mars Sample Return mission Item Type text; Thesis-Reproduction (electronic) Authors Preiss, Bruce Kenneth, 1964- Publisher The University of Arizona. Rights Copyright © is held by the author. Digital access to this material is made possible by the University Libraries, University of Arizona. Further transmission, reproduction or presentation (such as public display or performance) of protected items is prohibited except with permission of the author. Download date 11/10/2021 06:15:49 Link to Item http://hdl.handle.net/10150/278010 INFORMATION TO USERS This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer. The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction. In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion. Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book. -

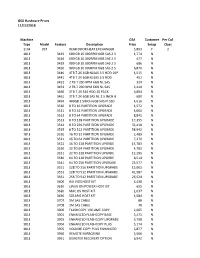

GSA HW Web File As of 11.12.2018.Xlsx

GSA Hardware Prices 11/12/2018 Machine GSA Customer Per Call Type Model Feature Description Price Setup Class 1164 95X REAR DOOR HEAT EXCHANGER 5,893 Y 2 1818 3415 600 GB 10.000RPM 6GB SAS 2.5 4,774 N 1818 3416 600 GB 10.000RPM 6GB SAS 2.5 477 N 1818 3419 900 GB 10.000RPM 6GB SAS 2.5 686 N 1818 3420 900 GB 10 000RPM 6GB SAS 2.5 6,870 N 1818 3440 4TB 7.2K 6GB NLSAS 3.5 HDD 10P 4,515 N 1818 3441 4TB 7.2K 6GB NLSAS 3.5 HDD 451 N 1818 3452 2 TB 7 200 RPM 6GB NL SAS 324 N 1818 3453 2 TB 7 200 RPM 6GB NL SAS 3,249 N 1818 3460 3TB 7.2K SAS HDD 10 PACK 6,804 N 1818 3461 3TB 7.2K 6GB SAS NL 3.5 INCH H 680 N 1818 3494 400GB 2.5INCH 6GB SAS PI SSD 4,616 N 1818 3510 8 TO 16 PARTITION UPGRADE 1,572 N 1818 3511 8 TO 32 PARTITION UPGRADE 4,060 N 1818 3512 8 TO 64 PARTITION UPGRADE 8,841 N 1818 3513 8 TO 128 PARTITION UPGRADE 17,355 N 1818 3514 8 TO 256 PARTITION UPGRADE 32,418 N 1818 3515 8 TO 512 PARTITION UPGRADE 58,942 N 1818 3520 16 TO 32 PARTITION UPGRADE 2,489 N 1818 3521 16 TO 64 PARTITION UPGRADE 7,270 N 1818 3522 16 TO 128 PARTITION UPGRDE 15,783 N 1818 3530 32 TO 64 PARTITION UPGRADE 4,781 N 1818 3531 32 TO 128 PARTITION UPGRDE 13,295 N 1818 3540 64 TO 128 PARTITION UPGRDE 8,514 N 1818 3541 64 TO 256 PARTITION UPGRADE 23,577 N 1818 3551 128 TO 256 PARTITION UPGRADE 15,063 N 1818 3552 128 TO 512 PARTITION UPGRADE 41,587 N 1818 3561 256 TO 512 PARTITION UPGRADE 26,524 N 1818 3600 AIX VIOS HOST KIT 3,438 N 1818 3610 LINUX ON POWER HOST KIT 655 N 1818 3620 MAC OS HOST KIT 1,637 N 1818 3630 SOLARIS HOST KIT 4,584 N 1818 3707 3M SAS CABLE 88 N 1818 -

University of South Florida at Tampa Student Government Statutes

University of South Florida at Tampa Student Government Statutes Statutes updated and certified accurate on 1/10/2018 Page 1 of 171 Pro Tempore Yusef Shafiq, YS Table of Contents Commented [AH1]: New University of South Florida at Tampa Student Government Statutes ................................................... 1 Title 1 System of SG Statutes ................................................................................................................. 5 Chapter 100 Introduction ............................................................................................................................................. 6 Chapter 101 Amendments ............................................................................................................................................ 7 Chapter 102 Symbols ..................................................................................................................................................... 8 Chapter 103 Acronyms and Terms ........................................................................................................................... 10 Title 2 Membership Procedures ...........................................................................................................12 Chapter 200 Membership............................................................................................................................................ 13 Chapter 201 Code of Ethics ...................................................................................................................................... -

Department of Health and Human Services (Hhs)

Monday April 27, 1998 Part VIII Department of Health and Human Services Semiannual Regulatory Agenda federal register 21931 VerDate 09-APR-98 12:32 Apr 21, 1998 Jkt 179005 PO 00000 Frm 00257 Fmt 4717 Sfmt 4717 Y:\SGML\ADV42.006 adv42 21932 Federal Register / Vol. 63, No. 80 / Monday, April 27, 1998 / Unified Agenda DEPARTMENT OF HEALTH AND HUMAN SERVICES (HHS) HHS DEPARTMENT OF HEALTH AND affect areas such as changes in Medicare 7500 Security Boulevard, C5-09-27, HUMAN SERVICES reimbursement rules for graduate Baltimore, Maryland 21244; phone 410- medical education; revisions to payment 786-4473. Office of the Secretary procedures for hospice and home health Food and Drug Administration: Ed services; and solvency standards for 21 CFR Ch. I Dutra, Director, Regulatory Policy and provider-sponsored organizations. Management Staff, 5600 Fishers Lane, 42 CFR Chs. I-V Also, the Health Insurance Portability Rockville, Maryland 20857; phone 301- and Accountability Act of 1996, along 443-3480. with its health insurance reforms, gives 45 CFR Subtitle A, Chs. II, III, and XIII Administration on Children and the Department major new Families: Madeline Mocko, Director, Unified Agenda of Federal Regulatory responsibilities concerning health data Division of Policy and Legislation, 7th and Deregulatory Actions standards and health record privacy. Floor, 370 L'Enfant Promenade SW., These provisions require the Secretary AGENCY: Office of the Secretary, HHS. Washington, DC 20447; phone 202-401- to adopt a series of data standards to 9223. ACTION: Semiannual regulatory agenda. support electronic data interchange for health insurance and related Administration on Aging: David SUMMARY: The President's Executive transactions, such as claims processing Bunoski, Executive Secretariat, Room Order 12866 and the Regulatory and enrollment.