Ampere® Altra® 64-Bit Multi-Core Arm® Processor Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Wir Helfen Dem Sport … 2

Das Klassifizierungssystem der paralympischen Sportarten Bundesinstitut für Sportwissenschaft (BISp) Fachbereich II – Wissenschaftliche Beratung Fachgebiet Sportanlagen und Sportgeräte Graurheindorfer Str. 198 53117 Bonn Tel.: 0 228 99 640 0 Fax: 0 228 99 640 9008 E-Mail: [email protected] Internet: www.bisp.de Stand: Februar 2008 Wir helfen dem Sport … 2 Warum eine Klassifizierung? Die folgenden Kapitel geben eine Übersicht über das Klassifizierungssystem der paralympischen Sportarten wieder. Die vollständigen, aktuellen Klassifizierungen erhalten Sie auf Anfrage bei den jeweiligen Sportfachverbänden des paralympischen Sports oder beim Internationalen Paralympischen Komitee (IPC). Der Zweck der Klassifizierung ist auch diejenigen zur aktiven Teilnahme am Wett- kampfsport zu motivieren, die aufgrund körperlicher Nachteile keine Chance auf eine er- folgreiche Teilnahme hätten. Die Anwendung von Klassifizierungssystemen fasst die Teilnehmer1 einer Sportart in ähn- liche Gruppen zusammen, so dass die Leistungen untereinander vergleichbar sind und sich die Chance vergrößert, gleichwertige und spannende Wettkämpfe zu erleben. In vielen Sportarten versucht man, zumindest die körperbehinderten Sportler funktionell zu klassifizieren, d. h. man achtet auf die Bewegungen, welche die Athleten unterschiedlicher Behinderungsarten gemeinsam haben. So sind bei den Rollstuhldisziplinen beinamputierte oder sogar spastisch gelähmte Sportler den querschnitt- oder poliogelähmten Athleten zugeordnet. Die Klassifizierungen bleiben aber im Behindertensport umstritten. Zu viele Klassen beeinträchtigen die Attraktivität des Sports und so wird weiterhin nach anderen Bewer- tungskriterien gesucht, die die Leistungen untereinander vergleichbar machen. Gab es bei den paralympischen Winterspielen in Salt Lake City 2002 noch 86 Entscheidungen, so waren es in Turin 2006 noch 52 in 5 Sportarten. Das Reglement wurde dahingehend verändert, das möglichst viele Sportler in einem Wettbewerb starten sollen, wobei die Handicapunterschiede durch Zeitgutschriften ausgeglichen werden. -

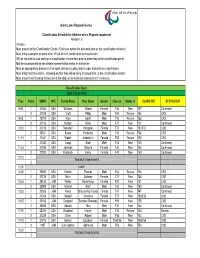

PI Classification Schedule GLRG.Xlsx

Great Lakes Regional Games Classification Schedule for Athletes with a Physical Impairment Version 1.6 Athletes - Must present to the Classification Centre 15 minutes before the allocated time on the classification schedule. Must bring a passport or some other official form of identification to classification. Will be required to read and sign a classification release form prior to presenting to the classification panel. May be accompanied by one athlete representative and/or an interpreter. Must be appropriately dressed in their sport clothes including shorts under tracksuits and sport shoes. Must bring their track chairs, strapping etc that they will be using in competition, to the classification session. Must ensure their throwing frames are at the stadium for technical assessments if necessary. Classification Day 1 Date: 9 June 2016 Time Panel SDMS NPC Family Name First Name Gender Class In Status In CLASS OUT STATUS OUT 9:00 1 31066 USA Williams Taleah Female T46 New T47 Confirmed 2 31008 USA Croft Philip Male T54 Review T54 CRS 9:45 1 15912 USA Rigo Isaiah Male T53 Review T53 CRS 2 31016 USA Nelson Brian Male F37 New F37 Confirmed 10:30 1 31218 USA Beaudoin Margaret Female T37 New T37/F37 CNS 2 30821 USA Evans Frederick Male T34 Review F34 CRS 11:15 1 11241 USA Weber Amberlynn Female T53 Review T53 CRS 2 31330 USA Langi Siale Male F43 New F43 Confirmed 11:45 1 31098 USA Johnson Shayna Female T44 New T44 Confirmed 2 27200 USA Frederick Emily Female F40 New F40 Confirmed 12:15 1 Technical Assessments 2 13:00 Lunch 14:00 1 20880 USA -

Para Athletics Classification Are You, Or Do You Know Someone Who May Be, Interested in Para Athletics?

PARA ATHLETICS CLASSIFICATION ARE YOU, OR DO YOU KNOW SOMEONE WHO MAY BE, INTERESTED IN PARA ATHLETICS? Classification determines who is eligible to compete in a Para sport and then groups the eligible athletes into sport classes according to their activity limitation in a certain sport or event. Athletes are classified as “T” (Track and Jump) or “F” (Field) based on which event they are competing in, followed by a number that represents impairment type and level of impairment. For example, T12. First Letter Represents: First Number Represents: Second Number Represents: T/F TRACK OR FIELD 1-6 IMPAIRMENT TYPE 1-8 DESCRIPTION OF IMPAIRMENT Typically T identifies a track 1 = Visual Impairment The number 1 through 8 specifies event and F for a field event. 2 = Intellectual Impairment the description of the impairment as There are certain exceptions 3 = Co-ordination Impairment per the classification rules (i.e. Long Jump is a T event) 4 = Upper Limb Deficiencies; Lower Limb Deficiencies without the use of prosthetic; short stature 5 = Impaired muscle power or range of movement 6 = Limb deficiencies with the use of prosthetic PHYSICAL IMPAIRMENT SHORT STATURE F40 F41 IMPAIRED MUSCLE POWER AND/OR PASSIVE RANGE OF MOVEMENT T/F51 T/F52 T/F53 T/F54 F55 F56 F57 Athletes who compete seated LIMB DEFICIENCY T/F42 T/F43 T/F44 T/F62 T/F63 T/F64 T/F45 T/F46 T/47 Lower limb deficiency without Lower limb deficiency with Upper limb deficiency the use of a prosthetic the use of a prosthetic with or without the use of a prosthetic ATHLETES WITH ATHETOSIS, ATAXIA AND/OR -

VMAA-Performance-Sta

Revised June 18, 2019 U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent the USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

Android in the Cloud on Arm Native Servers

Android in the Cloud on Arm Native Servers Introduction All the chatter about Arm servers and the role of Android in the cloud in recent years generates questions about what these things could mean for a largely mobile based platform like Arm/Android. This whitepaper examines the practical and commercial use cases that are driving a new paradigm linking the primary mobile and embedded computing platform in the world today with its new cousin in cloud infrastructure: Arm servers + virtualization + native Android execution. While detailing the use cases driving a mobile platform migration to cloud infrastructure, this whitepaper also showcases the solution that Ampere Computing, Canonical, and NETINT Technologies have partnered to produce addressing this migration. The solution is a stellar example of how a service provider or developer can take advantage of Arm native computing in a cloud context to bring together an ecosystem of over 3M primarily mobile apps integrated with benefits from a cloud enabled infrastructure. A case study around cloud gaming fills in the practical real-world considerations of this hot new paradigm. Cloud gaming really showcases the advantages of all the solution components the partners have integrated to make a scalable, efficient cloud resource available to a new class of cloud-native applications catering to the billions of users with Arm based devices worldwide. The whitepaper concludes with thoughts and predictions about the evolution of this new paradigm as hardware and software components mature in the coming years. A New Paradigm The Arm architecture has dominated the mobile processor market with its unrivaled ability to maximize power-efficiency. -

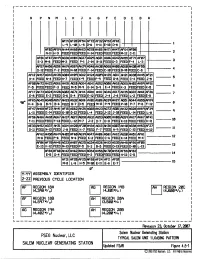

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

ISSCC 2022 INTELLIGENT SILICON for a SUSTAINABLE WORLD February 20-24, 2022 | San Francisco Marriott Marquis | San Francisco, California, USA Plenary Talks

ISSCC 2022 INTELLIGENT SILICON FOR A SUSTAINABLE WORLD February 20-24, 2022 | San Francisco Marriott Marquis | San Francisco, California, USA Plenary Talks ClassicMoore to SysMoore, The Future of the Intelligent Sensing: Power, Energy, High Performance Semiconductor Enabling the Next and the Si Saturation: all we need is a 1000X… Industry and Design “Automation Age” Design What and How? Aart de Geus Renée James Marco Cassis Inyup Kang Founder, Chairman and Founder, Chairman, and CEO, President, Sales, Marketing, Communications President and General Manager of co-Chief Executive Officer, Synopsys Ampere Computing and Strategy Development STMicroelectronics System LSI Business at Samsung Electronics Tutorials Student Activities Analog Circuit Design in Bipolar-CMOS-DMOS (BCD) Technologies Student Research Preview (SRP): Short Presentations w/ Poster Session Marco Berkhout, Goodix Technology, Nijmegen, The Netherlands Silkroad Award: Scholarships awarded for Far-East full-time students Fundamentals of High Frequency DC-DC Converters Kousuke Miyaji, Shinshu University, Nagano, Japan Invited Industry Track Noise-Shaping SAR ADCs Two Invited Industry tracks will highlight recent hot-product releases and discuss innovative ways they solved Yun-Shiang Shu, MediaTek, Hsinchu City, Taiwan product-level challenges. The focus this year is on Digital/ML, Systems and Quantum Computing. Fundamentals of Self-Sensing Processing Systems Special Events Shidhartha Das, Arm, Cambridge, United Kingdom Fundamentals of Process Monitors for Signoff-Oriented Circuit Next Gen Circuit Designer Workshop The Next Gen Circuit Designer Workshop 2022 is an educational workshop for EE undergraduates and early graduate students Design (Master's students/1-2 years of PhD) who are interested in choosing a career in integrated circuit (IC) design. -

Guide for the Use of the International System of Units (SI)

Guide for the Use of the International System of Units (SI) m kg s cd SI mol K A NIST Special Publication 811 2008 Edition Ambler Thompson and Barry N. Taylor NIST Special Publication 811 2008 Edition Guide for the Use of the International System of Units (SI) Ambler Thompson Technology Services and Barry N. Taylor Physics Laboratory National Institute of Standards and Technology Gaithersburg, MD 20899 (Supersedes NIST Special Publication 811, 1995 Edition, April 1995) March 2008 U.S. Department of Commerce Carlos M. Gutierrez, Secretary National Institute of Standards and Technology James M. Turner, Acting Director National Institute of Standards and Technology Special Publication 811, 2008 Edition (Supersedes NIST Special Publication 811, April 1995 Edition) Natl. Inst. Stand. Technol. Spec. Publ. 811, 2008 Ed., 85 pages (March 2008; 2nd printing November 2008) CODEN: NSPUE3 Note on 2nd printing: This 2nd printing dated November 2008 of NIST SP811 corrects a number of minor typographical errors present in the 1st printing dated March 2008. Guide for the Use of the International System of Units (SI) Preface The International System of Units, universally abbreviated SI (from the French Le Système International d’Unités), is the modern metric system of measurement. Long the dominant measurement system used in science, the SI is becoming the dominant measurement system used in international commerce. The Omnibus Trade and Competitiveness Act of August 1988 [Public Law (PL) 100-418] changed the name of the National Bureau of Standards (NBS) to the National Institute of Standards and Technology (NIST) and gave to NIST the added task of helping U.S. -

Topic 0991 Electrochemical Units Electric Current the SI Base

Topic 0991 Electrochemical Units Electric Current The SI base electrical unit is the AMPERE which is that constant electric current which if maintained in two straight parallel conductors of infinite length and of negligible circular cross section and placed a metre apart in a vacuum would produce between these conductors a force equal to 2 x 10-7 newton per metre length. It is interesting to note that definition of the Ampere involves a derived SI unit, the newton. Except in certain specialised applications, electric currents of the order ‘amperes’ are rare. Starter motors in cars require for a short time a current of several amperes. When a current of one ampere passes through a wire about 6.2 x 1018 electrons pass a given point in one second [1,2]. The coulomb (symbol C) is the electric charge which passes through an electrical conductor when an electric current of one A flows for one second. Thus [C] = [A s] (a) Electric Potential In order to pass an electric current thorough an electrical conductor a difference in electric potential must exist across the electrical conductor. If the energy expended by a flow of one ampere for one second equals one Joule the electric potential difference across the electrical conductor is one volt [3]. Electrical Resistance and Conductance If the electric potential difference across an electrical conductor is one volt when the electrical current is one ampere, the electrical resistance is one ohm, symbol Ω [4]. The inverse of electrical resistance , the conductance, is measured using the unit siemens, symbol [S]. -

NVIDIA and Tech Leaders Team to Build GPU-Accelerated Arm Servers for New Era of Diverse HPC Architectures

NVIDIA and Tech Leaders Team to Build GPU-Accelerated Arm Servers for New Era of Diverse HPC Architectures Arm, Ampere, Cray, Fujitsu, HPE, Marvell to Build NVIDIA GPU-Accelerated Servers for Hyperscale-Cloud to Edge, Simulation to AI, High-Performance Storage to Exascale Supercomputing SC19 -- NVIDIA today introduced a reference design platform that enables companies to quickly build GPU-accelerated Arm®-based servers, driving a new era of high performance computing for a growing range of applications in science and industry. Announced by NVIDIA founder and CEO Jensen Huang at the SC19 supercomputing conference, the reference design platform -- consisting of hardware and software building blocks -- responds to growing demand in the HPC community to harness a broader range of CPU architectures. It allows supercomputing centers, hyperscale-cloud operators and enterprises to combine the advantage of NVIDIA's accelerated computing platform with the latest Arm-based server platforms. To build the reference platform, NVIDIA is teaming with Arm and its ecosystem partners -- including Ampere, Fujitsu and Marvell -- to ensure NVIDIA GPUs can work seamlessly with Arm-based processors. The reference platform also benefits from strong collaboration with Cray, a Hewlett Packard Enterprise company, and HPE, two early providers of Arm-based servers. Additionally, a wide range of HPC software companies have used NVIDIA CUDA-X™ libraries to build GPU-enabled management and monitoring tools that run on Arm-based servers. “There is a renaissance in high performance computing,'' Huang said. “Breakthroughs in machine learning and AI are redefining scientific methods and enabling exciting opportunities for new architectures. Bringing NVIDIA GPUs to Arm opens the floodgates for innovators to create systems for growing new applications from hyperscale-cloud to exascale supercomputing and beyond.'' Rene Haas, president of the IP Products Group at Arm, said: “Arm is working with ecosystem partners to deliver unprecedented performance and efficiency for exascale-class Arm-based SoCs. -

A HISTORICAL OVERVIEW of BASIC ELECTRICAL CONCEPTS for FIELD MEASUREMENT TECHNICIANS Part 1 – Basic Electrical Concepts

A HISTORICAL OVERVIEW OF BASIC ELECTRICAL CONCEPTS FOR FIELD MEASUREMENT TECHNICIANS Part 1 – Basic Electrical Concepts Gerry Pickens Atmos Energy 810 Crescent Centre Drive Franklin, TN 37067 The efficient operation and maintenance of electrical and metal. Later, he was able to cause muscular contraction electronic systems utilized in the natural gas industry is by touching the nerve with different metal probes without substantially determined by the technician’s skill in electrical charge. He concluded that the animal tissue applying the basic concepts of electrical circuitry. This contained an innate vital force, which he termed “animal paper will discuss the basic electrical laws, electrical electricity”. In fact, it was Volta’s disagreement with terms and control signals as they apply to natural gas Galvani’s theory of animal electricity that led Volta, in measurement systems. 1800, to build the voltaic pile to prove that electricity did not come from animal tissue but was generated by contact There are four basic electrical laws that will be discussed. of different metals in a moist environment. This process They are: is now known as a galvanic reaction. Ohm’s Law Recently there is a growing dispute over the invention of Kirchhoff’s Voltage Law the battery. It has been suggested that the Bagdad Kirchhoff’s Current Law Battery discovered in 1938 near Bagdad was the first Watts Law battery. The Bagdad battery may have been used by Persians over 2000 years ago for electroplating. To better understand these laws a clear knowledge of the electrical terms referred to by the laws is necessary. Voltage can be referred to as the amount of electrical These terms are: pressure in a circuit. -

Conversions (PDF)

R R x I 2 I VOLTS E x I E P x R WATTSP P AMPSI R E TRANSCAT TECHNICAL REFERENCE E OHMS I P E 2 Conversions Pressures and Densities Electricity Pressure = force 1 ampere = 1 coulomb per second area 1 volt = 1 joule per coulomb 1 column of water 1 foot deep = 62.4 pounds per square foot, or 0.433 pounds per square inch. 1 column of water 1 centimeter Ohm’s Law: Current = potential difference deep = 1 gram per square centimeter. resistance or amperes (I) = volts or E E Specific gravity (liquid) = number of times a substance is as heavy ohms R as an equal body of water, or specific gravity (liquid) = Ampere = electric current weight of liquid Volt = potential difference weight of equal volume of water Ohm = electrical resistance One volt potential difference will drive 1 ampere through a Density = weight resistance of 1 ohm. volume The resistance of conductor can be calculated by Pressure = depth x density, or force per unit area. An increase in the formula: pressure is transmitted equally through the liquid. R = kl (Where l is length, d is diameter, and k is constant) d2 Specific gravity (solid) = The combined resistance of conductors connected in parallel is weight of body 1111 + + weight of equal volume of water Rc = R1 R2 R3 or specific gravity (solid) = 1 watt is the power of a current on 1 ampere when the potential weight of body difference is 1 volt. loss of weight in water To compute electric power: P (power in watts) = V (voltage in volts) One cubic yard of air weighs about 2 pounds.