FET Amplifiers & Amplifier Analysis

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

PH-218 Lec-12: Frequency Response of BJT Amplifiers

Analog & Digital Electronics Course No: PH-218 Lec-12: Frequency Response of BJT Amplifiers Course Instructors: Dr. A. P. VAJPEYI Department of Physics, Indian Institute of Technology Guwahati, India 1 High frequency Response of CE Amplifier At high frequencies, internal transistor junction capacitances do come into play, reducing an amplifier's gain and introducing phase shift as the signal frequency increases. In BJT, C be is the B-E junction capacitance, and C bc is the B-C junction capacitance. (output to input capacitance) At lower frequencies, the internal capacitances have a very high reactance because of their low capacitance value (usually only a few pf) and the low frequency value. Therefore, they look like opens and have no effect on the transistor's performance. As the frequency goes up, the internal capacitive reactance's go down, and at some point they begin to have a significant effect on the transistor's gain. High frequency Response of CE Amplifier When the reactance of C be becomes small enough, a significant amount of the signal voltage is lost due to a voltage-divider effect of the source resistance and the reactance of C be . When the reactance of Cbc becomes small enough, a significant amount of output signal voltage is fed back out of phase with the input (negative feedback), thus effectively reducing the voltage gain. 3 Millers Theorem The Miller effect occurs only in inverting amplifiers –it is the inverting gain that magnifies the feedback capacitance. vin − (−Av in ) iin = = vin 1( + A)× 2π × f ×CF X C Here C F represents C bc vin 1 1 Zin = = = iin 1( + A)× 2π × f ×CF 2π × f ×Cin 1( ) Cin = + A ×CF 4 High frequency Response of CE Amp.: Millers Theorem Miller's theorem is used to simplify the analysis of inverting amplifiers at high-frequencies where the internal transistor capacitances are important. -

Common Drain - Wikipedia, the Free Encyclopedia 10-5-17 下午7:07

Common drain - Wikipedia, the free encyclopedia 10-5-17 下午7:07 Common drain From Wikipedia, the free encyclopedia In electronics, a common-drain amplifier, also known as a source follower, is one of three basic single- stage field effect transistor (FET) amplifier topologies, typically used as a voltage buffer. In this circuit the gate terminal of the transistor serves as the input, the source is the output, and the drain is common to both (input and output), hence its name. The analogous bipolar junction transistor circuit is the common- collector amplifier. In addition, this circuit is used to transform impedances. For example, the Thévenin resistance of a combination of a voltage follower driven by a voltage source with high Thévenin resistance is reduced to only the output resistance of the voltage follower, a small resistance. That resistance reduction makes the combination a more ideal voltage source. Conversely, a voltage follower inserted between a small load resistance and a driving stage presents an infinite load to the driving stage, an advantage in coupling a voltage signal to a small load. Characteristics At low frequencies, the source follower pictured at right has the following small signal characteristics.[1] Voltage gain: Current gain: Input impedance: Basic N-channel JFET source Output impedance: (the parallel notation indicates the impedance follower circuit (neglecting of components A and B that are connected in parallel) biasing details). The variable gm that is not listed in Figure 1 is the transconductance of the device (usually given in units of siemens). References http://en.wikipedia.org/wiki/Common_drain Page 1 of 2 Common drain - Wikipedia, the free encyclopedia 10-5-17 下午7:07 1. -

Cascode Amplifiers by Dennis L. Feucht Two-Transistor Combinations

Cascode Amplifiers by Dennis L. Feucht Two-transistor combinations, such as the Darlington configuration, provide advantages over single-transistor amplifier stages. Another two-transistor combination in the analog designer's circuit library combines a common-emitter (CE) input configuration with a common-base (CB) output. This article presents the design equations for the basic cascode amplifier and then offers other useful variations. (FETs instead of BJTs can also be used to form cascode amplifiers.) Together, the two transistors overcome some of the performance limitations of either the CE or CB configurations. Basic Cascode Stage The basic cascode amplifier consists of an input common-emitter (CE) configuration driving an output common-base (CB), as shown above. The voltage gain is, by the transresistance method, the ratio of the resistance across which the output voltage is developed by the common input-output loop current over the resistance across which the input voltage generates that current, modified by the α current losses in the transistors: v R A = out = −α ⋅α ⋅ L v 1 2 β + + + vin RB /( 1 1) re1 RE where re1 is Q1 dynamic emitter resistance. This gain is identical for a CE amplifier except for the additional α2 loss of Q2. The advantage of the cascode is that when the output resistance, ro, of Q2 is included, the CB incremental output resistance is higher than for the CE. For a bipolar junction transistor (BJT), this may be insignificant at low frequencies. The CB isolates the collector-base capacitance, Cbc (or Cµ of the hybrid-π BJT model), from the input by returning it to a dynamic ground at VB. -

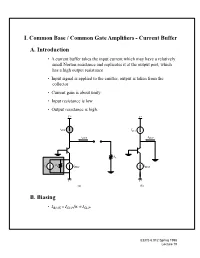

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Dynamic Microphone Amplifier

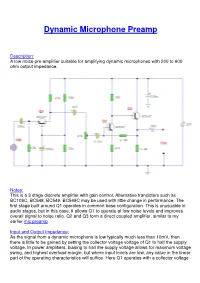

Dynamic Microphone Preamp Description: A low noise pre-amplifier suitable for amplifying dynamic microphones with 200 to 600 ohm output impedance. Notes: This is a 3 stage discrete amplifier with gain control. Alternative transistors such as BC109C, BC548, BC549, BC549C may be used with little change in performance. The first stage built around Q1 operates in common base configuration. This is unusuable in audio stages, but in this case, it allows Q1 to operate at low noise levels and improves overall signal to noise ratio. Q2 and Q3 form a direct coupled amplifier, similar to my earlier mic preamp . Input and Output Impedance: As the signal from a dynamic microphone is low typically much less than 10mV, then there is little to be gained by setting the collector voltage voltage of Q1 to half the supply voltage. In power amplifiers, biasing to half the supply voltage allows for maximum voltage swing, and highest overload margin, but where input levels are low, any value in the linear part of the operating characteristics will suffice. Here Q1 operates with a collector voltage of 2.4V and a low collector current of around 200uA. This low collector current ensures low noise performance and also raises the input impedance of the stage to around 400 ohms. This is a good match for any dynamic microphone having an impedances between 200 and 600 ohms. The output impedance at Q3 is low, the graph of input and output impedance versus frequency is shown below: Gain and Frequency Response: The overall gain of this pre-amplifier is around +39dB or about 90 times. -

JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET Datasheet

JFE150 SLPS732 – JUNE 2021 JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET 1 Features and yields excellent noise performance for currents from 50 μA to 20 mA. When biased at 5 mA, the • Ultra-low noise: device yields 0.8 nV/√Hz of input-referred noise, – Voltage noise: giving ultra-low noise performance with extremely high input impedance (> 1 TΩ). The JFE150 also • 0.8 nV/√Hz at 1 kHz, IDS = 5 mA features integrated diodes connected to separate • 0.9 nV/√Hz at 1 kHz, IDS = 2 mA – Current noise: 1.8 fA/√Hz at 1 kHz clamp nodes to provide protection without the addition • Low gate current: 10 pA (max) of high leakage, nonlinear external diodes. • Low input capacitance: 24 pF at VDS = 5 V The JFE150 can withstand a high drain-to-source • High gate-to-drain and gate-to-source breakdown voltage of 40-V, as well as gate-to-source and gate- voltage: –40 V to-drain voltages down to –40 V. The temperature • High transconductance: 68 mS range is specified from –40°C to +125°C. The device • Packages: Small SC70 and SOT-23 (Preview) is offered in 5-pin SOT-23 and SC-70 packages. 2 Applications Device Information • Microphone inputs PART NUMBER PACKAGE(1) BODY SIZE (NOM) • Hydrophones and marine equipment SOT-23 (5) - Preview 2.90 mm × 1.60 mm JFE150 • DJ controllers, mixers, and other DJ equipment SC-70 (5) 2.00 mm × 1.25 mm • Professional audio mixer or control surface • Guitar amplifier and other music instrument (1) For all available packages, see the package option addendum at the end of the data sheet. -

Notes on BJT & FET Transistors

Phys2303 L.A. Bumm [ver 1.1] Transistors (p1) Notes on BJT & FET Transistors. Comments. The name transistor comes from the phrase “transferring an electrical signal across a resistor.” In this course we will discuss two types of transistors: The Bipolar Junction Transistor (BJT) is an active device. In simple terms, it is a current controlled valve. The base current (IB) controls the collector current (IC). The Field Effect Transistor (FET) is an active device. In simple terms, it is a voltage controlled valve. The gate-source voltage (VGS) controls the drain current (ID). Regions of BJT operation: Cut-off region: The transistor is off. There is no conduction between the collector and the emitter. (IB = 0 therefore IC = 0) Active region: The transistor is on. The collector current is proportional to and controlled by the base current (IC = βIC) and relatively insensitive to VCE. In this region the transistor can be an amplifier. Saturation region: The transistor is on. The collector current varies very little with a change in the base current in the saturation region. The VCE is small, a few tenths of volt. The collector current is strongly dependent on VCE unlike in the active region. It is desirable to operate transistor switches will be in or near the saturation region when in their on state. Rules for Bipolar Junction Transistors (BJTs): • For an npn transistor, the voltage at the collector VC must be greater than the voltage at the emitter VE by at least a few tenths of a volt; otherwise, current will not flow through the collector-emitter junction, no matter what the applied voltage at the base. -

Lecture 19 Common-Gate Stage

4/7/2008 Lecture 19 OUTLINE • Common‐gate stage • Source follower • Reading: Chap. 7.3‐7.4 EE105 Spring 2008 Lecture 19, Slide 1Prof. Wu, UC Berkeley Common‐Gate Stage AvmD= gR • Common‐gate stage is similar to common‐base stage: a rise in input causes a rise in output. So the gain is positive. EE105 Spring 2008 Lecture 19, Slide 2Prof. Wu, UC Berkeley EE105 Fall 2007 1 4/7/2008 Signal Levels in CG Stage • In order to maintain M1 in saturation, the signal swing at Vout cannot fall below Vb‐VTH EE105 Spring 2008 Lecture 19, Slide 3Prof. Wu, UC Berkeley I/O Impedances of CG Stage 1 R = in λ =0 RRout= D gm • The input and output impedances of CG stage are similar to those of CB stage. EE105 Spring 2008 Lecture 19, Slide 4Prof. Wu, UC Berkeley EE105 Fall 2007 2 4/7/2008 CG Stage with Source Resistance 1 g vv= m Xin1 + RS gm 1 vv g AgR==out x m vmD1 vvxin + RS gm R gR ==D mD 1 1+ gRmS + RS gm • When a source resistance is present, the voltage gain is equal to that of a CS stage with degeneration, only positive. EE105 Spring 2008 Lecture 19, Slide 5Prof. Wu, UC Berkeley Generalized CG Behavior Rgout= (1++g mrR O) S r O • When a gate resistance is present it does not affect the gain and I/O impedances since there is no potential drop across it (at low frequencies). • The output impedance of a CG stage with source resistance is identical to that of CS stage with degeneration. -

FJP2145 — ESBC™ Rated NPN Power Transistor MOS- (2) ™ March 2015 FDC655 FJP2145 S C G B Figure 3

FJP2145 — ESBC™ Rated ESBC™ FJP2145 — March 2015 FJP2145 ESBC™ Rated NPN Power Transistor ESBC Features (FDC655 MOSFET) Description NPN Power Transistor (1) The FJP2145 is a low-cost, high-performance power VCS(ON) IC Equiv. RCS(ON) switch designed to provide the best performance when 0.21 V 2 A 0.105 Ω used in an ESBC™ configuration in applications such as: • Low Equivalent On Resistance power supplies, motor drivers, smart grid, or ignition • Very Fast Switch: 150 kHz switches. The power switch is designed to operate up to 1100 volts and up to 5 amps, while providing exception- • Wide RBSOA: Up to 1100 V ally low on-resistance and very low switching losses. •Avalanche Rated ™ • Low Driving Capacitance, No Miller Capacitance The ESBC switch can be driven using off-the-shelf power supply controllers or drivers. The ESBC™ MOS- • Low Switching Losses FET is a low-voltage, low-cost, surface-mount device that • Reliable HV Switch: No False Triggering due to combines low-input capacitance and fast switching. The High dv/dt Transients ESBC™ configuration further minimizes the required driv- ing power because it does not have Miller capacitance. Applications The FJP2145 provides exceptional reliability and a large • High-Voltage, High-Speed Power Switch operating range due to its square reverse-bias-safe-oper- • Emitter-Switched Bipolar/MOSFET Cascode ating-area (RBSOA) and rugged design. The device is (ESBC™) avalanche rated and has no parasitic transistors, so is not prone to static dv/dt failures. • Smart Meters, Smart Breakers, SMPS, HV Industrial Power Supplies The power switch is manufactured using a dedicated • Motor Drivers and Ignition Drivers high-voltage bipolar process and is packaged in a high- voltage TO-220 package. -

Designing a Common-Collector Amplifier

SCHOOL OF ENGINEERING AND APPLIED SCIENCE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING ECE 2115: ENGINEERING ELECTRONICS LABORATORY Tutorial #6: Designing a Common-Collector Amplifier BACKGROUND In the previous lab, you designed a common-emitter (CE) amplifier. Voltage gain (AV) is easy to achieve with this type of amplifier. As you discovered, the input impedance (Rin) of the CE amplifier is moderate- to-high (on the order of a few kΩ). The output impedance (Rout) is high (roughly the value of RC). This makes the common-emitter amplifier a poor choice for “driving” small loads. A common-collector (CC) amplifier typically has a high input impedance (typically in the hundred kΩ range) and a very low output impedance (on the order of 1Ω or 10Ω). This makes the common- collector amplifier excellent for “driving” small loads. As you discovered in Lab 6, the common-collector amplifier has a voltage gain of about 1, or unity gain. The common-collector amplifier is considered a voltage-buffer since the voltage gain is unity. The voltage signal applied at the input will be duplicated at the output; for this reason, the common-collector amplifier is typically called an emitter-follow amplifier. The common-collector amplifier can be thought of as a current amplifier. When the common-emitter amplifier is cascaded to a common-collector amplifier, the CC amplifier can be thought of as an “impedance transformer.” It can take the high output impedance of the CE amplifier and “transform” it to a low output impedance capable of driving small loads. Figure 1 shows a typical configuration for a common-collector amplifier. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ......................................................................................................