4. System Design of the SEAC and DYSEAC

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

DRAM EMAIL GIM Teams!!!/Teaming Issues •Memories in Verilog •Memories on the FPGA

Memories & More •Overview of Memories •External Memories •SRAM (async, sync) •Flash •DRAM EMAIL GIM teams!!!/teaming Issues •Memories in Verilog •Memories on the FPGA 10/18/18 6.111 Fall 2018 1 Memories: a practical primer • The good news: huge selection of technologies • Small & faster vs. large & slower • Every year capacities go up and prices go down • Almost cost competitive with hard disks: high density, fast flash memories • Non-volatile, read/write, no moving parts! (robust, efficient) • The bad news: perennial system bottleneck • Latencies (access time) haven’t kept pace with cycle times • Separate technology from logic, so must communicate between silicon, so physical limitations (# of pins, R’s and C’s and L’s) limit bandwidths • New hopes: capacitive interconnect, 3D IC’s • Likely the limiting factor in cost & performance of many digital systems: designers spend a lot of time figuring out how to keep memories running at peak bandwidth • “It’s the memory - just add more faster memory” 10/18/18 6.111 Fall 2018 2 How do we Electrically Remember Things? • We can convey/transfer information with voltages that change over time • How can we store information in an electrically accessible manner? • Store in either: • Electric Field • Magnetic Field 10/18/18 6.111 Fall 2018 3 Mostly focus on rewritable • Punched Cards have existed as electromechanical program storage since ~1800s • We’re mostly concerned with rewritable storage mechanisms today (cards were true Computer program in punched card format ROMs) https://en.wiKipedia.org/wiKi/Computer_programming_in_the_ -

Early Stored Program Computers

Stored Program Computers Thomas J. Bergin Computing History Museum American University 7/9/2012 1 Early Thoughts about Stored Programming • January 1944 Moore School team thinks of better ways to do things; leverages delay line memories from War research • September 1944 John von Neumann visits project – Goldstine’s meeting at Aberdeen Train Station • October 1944 Army extends the ENIAC contract research on EDVAC stored-program concept • Spring 1945 ENIAC working well • June 1945 First Draft of a Report on the EDVAC 7/9/2012 2 First Draft Report (June 1945) • John von Neumann prepares (?) a report on the EDVAC which identifies how the machine could be programmed (unfinished very rough draft) – academic: publish for the good of science – engineers: patents, patents, patents • von Neumann never repudiates the myth that he wrote it; most members of the ENIAC team contribute ideas; Goldstine note about “bashing” summer7/9/2012 letters together 3 • 1.0 Definitions – The considerations which follow deal with the structure of a very high speed automatic digital computing system, and in particular with its logical control…. – The instructions which govern this operation must be given to the device in absolutely exhaustive detail. They include all numerical information which is required to solve the problem…. – Once these instructions are given to the device, it must be be able to carry them out completely and without any need for further intelligent human intervention…. • 2.0 Main Subdivision of the System – First: since the device is a computor, it will have to perform the elementary operations of arithmetics…. – Second: the logical control of the device is the proper sequencing of its operations (by…a control organ. -

Metal Ultrasonic Delay Lines

Research Paper 2453 rOOmOI of R~eo"h of The NO tiO ~;;:if ~;=asoni;l~~i~;~~~:: Russell W . Mebs, John H. Darr, and John D. Grimsley A study was made of the applicability of a number of metals and a lloys for therm all y stable ultrasonic delay lin es. A preliminary iavestigation was made of different types of pressure holders and ad hesi ves for use in crystal t ransducer attachments and of the iafluence of specimen length on attenuation for valious m etals and alloy. The effect of cold-work, annealing, and specimen cross section on attenuation was a lso determined for a representati ve isoelastic alloy. Measurements of temperature variation of signal attenuation, distort ion, a nd delay t im e on a number of assembled delay lines indicated t hat an isoelastic a lloy employing over cured epoxy-resin crystal attachments gave best over-all t ransmission characteristics. No correlation was obtainable between strength and SOLl nd-transmission characteristics with varioLls cemented joints. 1. Introduction variations in pulse attenuation and distortion with acceleration or change of temperature. The ultrasonic delay line has come into wide use Only a general survey will be given of the basic in recent years with the development of radar, com theory of ultrasonic transmission as related to delay ~uters , and other electronic devices [1 , 2, 3, 4V It lines of 50 tLsec or less. More comprehensive 's a means for delaying a signal for a predetermined treatments have been given elsewhere [2, 4, and 5]. ~hort period to be accurately reproduced for use at _tn appropriate later instant. -

Computer Development at the National Bureau of Standards

Computer Development at the National Bureau of Standards The first fully operational stored-program electronic individual computations could be performed at elec- computer in the United States was built at the National tronic speed, but the instructions (the program) that Bureau of Standards. The Standards Electronic drove these computations could not be modified and Automatic Computer (SEAC) [1] (Fig. 1.) began useful sequenced at the same electronic speed as the computa- computation in May 1950. The stored program was held tions. Other early computers in academia, government, in the machine’s internal memory where the machine and industry, such as Edvac, Ordvac, Illiac I, the Von itself could modify it for successive stages of a compu- Neumann IAS computer, and the IBM 701, would not tation. This made a dramatic increase in the power of begin productive operation until 1952. programming. In 1947, the U.S. Bureau of the Census, in coopera- Although originally intended as an “interim” com- tion with the Departments of the Army and Air Force, puter, SEAC had a productive life of 14 years, with a decided to contract with Eckert and Mauchly, who had profound effect on all U.S. Government computing, the developed the ENIAC, to create a computer that extension of the use of computers into previously would have an internally stored program which unknown applications, and the further development of could be run at electronic speeds. Because of a demon- computing machines in industry and academia. strated competence in designing electronic components, In earlier developments, the possibility of doing the National Bureau of Standards was asked to be electronic computation had been demonstrated by technical monitor of the contract that was issued, Atanasoff at Iowa State University in 1937. -

P the Pioneers and Their Computers

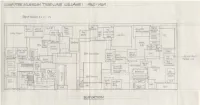

The Videotape Sources: The Pioneers and their Computers • Lectures at The Compp,uter Museum, Marlboro, MA, September 1979-1983 • Goal: Capture data at the source • The first 4: Atanasoff (ABC), Zuse, Hopper (IBM/Harvard), Grosch (IBM), Stibitz (BTL) • Flowers (Colossus) • ENIAC: Eckert, Mauchley, Burks • Wilkes (EDSAC … LEO), Edwards (Manchester), Wilkinson (NPL ACE), Huskey (SWAC), Rajchman (IAS), Forrester (MIT) What did it feel like then? • What were th e comput ers? • Why did their inventors build them? • What materials (technology) did they build from? • What were their speed and memory size specs? • How did they work? • How were they used or programmed? • What were they used for? • What did each contribute to future computing? • What were the by-products? and alumni/ae? The “classic” five boxes of a stored ppgrogram dig ital comp uter Memory M Central Input Output Control I O CC Central Arithmetic CA How was programming done before programming languages and O/Ss? • ENIAC was programmed by routing control pulse cables f ormi ng th e “ program count er” • Clippinger and von Neumann made “function codes” for the tables of ENIAC • Kilburn at Manchester ran the first 17 word program • Wilkes, Wheeler, and Gill wrote the first book on programmiidbBbbIiSiing, reprinted by Babbage Institute Series • Parallel versus Serial • Pre-programming languages and operating systems • Big idea: compatibility for program investment – EDSAC was transferred to Leo – The IAS Computers built at Universities Time Line of First Computers Year 1935 1940 1945 1950 1955 ••••• BTL ---------o o o o Zuse ----------------o Atanasoff ------------------o IBM ASCC,SSEC ------------o-----------o >CPC ENIAC ?--------------o EDVAC s------------------o UNIVAC I IAS --?s------------o Colossus -------?---?----o Manchester ?--------o ?>Ferranti EDSAC ?-----------o ?>Leo ACE ?--------------o ?>DEUCE Whirl wi nd SEAC & SWAC ENIAC Project Time Line & Descendants IBM 701, Philco S2000, ERA.. -

History Timeline by Jeff Drobman (C) 2015 === 1889 - Punch Cards - Herman Hollerith (Of IBM Forerunner) Invented "IBM" Punch Cards to Be Used for the 1890 Census

Computer Memory History Timeline by Jeff Drobman (C) 2015 === 1889 - Punch cards - Herman Hollerith (of IBM forerunner) invented "IBM" punch cards to be used for the 1890 census. 1932 - Drum memory 1947 - Delay line memory 1949 - Magnetic CORE memory 1950 - Magnetic TAPE memory 1955 - Magnetic DISK memory - IBM RAMAC was first one 1957 - Plated wire memory 1962 - Thin film memory 1968 (ca) - Paper tape - Had beginnings dating back to 1846, but became widely used with teletype machines such as the Teletype Model 33 ASR, which were adopted early on by minicomputers as a primitive terminal. 1970 - Bubble memory 1970 - DRAM - Invented by Intel, first device was the 1101, organized as 256x1, followed by the 4x larger (1024x1) 1103(A) -- regarded as the world's first commercial DRAM (intro in October 1970). 1971 - Bipolar SRAM - Fairchild 256x1 (note IBM made a 16-bit SRAM in late 1960s. AMD made a second source of a 64x1 SRAM by Fairchild in 1971.) 1971 - EPROM - Invented by Dov Frohman of Intel as the i1702, a 2K-bit (256x8) EPROM. 1971 - "Floppy" disks -- First were 8-inch, hence very flexible ("floppy"). The 8" became commercially available in 1971. 1973 (ca) - Magnetic TAPE CASSETTE memory 1976 - Shugart Associates introduced the first 5¼-inch floppy (flexible) disk drive 1977 - EEPROM - invented by Eli Harari at Hughes - a BYTE erasable device 1979 - CMOS SRAM (static RAM, 4T/6T cell, implemented as a latch) - first introduced by HP then its spinoff as Integrated Device Technology. I believe first devices were 1K (1024x1), and later organized as x4 then x8. -

The Graphic Display of Computer Memory Data

University of Windsor Scholarship at UWindsor Electronic Theses and Dissertations Theses, Dissertations, and Major Papers 7-21-1969 The graphic display of computer memory data. Satish P. Agrawal University of Windsor Follow this and additional works at: https://scholar.uwindsor.ca/etd Recommended Citation Agrawal, Satish P., "The graphic display of computer memory data." (1969). Electronic Theses and Dissertations. 6548. https://scholar.uwindsor.ca/etd/6548 This online database contains the full-text of PhD dissertations and Masters’ theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email ([email protected]) or by telephone at 519-253-3000ext. 3208. INFORMATION TO USERS This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer. The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction. -

A Large Routine

A large routine Freek Wiedijk It is not widely known, but already in June 1949∗ Alan Turing had the main concepts that still are the basis for the best approach to program verification known today (and for which Tony Hoare developed a logic in 1969). In his three page paper Checking a large routine, Turing describes how to verify the correctness of a program that calculates the factorial function by repeated additions. He both shows how to use invariants to establish the correctness of this program, as well as how to use a variant to establish termination. In the paper the program is only presented as a flow chart. A modern C rendering is: int fac (int n) { int s, r, u, v; for (u = r = 1; v = u, r < n; r++) for (s = 1; u += v, s++ < r; ) ; return u; } Turing's paper seems not to have been properly appreciated at the time. At the EDSAC conference where Turing presented the paper, Douglas Hartree criticized that the correctness proof sketched by Turing should not be called inductive. From a modern point of view this is clearly absurd. Marc Schoolderman first told me about this paper (and in his master's thesis used the modern Why3 tool of Jean-Christophe Filli^atreto make Turing's paper fully precise; he also wrote the above C version of Turing's program). He then challenged me to speculate what specific computer Turing had in mind in the paper, and what the actual program for that computer might have been. My answer is that the `EPICAC'y of this paper probably was the Manchester Mark 1. -

Pioneercomputertimeline2.Pdf

Memory Size versus Computation Speed for various calculators and computers , IBM,ZQ90 . 11J A~len · W •• EDVAC lAS• ,---.. SEAC • Whirlwind ~ , • ENIAC SWAC /# / Harvard.' ~\ EDSAC Pilot• •• • ; Mc;rk I " • ACE I • •, ABC Manchester MKI • • ! • Z3 (fl. pt.) 1.000 , , .ENIAC •, Ier.n I i • • \ I •, BTL I (complexV • 100 ~ . # '-------" Comptometer • Ir.ne l ' with constants 10 0.1 1.0 10 100 lK 10K lOOK 1M GENERATIONS: II] = electronic-vacuum tube [!!!] = manual [1] = transistor Ime I = mechanical [1] = integrated circuit Iem I = electromechanical [I] = large scale integrated circuit CONTENTS THE COMPUTER MUSEUM BOARD OF DIRECTORS The Computer Museum is a non-profit. Kenneth H. Olsen. Chairman public. charitable foundation dedicated to Digital Equipment Corporation preserving and exhibiting an industry-wide. broad-based collection of the history of in Charles W Bachman formation processing. Computer history is Cullinane Database Systems A Compcmion to the Pioneer interpreted through exhibits. publications. Computer Timeline videotapes. lectures. educational programs. C. Gordon Bell and other programs. The Museum archives Digital Equipment Corporation I Introduction both artifacts and documentation and Gwen Bell makes the materials available for The Computer Museum 2 Bell Telephone Laboratories scholarly use. Harvey D. Cragon Modell Complex Calculator The Computer Museum is open to the public Texas Instruments Sunday through Friday from 1:00 to 6:00 pm. 3 Zuse Zl, Z3 There is no charge for admission. The Robert Everett 4 ABC. Atanasoff Berry Computer Museum's lecture hall and rece ption The Mitre Corporation facilities are available for rent on a mM ASCC (Harvard Mark I) prearranged basis. For information call C. -

Computer Conservation Society

Issue Number 76 Winter 2016/7 Computer Conservation Society Aims and objectives The Computer Conservation Society (CCS) is a co-operative venture between BCS, The Chartered Institute for IT; the Science Museum of London; and the Museum of Science and Industry (MSI) in Manchester. The CCS was constituted in September 1989 as a Specialist Group of the British Computer Society. It is thus covered by the Royal Charter and charitable status of BCS. The aims of the CCS are: To promote the conservation of historic computers and to identify existing computers which may need to be archived in the future, To develop awareness of the importance of historic computers, To develop expertise in the conservation and restoration of historic computers, To represent the interests of Computer Conservation Society members with other bodies, To promote the study of historic computers, their use and the history of the computer industry, To publish information of relevance to these objectives for the information of Computer Conservation Society members and the wider public. Membership is open to anyone interested in computer conservation and the history of computing. The CCS is funded and supported by voluntary subscriptions from members, a grant from BCS, fees from corporate membership, donations and by the free use of the facilities of our founding museums. Some charges may be made for publications and attendance at seminars and conferences. There are a number of active projects on specific computer restorations and early computer technologies and software. Younger people are especially encouraged to take part in order to achieve skills transfer. The CCS also enjoys a close relationship with the National Museum of Computing. -

Random Access Memory (RAM)

P-2 Digital Design & Applications Semiconductor Memory (Unit-V) By: A K Verma SOS in Electronics & Photonics Pt. Ravishankar Shukla University, Raipur (C.G.) 1 What is Memory? • In computing, memory refers to the physical devices used to store programs (sequences of instructions) or data (e.g. program state information) on a temporary or permanent basis for use in a computer or other digital electronic device. The term primary memory is used for the information in physical systems which function at high-speed (i.e. RAM), as a distinction from secondary memory, which are physical devices for program and data storage which are slow to access but offer higher memory capacity. If needed, primary memory can be stored in secondary memory, through a memory management technique called "virtual memory“.[1] 2 History • In the early 1940s, memory technology mostly permitted a capacity of a few bytes. The first electronic programmable digital computer, the ENIAC, using thousands of octal-base radio vacuum tubes, could perform simple calculations involving 20 numbers of ten decimal digits which were held in the vacuum tube accumulators. • The next significant advance in computer memory came with acoustic delay line memory, developed by J. Presper Eckert in the early 1940s. Through the construction of a glass tube filled with mercury and plugged at each end with a quartz crystal, delay lines could store bits of information within the quartz and transfer it through sound waves propagating through mercury. Delay line memory would be limited to a capacity of up to a few hundred thousand bits to remain efficient. -

Optical RAM and Integrated Optical Memories: a Survey

Alexoudi, T. , Kanellos, G. T., & Pleros, N. (2020). Optical RAM and integrated optical memories: a survey. Light, science & applications, 9, 91. https://doi.org/10.1038/s41377-020-0325-9 Publisher's PDF, also known as Version of record License (if available): CC BY Link to published version (if available): 10.1038/s41377-020-0325-9 Link to publication record in Explore Bristol Research PDF-document This is the final published version of the article (version of record). It first appeared online via Nature at https://doi.org/10.1038/s41377-020-0325-9 . Please refer to any applicable terms of use of the publisher. University of Bristol - Explore Bristol Research General rights This document is made available in accordance with publisher policies. Please cite only the published version using the reference above. Full terms of use are available: http://www.bristol.ac.uk/red/research-policy/pure/user-guides/ebr-terms/ Alexoudi et al. Light: Science & Applications (2020) 9:91 Official journal of the CIOMP 2047-7538 https://doi.org/10.1038/s41377-020-0325-9 www.nature.com/lsa REVIEW ARTICLE Open Access Optical RAM and integrated optical memories: a survey Theoni Alexoudi1, George Theodore Kanellos2 and Nikos Pleros1 Abstract The remarkable achievements in the area of integrated optical memories and optical random access memories (RAMs) together with the rapid adoption of optical interconnects in the Datacom and Computercom industries introduce a new perspective for information storage directly in the optical domain, enabling fast access times, increased bandwidth and transparent cooperation with optical interconnect lines. This article reviews state-of-the-art integrated optical memory technologies and optical RAM cell demonstrations describing the physical mechanisms of several key devices along with their performance metrics in terms of their energy, speed and footprint.